## The University of Alabama in Huntsville Electrical and Computer Engineering Department CPE 221 01 Test 2 November 14, 2019

This test is closed book, closed notes. You may use a calculator. You should have the 6 page ARM Instruction Reference. Please check to make sure you have all 6 pages of the test. You must show your work to receive full credit.

Name: \_\_\_\_\_

1. (2 points) List the RTL for POP instruction \_\_\_\_\_

- 2. (1 point) The stack pointer always points to the \_\_\_\_\_ of the stack.

- 3. (1 point) \_\_\_\_\_\_ is a technique in which the execution of multiple instructions are overlapped to increase the number of instructions executed in a period of time.

- 4. (1 point) True/False \_\_\_\_\_ The stack pointer can change during the execution of a procedure.

- 5. (8 points) A processor executes an instruction in the following five stages. The time required by each stage in picoseconds (1,000 ps = 1 ns) is:

- F Fetch 170 ps

- O Decode/Read Operands 120 ps

- E Execute 250 ps

- M Memory 380 ps

- WB Result Writeback to Register 120 ps

- a. (4 points) What is the time taken to fully execute an instruction assuming that this structure is pipelined in five stages and that there is an additional 10 ps per stage due to the pipeline latches?

b. (4 points) What is the time to execute an instruction if the processor is not pipelined?

6. (20 points) Write the code to implement the expression A = (B - C)/(D+(E+F)/G) on 3-, 2-, 1-, and 0-address machines. Do not rearrange the expression. In accordance with programming language practice, computing the expression should not change the values of its operands. When using a 0-address machine, the order used is SOS op TOS, where SOS is second on stack and TOS is top of stack.

7. (30 points) Complete the ARM assembly language program below so that it implements the following C++ statements. Create a subroutine cube that expects the input parameter to be in register r8 and returns the result in register r9. There is no need to use the stack.

```

;

This program calculates the cube of each of the elements of an

;

array using a subroutine and stores them in another array.

;

int cube(int);

;

;

void main(void)

{

;

const int size = 10;

;

int x[size] = {100, 3, -1, 2, 4, 4, 2, -1, 3, 100};

;

int z[size];

;

int i;

;

for (i = 0; i < size; i++)

;

{

;

z[i] = cube(x[i]);

;

}

;

int cube(int val)

;

;

{

int i, result;

;

result = 1

;

for (i = 0; i < 3; i++)

;

result = result * val;

;

return result;

;

}

;

```

```

AREA PROB_8, CODE, READ

ENTRY

ADR r0, x

ADR r2, z

LDR r3, size

LDR r4, i

```

| done | В     | done |    |     |    |    |    |    |     |    |     |  |

|------|-------|------|----|-----|----|----|----|----|-----|----|-----|--|

| х    | DCD   | 100, | З, | -1, | 2, | 4, | 4, | 2, | -1, | З, | 100 |  |

| Z    | SPACE | 40   |    |     |    |    |    |    |     |    |     |  |

| i    | DCD   | 0    |    |     |    |    |    |    |     |    |     |  |

| size | DCD   | 10   |    |     |    |    |    |    |     |    |     |  |

|      | END   |      |    |     |    |    |    |    |     |    |     |  |

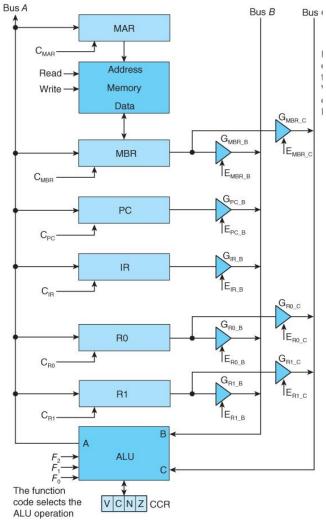

8. (15 points) For the architecture shown, write the sequence of signals and control actions necessary to execute the instruction SUB R1, R1, R0, that stores R1 − R0 in R1 The actions of this instruction are described by the abstract RTL R1 ← R1 − R0.

| $F_2$ | $F_1$ | F <sub>0</sub> | Operation |

|-------|-------|----------------|-----------|

| 0     | 0     | 0              | A = B'    |

| 0     | 0     | 1              | A = C     |

| 0     | 1     | 0              | A = B + 1 |

| 0     | 1     | 1              | A = B + C |

| 1     | 0     | 0              | A = C     |

| 1     | 0     | 1              | A = C     |

| 1     | 1     | 0              | A = C     |

| 1     | 1     | 1              | A = C     |

| Cycle | Concrete RTL | Signals |

|-------|--------------|---------|

| 1     |              |         |

| 2     |              |         |

| 3     |              |         |

| 4     |              |         |

| 5     |              |         |

| 6     |              |         |

| 7     |              |         |

| 8     |              |         |

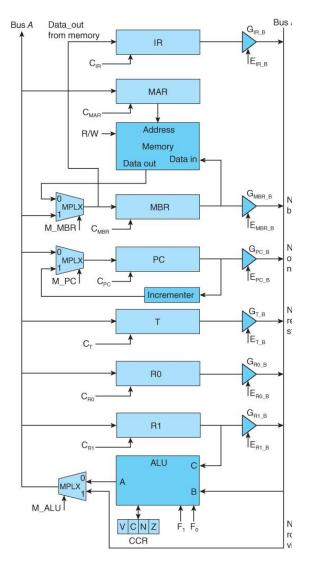

9. (7 points) For the architecture shown, write the sequence of signals and control actions necessary to implement the fetch cycle.

| Cycle | Concrete RTL | Signals |

|-------|--------------|---------|

| 1     |              |         |

| 2     |              |         |

| 3     |              |         |

| 4     |              |         |

10. (15 points) A RISC processor executes the following code. There are data dependencies but no internal forwarding. A source operand cannot be used until it has been written. Assume that the first instruction begins executing in the first cycle.

a. (5 points) Assuming a four-stage pipeline (fetch (IF), operand fetch (OF), execute (E), operand write (W)), what registers are being read during the seventh clock cycle and what register is being written?

|                | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 |

|----------------|---|---|---|---|---|---|---|---|---|----|----|----|----|

| MUL r0, r1, r2 |   |   |   |   |   |   |   |   |   |    |    |    |    |

| ADD r3, r1, r0 |   |   |   |   |   |   |   |   |   |    |    |    |    |

| LDR r1, [r2]   |   |   |   |   |   |   |   |   |   |    |    |    |    |

| ADD r3, r3, r6 |   |   |   |   |   |   |   |   |   |    |    |    |    |

| ADD r6, r0, r7 |   |   |   |   |   |   |   |   |   |    |    |    |    |

| STR r3, [r6]   |   |   |   |   |   |   |   |   |   |    |    |    |    |

b. (10 points) Assuming a six-stage pipeline: fetch (F), register read (O), execute (E), memory read (MR), memory write (MW), register write (WB), how long will it take to execute the entire sequence?

|                | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

|----------------|---|---|---|---|---|---|---|---|---|----|----|

| MUL r0, r1, r2 |   |   |   |   |   |   |   |   |   |    |    |

| ADD r3, r1, r0 |   |   |   |   |   |   |   |   |   |    |    |

| LDR r1, [r2]   |   |   |   |   |   |   |   |   |   |    |    |

| ADD r3, r3, r6 |   |   |   |   |   |   |   |   |   |    |    |

| ADD r6, r0, r7 |   |   |   |   |   |   |   |   |   |    |    |

| STR r3, [r1]   |   |   |   |   |   |   |   |   |   |    |    |

|                | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 |

|----------------|----|----|----|----|----|----|----|----|----|----|----|

| MUL r0, r1, r2 |    |    |    |    |    |    |    |    |    |    |    |

| ADD r3, r1, r0 |    |    |    |    |    |    |    |    |    |    |    |

| LDR r1, [r2]   |    |    |    |    |    |    |    |    |    |    |    |

| ADD r3, r3, r6 |    |    |    |    |    |    |    |    |    |    |    |

| ADD r6, r0, r7 |    |    |    |    |    |    |    |    |    |    |    |

| STR r3, [r1]   |    |    |    |    |    |    |    |    |    |    |    |