# Department of Electrical and Computer Engineering University of Alabama in Huntsville

# EE/CPE 421/521 – Microcomputers Test II Solutions

Instructor: Dr. Aleksandar Milenkovic

Date: February 19, 2004

Place: EB 240

Time: 5:30 PM - 6:50 PM

**Note:** Work should be performed systematically and neatly. This exam is closed books and closed neighbour(s). Allowable items include exam, pencils, straight edge, calculator, and materials distributed by the instructor. Best wishes.

| Question | Points | Score |

|----------|--------|-------|

| 1        | 35     |       |

| 2        | 50     |       |

| 3        | 20     |       |

|          |        |       |

| Sum      | 105    |       |

| Please print in | capitals: |  |

|-----------------|-----------|--|

| Last name:_     |           |  |

| First name:     |           |  |

**1.** (**35 points**) Microcontroller system is using 32KHz crystal connected to LFXT1 Oscillator, 8MHz crystal connected to XT2 Oscillator, and 3V power supply. See **Appendix** (**pages 7-11**) for necessary information.

Datasheet specifications:

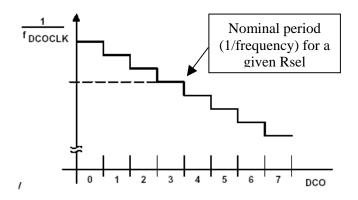

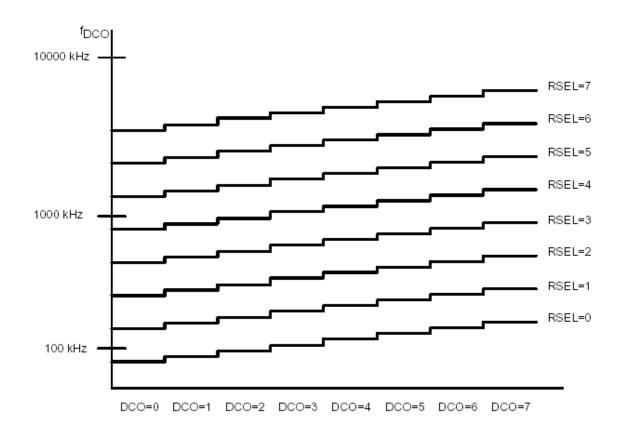

$$\begin{split} f_{Rsel+1} \, / \, f_{Rsel} &= 1.65, \\ f_{DCO+1} \, / \, f_{DCO} &= 1.12, \\ DCOR: \, use \, internal \, R_{osc} \end{split}$$

# Set the following modes of operation (If the bit can be either 0 or 1, put X):

a) (10 points) processor clock (MCLK) to 8MHz, ACLK to 8KHz, SMCLK to 750 KHz.

| _             |        |        |        |        |       |        |        |       |

|---------------|--------|--------|--------|--------|-------|--------|--------|-------|

| BCSCTL1: 0x24 | 0      | 0      | 1      | 0      | 0     | 1      | 0      | 0     |

|               | XT2Off | XTS    | DIVA.1 | DIVA.0 | XT5V  | Rsel2  | Rsel1  | Rsel0 |

| BCSCTL2: 0x80 | 1      | 0      | 0      | 0      | 0     | 0      | 0      | 0     |

| _             | SELM.1 | SELM.0 | DIVM.1 | DIVM.0 | SELS  | DIVS.1 | DIVS.0 | DCOR  |

| DCOCTL: 0x60  | 0      | 1      | 1      | 0      | 0     | 0      | 0      | 0     |

|               | DCO.2  | DCO.1  | DCO.0  | MOD.4  | MOD.3 | MOD.2  | MOD.1  | MOD.0 |

b) (10 points) processor clock to 840KHz, SMCLK to 420KHz, and ACLK to 32KHz.

| BCSCTL1: 0x84 | 1      | 0      | 0      | 0      | 0     | 1      | 0      | 0     |

|---------------|--------|--------|--------|--------|-------|--------|--------|-------|

|               | XT2Off | XTS    | DIVA.1 | DIVA.0 | XT5V  | Rsel2  | Rsel1  | Rsel0 |

| BCSCTL2: 0x02 | 0      | 0      | 0      | 0      | 0     | 0      | 1      | 0     |

| ·             | SELM.1 | SELM.0 | DIVM.1 | DIVM.0 | SELS  | DIVS.1 | DIVS.0 | DCOR  |

| DCOCTL: 0x80  | 1      | 0      | 0      | 0      | 0     | 0      | 0      | 0     |

| ·             | DCO.2  | DCO.1  | DCO.0  | MOD.4  | MOD.3 | MOD.2  | MOD.1  | MOD.0 |

c) (15 points) What should be the value of MOD if MCLK needs to be set to **1.5MHz** for the system that doesn't use external oscillators (uses only DCO)? Give values for Rsel, DCO, and MOD. Show how you came up with the result. [*Hint*: use the formula T=((32-MOD)\*TDCO + MOD\*TDCO+1)/32]

```

\begin{split} f_{DCO53} &= 1.3 MHz => f_{DCO54} = f_{DCO53} * 1.12 = 1.456 MHz \text{ and } f_{DCO55} = f_{DCO54} * 1.12 = 1.631 MHz \\ &=> T_{DCO} = 1/f_{DCO54} = 0.687 e^{-6} \text{ and } T_{DCO+1} = 1/f_{DCO55} = 0.613 e^{-6} \text{ and } T = 1/f = 1/1.5 MHz = 0.667 e^{-6} \\ 0.667 &= ((32 - MOD) * 0.687 + MOD * 0.613)/32 \\ MOD &= 8.83 \approx 9 \end{split}

```

Answer: Rsel = 5; DCO = 4; MOD = 9

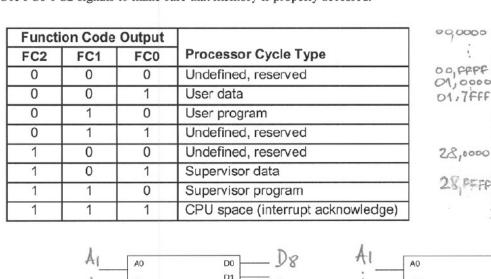

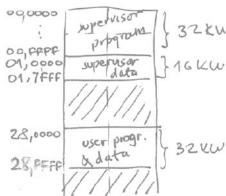

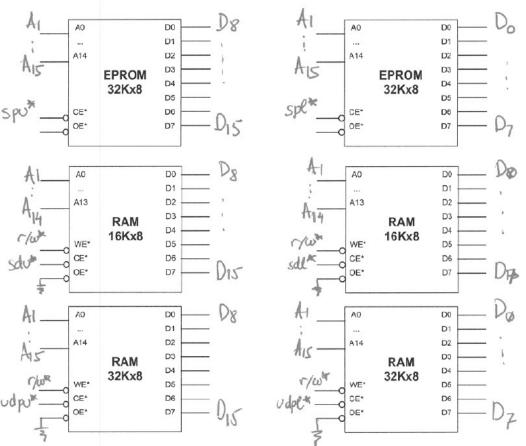

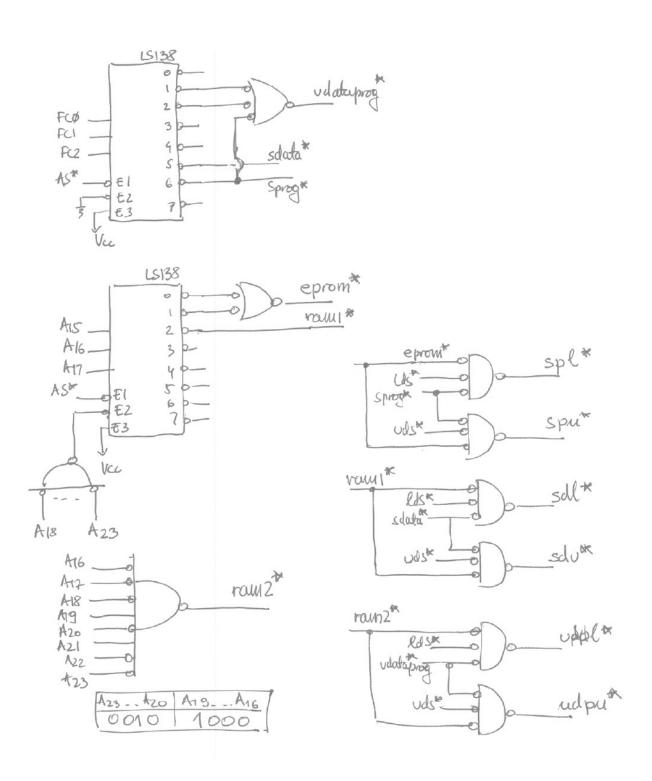

- **2.** (50 points) Using given memory components, design a memory subsystem for an MC68000-based microcomputer system with following characteristics:

- a. 64 KB of supervisor program memory (EPROM) residing at address \$00 0000

- b. 32 KB of supervisor data memory (RAM) residing in the consecutive address window, and

- c. 64 KB of user program/data memory (RAM) beginning at the address \$28 0000.

Use LS138 decoders (3 to 8) plus any other logic gates for address decoding, and generate:

- Address decoding signals (CS\*)

- Control signals (WE\*, OE\*)

Use FC0-FC2 signals to make sure that memory is properly accessed.

- **3.** (20 points) Microcontroller system operates with system frequency of 100 Hz (repeat the following sequence: a/d conversion, process data, real-time clock, idle). What is the expected system operation time for the system if the system is supplied with 720mAh capacity battery? Power consumption of different components is:

- Analog interface circuit 2 mA, cycle operation time 100 μs.

- Microcontroller in active mode 400 μA, cycle processing time:

- 40 µs with probability 20%

- 80 µs with probability 50%

- 120 μs with probability 30%

- Microcontroller in idle mode 1.6 μA.

- Real Time Clock 350 μA, cycle operation time 100 μs.

- LCD display 20 μA, always active.

#### Solution:

System clock frequency fs =  $100 \text{ Hz} \rightarrow \text{cycle time T} = 10 \text{ ms}$ .

Average microcontroller cycle activity

$$T_a = 0.2*40 \ \mu s + 0.5*80 \ \mu s + 0.3*120 \ \mu s = 84 \ \mu s$$

```

\begin{split} I_{avg} &= 2mA*100~\mu\text{s/T} & \text{(analog interface circuit)} \\ &+ 400~\mu\text{A}*T_a/T + & \text{(microcontroller - active mode)} \\ &+ 1.6~\mu\text{A}*(T-T_a)/T & \text{(microcontroller - idle mode)} \\ &+ 350~\mu\text{A}*100~\mu\text{s}/T & \text{(RTC)} \\ &+ 20~\mu\text{A} & \text{(LCD)} \end{split}

```

$$I_{avg} = 20 \ \mu A + 3.36 \ \mu A + 1.58656 \ \mu A + 3.5 \ \mu A + 20 \ \mu A = 48.44656 \ \mu A$$

Expected operation time OT = 720 mAh /  $48.44656 \mu A \approx 14862$  or 619 days

# **Appendix**

| PARAMETER | TEST CONDITIONS                                                               |                             | MIN             | NOM                        | MAX                        | UNIT   |

|-----------|-------------------------------------------------------------------------------|-----------------------------|-----------------|----------------------------|----------------------------|--------|

| frances   | R <sub>Sel</sub> = 0, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 \text{ V}$    | 0.08            | 0.12                       | 0.15                       | MHz    |

| f(DCO03)  |                                                                               | V <sub>CC</sub> = 3 V       | 0.08            | 0.13                       | 0.16                       | IVITIZ |

| fraccian  | R <sub>sel</sub> = 1, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 0.14            | 0.19                       | 0.23                       | MHz    |

| f(DCO13)  |                                                                               | $V_{CC} = 3 V$              | 0.14            | 0.18                       | 0.22                       | IVITIZ |

| fraccass  | R <sub>sel</sub> = 2, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 0.22            | 0.30                       | 0.36                       | MHz    |

| f(DCO23)  |                                                                               | $V_{CC} = 3 V$              | 0.22            | 0.28                       | 0.34                       | IVITIZ |

| fraccass  | R <sub>sel</sub> = 3, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 0.37            | 0.49                       | 0.59                       | MHz    |

| f(DCO33)  |                                                                               | V <sub>CC</sub> = 3 V       | 0.37            | 0.47                       | 0.56                       | 101112 |

| f(DCO43)  | R <sub>sel</sub> = 4, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 0.61            | 0.77                       | 0.93                       | MHz    |

| ·(DCO43)  |                                                                               | V <sub>CC</sub> = 3 V       | 0.61            | 0.75                       | 0.90                       | 101112 |

| f(DCO53)  | R <sub>sel</sub> = 5, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 1               | 1.2                        | 1.5                        | MHz    |

| (DC053)   |                                                                               | $V_{CC} = 3 V$              | 1               | 1.3                        | 1.5                        | IVITIZ |

| f(DCO63)  | R <sub>sel</sub> = 6, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 1.6             | 1.9                        | 2.2                        | MHz    |

| ·(DCC63)  |                                                                               | V <sub>CC</sub> = 3 V       | 1.69            | 2.0                        | 2.29                       | 101112 |

| f(DCO73)  | R <sub>sel</sub> = 7, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 2.4             | 2.9                        | 3.4                        | MHz    |

| (00073)   |                                                                               | V <sub>CC</sub> = 3 V       | 2.7             | 3.2                        | 3.65                       |        |

| f(DCO47)  | R <sub>Sel</sub> = 4, DCO = 7, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | V <sub>CC</sub> = 2.2 V/3 V | fDCO40<br>× 1.7 | f <sub>DCO40</sub><br>×2.1 | f <sub>DCO40</sub><br>×2.5 | MHz    |

| fracerry  | R <sub>Sel</sub> = 7, DCO = 7, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C       | $V_{CC} = 2.2 V$            | 4               | 4.5                        | 4.9                        | MHz    |

| f(DCO77)  | NSEI - 7, BCO - 7, MOB - 0, BCOK - 0, 14 - 25 C                               | $V_{CC} = 3 V$              | 4.4             | 4.9                        | 5.4                        | IVITIZ |

| S(Rsel)   | S <sub>R</sub> = f <sub>Rsel+1</sub> / f <sub>Rsel</sub>                      | V <sub>CC</sub> = 2.2 V/3 V | 1.35            | 1.65                       | 2                          |        |

| S(DCO)    | S <sub>DCO</sub> = f <sub>DCO+1</sub> / f <sub>DCO</sub>                      | V <sub>CC</sub> = 2.2 V/3 V | 1.07            | 1.12                       | 1.16                       |        |

| Di        | Temperature drift, R <sub>Sel</sub> = 4, DCO = 3, MOD = 0                     | $V_{CC} = 2.2 V$            | -0.31           | -0.36                      | -0.40                      | %/°C   |

| Dt        | (see Note 30)                                                                 | V <sub>CC</sub> = 3 V       | -0.33           | -0.38                      | -0.43                      | 707 C  |

| DV        | Drift with $V_{CC}$ variation, $R_{sel} = 4$ , DCO = 3, MOD = 0 (see Note 30) | V <sub>CC</sub> = 2.2 V/3 V | 0               | 5                          | 10                         | %/V    |

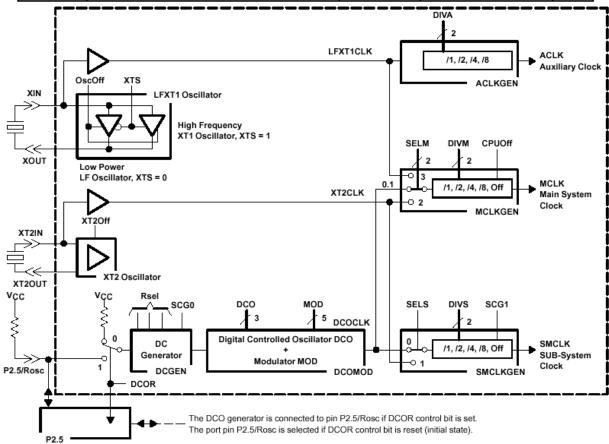

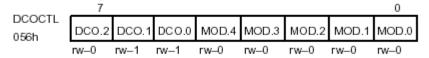

## 7.5 Basic Clock Module Control Registers

The Basic Clock Module is configured using control registers DCOCTL, BCSCTL1, and BCSCTL2, and four bits from the CPU status register: SCG1, SCG0, OscOff, and CPUOFF. User software can modify these control registers from their default condition at any time. The Basic Clock Module control registers are located in the byte-wide peripheral map and should be accessed with byte (.B) instructions.

| Register                        | Short Form | Register Type | Address | Initial State |

|---------------------------------|------------|---------------|---------|---------------|

| DCO control<br>register         | DCOCTL     | Read/write    | 056h    | 060h          |

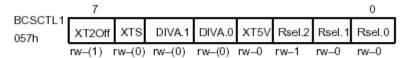

| Basic clock<br>system control 1 | BCSCTL1    | Read/write    | 057h    | 084h          |

| Basic clock<br>system control 1 | BCSCTL2    | Read/write    | 058h    | reset         |

# 7.5.1 Digitally-Controlled Oscillator (DCO) Clock-Frequency Control

DCOCTL is loaded with a value of 060h with a valid PUC condition.

- MOD.0.. MOD.4: The MOD constant defines how often the discrete frequency f<sub>DCO+1</sub> is used within a period of 32 DCOCLK cycles. During the remaining clock cycles (32–MOD) the discrete frequency f<sub>DCO</sub> is used. When the DCO constant is set to seven, no modulation is possible since the highest feasible frequency has then been selected.

- DCO.0 .. DCO.2: The DCO constant defines which one of the eight discrete frequencies is selected. The frequency is defined by the current injected into the dc generator.

### 7.5.2 Oscillator and Clock Control Register

BCSCTL1 is affected by a valid PUC or POR condition.

Bit0 to Bit2: The internal resistor is selected in eight different steps.

Rsel.0 to Rsel.2 The value of the resistor defines the nominal frequency.

The lowest nominal frequency is selected by setting Rsel=0.

Bit3, XT5V: XT5V should always be reset.

Bit4 to Bit5: The selected source for ACLK is divided by:

DIVA = 0: 1 DIVA = 1: 2 DIVA = 2: 4 DIVA = 3: 8

Bit6, XTS: The LFXT1 oscillator operates with a low-frequency clock crystal or with a high-frequency crystal:

XTS = 0: The low-frequency oscillator is selected.

XTS = 1: The high-frequency oscillator is selected.

The oscillator selection must meet the external crystal's operating condition.

Bit7, XT2Off: The XT2 oscillator is switched on or off:

XT2Off = 0: the oscillator is on

XT2Off = 1: the oscillator is off if it is not used for MCLK or SMCLK.

BCSCTL2 is affected by a valid PUC or POR condition.

0 BCSCTL2 SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR 058h rw = (0)rw = (0)rw = (0)rw = (0)rw-0 rw-0 rw=0rw=0

Bit0, DCOR: The DCOR bit selects the resistor for injecting current into the dc generator. Based on this current, the oscillator operates if activated.

> DCOR = 0: Internal resistor on, the oscillator can operate. The failsafe mode is on.

> DCOR = 1: Internal resistor off, the current must be injected externally if the DCO output drives any clock using the DCOCLK.

Bit1, Bit2: The selected source for SMCLK is divided by:

DIVS.1.. DIVS.0 DIVS = 0:1

DIVS = 1:2

DIVS = 2:4

DIVS = 3: 8

Bit3, SELS: Selects the source for generating SMCLK:

SELS = 0: Use the DCOCLK

SELS = 1: Use the XT2CLK signal (in three-oscillator systems)

or

LFXT1CLK signal (in two-oscillator systems)

Bit4, Bit5: The selected source for MCLK is divided by:

DIVM.0 .. DIVM.1 DIVM = 0: 1

DIVM = 1:2

DIVM = 2:4

DIVM = 3:8

Bit6, Bit7: Selects the source for generating MCLK:

SELM.0 .. SELM.1 SELM = 0: Use the DCOCLK

SELM = 1: Use the DCOCLK

SELM = 2: Use the XT2CLK (x13x and x14x devices) or

Use the LFXT1CLK (x11xx and x12xx devices)

SELM = 3: Use the LFXT1CLK