## The University of Alabama in Huntsville ECE Department CPE/EE 422/522 01 Midterm Exam Solution

1. (4 points) In general, what are static hazards in a combinational network.

Static hazards occur when an output has the wrong value temporarily due to propagation delay difference down multiple paths or simultaneous changes on multiple inputs.

2. (5 points) Obtain a minimum sum of products expression for the following function:

$$f(A, B, C, D) = \Sigma m(0, 1, 2, 5, 8, 9, 10, 13)$$

$$C$$

$$\begin{array}{c|c}

& I & I & B \\

\hline

A & I & B \\

\hline

& I & I & D \\

\hline

& F = \overline{C}D + \overline{B}\overline{D}

\end{array}$$

3. (7 points) Write a short VHDL description of a negative edge-triggered D flip-flop using a VHDL process.

```

entity DFF is

port (D, CLK : in bit;

Q, QBAR : out bit);

end DFF;

architecture DFF of DFF is

begin

process (CLK)

begin

if (CLK'event and CLK = '0') then

Q <= D;

QBAR <= not D;

end if;

end process;

end DFF;</pre>

```

4. (15 points) In the following VHDL process A, B, C, and D are all integers that have a value of 0 at time – 10 ns. If E changes from '0' to '1' at time 20 ns, specify the time(s) at which each signal will change and the value to which it will change. List these changes in chronological order. List any delta delays as a separate entry.

```

P1: process

begin

wait on E;

A <= 1 after 5 ns;

B <= A + 1;

wait for 0 ns;

C <= B after 10ns;

D <= A after 3 ns;

A <= A + 5 after 15 ns;</pre>

```

$B \le B + 7;$  end process P1;

| Time              | A | В | С | D | Е |

|-------------------|---|---|---|---|---|

| 10 ns             | 0 | 0 | 0 | 0 | 0 |

| 20 ns             | 0 | 0 | 0 | 0 | 1 |

| $20 + \Delta ns$  | 0 | 1 | 0 | 0 | 1 |

| $20 + 2\Delta ns$ | 0 | 8 | 0 | 0 | 1 |

| 23 ns             | 0 | 8 | 0 | 0 | 1 |

| 30 ns             | 0 | 8 | 1 | 0 | 1 |

| 35 ns             | 5 | 8 | 1 | 0 | 1 |

5. (6 points) What are the differences between signals and variables in VHDL? Where can signals and variables be used within a typical VHDL model?

## Signals

Declared in entities (ports), architectures, blocks

Values are scheduled to occur at a certain time, each signal has a queue of scheduled transactions

Can be used to communicate between processes

## Variables

Declared in processes, procedures, functions

Assignments take effect immediately

Can be used inside processes

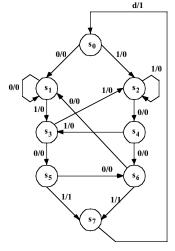

6. (15 points) A synchronous sequential network has one input and one output. If the input sequence 1001 or 0101 occurs, an output of two successive 1s will occur. The first of these 1s should occur coincident with the last input of the 1001 or 0101 sequence. The network should reset when the second 1 output occurs. For example,

Input sequence: 01101100010010 1101010

Output sequence: 0000000000011 0000011

Derive a Mealy state graph and table with a minimum number of states (8 states

|               | Next State |     | Output |     |

|---------------|------------|-----|--------|-----|

| Present State | X=0        | X=1 | X=0    | X=1 |

| S0            | S1         | S2  | 0      | 0   |

| S1            | S1         | S3  | 0      | 0   |

| S2            | S4         | S2  | 0      | 0   |

| S3            | S5         | S2  | 0      | 0   |

| S4            | S6         | S3  | 0      | 0   |

| S5            | S6         | S7  | 0      | 1   |

| S6            | S1         | S7  | 0      | 1   |

| S7            | S0         | S0  | 1      | 1   |

8. (10 points) Find a minimum-row PLA table to implement the following sets of functions.

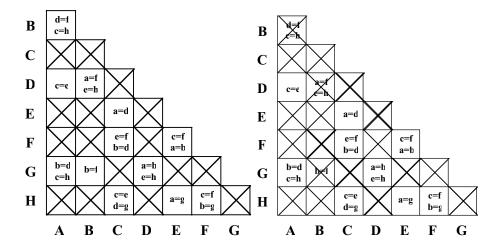

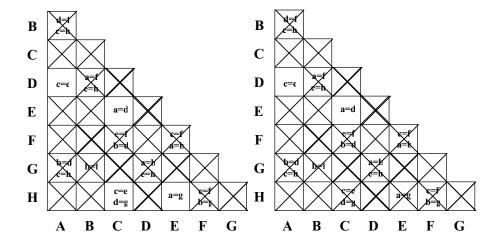

7. (10 points) Reduce the following state table to a minimum number of states. Show all your work in determining the state equivalents.

|               | Next  |       |        |

|---------------|-------|-------|--------|

| Present State | X = 0 | X = 1 | Output |

| A             | D     | C     | 0      |

| В             | F     | Н     | 0      |

| С             | Е     | D     | 1      |

| D             | A     | Е     | 0      |

| Е             | C     | A     | 1      |

| F             | F     | В     | 1      |

| G             | В     | Н     | 0      |

| Н             | C     | G     | 1      |

| Present State | Next State |       | Output |

|---------------|------------|-------|--------|

|               | X = 0      | X = 1 |        |

| A             | A          | C     | 0      |

| В             | F          | Н     | 0      |

| С             | С          | A     | 1      |

| F             | F          | В     | 1      |

| G             | В          | Н     | 0      |

| Н             | C          | G     | 1      |

9. (5 points) Write out the truth table for the following equation.

| F = | (A +   | B')•             | (C + | D)       |

|-----|--------|------------------|------|----------|

| _   | (4 4 1 | $\boldsymbol{L}$ | ( -  | <b>」</b> |

|   |   | - | (11.2) | $( \cup , \cup )$ |

|---|---|---|--------|-------------------|

| A | В | C | D      | F                 |

| 0 | 0 | 0 | 0      | 0                 |

| 0 | 0 | 0 | 1      | 1                 |

| 0 | 0 | 1 | 0      | 1                 |

| 0 | 0 | 1 | 1      | 1                 |

| 0 | 1 | 0 | 0      | 0                 |

| 0 | 1 | 0 | 1      | 0                 |

| 0 | 1 | 1 | 0      | 0                 |

| 0 | 1 | 1 | 1      | 0<br>0<br>0       |

| 1 | 0 | 0 | 0      |                   |

| 1 | 0 | 0 | 1      | 1                 |

| 1 | 0 | 1 | 0      | 1                 |

| 1 | 0 | 1 | 1      | 1                 |

| 1 | 1 | 0 | 0      | 0                 |

| 1 | 1 | 0 | 1      | 1                 |

| 1 | 1 | 1 | 0      | 1                 |

| 1 | 1 | 1 | 1      | 1                 |

|   |   |   |        |                   |

10. (5 points) What is the difference between combinational and sequential logic?

Sequential logic depends on both present inputs and previous inputs (state) Combinational logic depends on present inputs only

11. (5 points) What is the purpose of the architecture and entity sections of a VHDL model? How do they differ?

An entity defines the interface – signals and their directions. An architecture defines the internal functionality associated with the entity.

12. (1 point) An entity X, when used in another entity, becomes a \_component\_ for the entity Y.

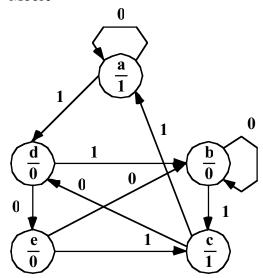

13. (12 points) Draw the state diagram for the following state machine. Is it a Moore machine or a Mealy machine?

```

ENTITY state machine IS

PORT (sig in ; IN BIT; clk : IN

BIT;

sig out : OUT BIT);

END state machine;

ARCHITECTURE state_machine OF

state machine IS

TYPE state type IS (a, b, c, d,

SIGNAL current state, next state

: state type;

BEGIN

PROCESS (sig in, current state)

sig out <= '0';

next_state <= b;</pre>

CASE current state

WHEN a \Rightarrow

IF sig in = '0' THEN

next state <= a;</pre>

ELSE

next state <= d;</pre>

END IF;

sig out <= '1';

WHEN b \Rightarrow

IF sig_in = '0' THEN

next state <= b;

next state <= c;</pre>

END IF;

WHEN C \Rightarrow

IF sig in = '1' THEN

next_state <= a;</pre>

ELSE

next_state <= d;</pre>

END IF;

```

```

sig out <= '1';

WHEN d \Rightarrow

IF sig in = '0' THEN

next state <= e;</pre>

END IF;

WHEN e \Rightarrow

IF sig in = '1' THEN

next state <= c;</pre>

END IF;

END CASE;

END PROCESS;

PROCESS (clk)

BEGIN

IF (clk' EVENT AND clk = '1')

THEN

current_state <=

next_state;

END IF;

END PROCESS;

END state machine;

```

## Moore