## The University of Alabama in Huntsville ECE Department CPE 426 01 Final Exam December 3, 2007

|    | Name:                                                                                                                                                                                                                                                                        |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | (5 points) Draw the transistor-level diagram of a two-input CMOS NAND gate.                                                                                                                                                                                                  |

|    |                                                                                                                                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                              |

| 2. | (10 points) Write a VHDL entity (3 points) and architecture (7 points) of a D latch with the generics TPDQ, which reflects the time for a change on D to appear at the outputs and TGDQ, which reflect the time for a change on the gate input, D, to appear at the outputs. |

|    |                                                                                                                                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                              |

|    |                                                                                                                                                                                                                                                                              |

| 3  | (1 point) consists of assigning each operation to a control step.                                                                                                                                                                                                            |

|    | (1 point) The of a component is the ratio of the busy time for the component to the execution time for the process.                                                                                                                                                          |

5. (5 points) If the NRE costs for FPGA and ASIC circuits are \$25,000 and \$575,000, respectively, and the cost of individual parts for FPGA and ASIC circuits are \$22 and \$7, respectively, what is the break-even manufacturing volume for these two types of circuits?

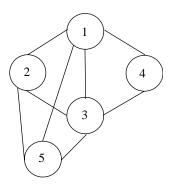

6. (10 points) Consider the dataflow graph shown below. As part of the cluster partitioning algorithm, determine which two nodes should be merged and show the dataflow graph that results from the merger.

7. (4 points) List the four types of paths that must be considered when doing timing analysis of sequential circuits.

- 8. (1 point) \_\_\_\_\_\_ is the process of transforming a behavioral description into a structural gate-level circuit.

- 9. (1 point) \_\_\_\_\_\_ is the process of making the connections between standard cells.

- 10. (10 points) For the data lifetime chart shown, use the left edge algorithm to obtain an efficient register allocation.

|            | A | В | С | D | Е | F | G | Н | I | J | K | L |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|

| <b>S</b> 1 |   |   |   | X |   |   | X |   |   | X |   |   |

| S2         | X |   |   | X |   |   | X |   | X | X |   |   |

| <b>S</b> 3 | X | X |   | X |   | X |   |   | X | X | X |   |

| S4         | X | X |   | X |   | X |   | X | X |   | X |   |

| S5         | X | X |   |   | X | X |   | X |   |   | X | X |

| <b>S</b> 6 |   | X | X |   | X | X |   | X |   |   |   | X |

| <b>S</b> 7 |   |   | X |   |   |   |   |   |   |   |   | X |

11. (6 points) Translate the following VHDL use (a) block statement(s) instead of a process:

```

process (S1, S4, DI, S3, Q)

begin

if (S1 = '1' and S4 = '1') then

Q <= DI after FFDEL;

elsif (S1 = '0' and S4 = '0') then

Q <="00000000" after FFDEL;

end if;

if (S3 = '1') then

DO <= Q after BUFDEL;

else

DO <= "ZZZZZZZZZZ" after BUFDEL;

end if;</pre>

```

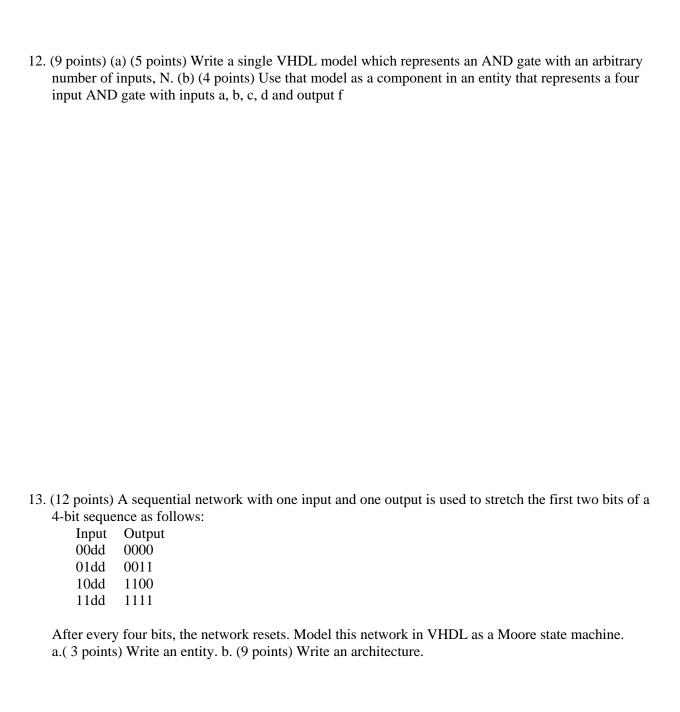

Consider the following VHDL code:

```

-- Entity declaration

entity SCHED2 is

port (A, B, C, D, E, F: in INTEGER;

CLK : in BIT;

W, X, Y: out INTEGER);

end SCHED2;

-- Architecture declaration

_____

architecture HIGH_LEVEL of SCHED2 is

signal V, Z: INTEGER;

begin

X \le ((A - B) * Z) * (C + V);

Y \le ((A * B) + Z) * E + F;

Z \le (C * D) + D * (E + F);

W \ll (A/F + C*C + D*(A - B))/V;

V \le (C * (B + D*E)) + F;

end HIGH_LEVEL;

```

16. (15 points) The following task refers to the VHDL code above. Assume that all operations are done in an ALU module and there are two ALU modules available. Derive a list schedule using the critical path priority metric for the operations.

17. (10 points) Write a VHDL model for a shift register module that includes a 16-bit shift register, a controller, and a 4-bit down counter. The shifter can shift a variable number of bits depending on a count provided to the shifter module. Inputs to the module are a number N (indicating a shift count) in the range 1 to 15, a 16-bit vector par\_in, a clock and a start signal, St. When St = '1', N is loaded in the down counter, and par\_in is loaded into the shift register. Then the shift register does a left shift N times and the controller returns to the start state. Assume that St is only '1' for one clock time. All operations are synchronous on the falling edge of the clock.