## The University of Alabama in Huntsville ECE Department CPE 426 01 Final Exam Solution Spring 2004

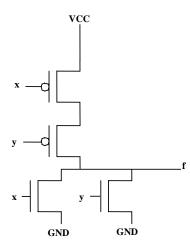

1. (7 points) Draw the transistor-level diagram of a CMOS two-input NOR gate.

2. (10 points) Write a VHDL entity (3 points) and architecture (7 points) of a two-input OR gate with the generics, TPLH and TPHL, which reflect the time for the output to make a low to high or high to low transition, respectively.

```

library ieee;

use ieee.std logic 1164.all;

entity OR DEL is

generic (TPLH, TPHL : time := 2 ns);

port (x, y : in std_logic;

: out std logic);

f

end OR DEL;

architecture BEHAV of OR DEL is

begin

process (x,y)

variable current, old : std logic;

begin

current := x or y;

f <= x or y;

if (current = '1' and old = '0') then

f <= x or y after TPHL;</pre>

elsif (current = '0' and old = '1') then

f <= x or y after TPLH;</pre>

end if;

old := current;

end process;

end BEHAV;

```

3. (1 point) \_\_\_\_\_\_ Routing \_\_\_\_\_\_ is the process of making the connections between standard cells.

4. (5 points) If the NRE costs for FPGA and CBIC circuits are \$21,000 and \$187,000, respectively, and the cost of individual parts for FPGA and CBIC circuits are \$15 and \$7, respectively, what is the breakeven manufacturing volume for these two types of circuits?

x – number of units 21000 + 15x = 187000 + 7x, 8x = 166000, x = 20750

5. (5 points) What kind of hardware element will be inferred by a synthesis tool from the following model? A flip-flop (because of the edge behavior) with synchronous reset.

```

library ieee;

use ieee.std_logic_1164.all;

entity WIDGET is

Port (A, B : in SIGNED (0 to 2);

CLK, RESET : in std_logic;

Z : out SIGNED(0 to 2));

end WIDGET;

architecture EXAMPLE of WIDGET is

begin

process (CLK, RESET)

begin

if (CLK'event and CLK = `1') then

if (RESET = 1') then

Z <= `0';

else

Z <= A nor B;

end if;

end if;

end process;

end EXAMPLE;

```

6. (10 points) For the data lifetime chart shown, use the left edge algorithm to obtain an efficient register allocation.

|            | А | В | С | D | Е | F | G | Η | Ι | J | Κ | L |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|

| <b>S</b> 1 |   |   | Х | Х |   |   | Х |   |   |   |   |   |

| S2         |   | Х | Х |   |   |   | Х |   |   | Х |   |   |

| <b>S</b> 3 |   | Х |   |   |   | Х | Х |   | Х | Х | Х |   |

| <b>S</b> 4 | Х | Х |   |   |   | Х |   |   | Х |   | Х | Х |

| S5         | Х |   |   |   | Х | Х |   | Х | Х |   | Х | Х |

| <b>S</b> 6 | Х |   |   |   | Х |   |   | Х | Х |   |   | Х |

| <b>S</b> 7 |   |   |   |   | Х |   |   |   | Х |   |   | Х |

|            | D | С | G | J | В | F | Κ | Ι | Α | L | Η | E |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|

| <b>S</b> 1 | Х | Х | Х |   |   |   |   |   |   |   |   |   |

| <b>S</b> 2 |   | Χ | Х | Х | Х |   |   |   |   |   |   |   |

| <b>S</b> 3 |   |   | Х | Х | Х | Х | Х | Х |   |   |   |   |

| <b>S</b> 4 |   |   |   |   | Х | Х | Х | Х | Х | Х |   |   |

| S5         |   |   |   |   |   | Χ | Χ | Х | Х | Х | Х | Х |

| <b>S</b> 6 |   |   |   |   |   |   |   | Х | Х | Х | Х | Х |

| <b>S</b> 7 |   |   |   |   |   |   |   | Х |   | Х |   | Х |

|            | R1 | R2 | R3 | R4 | R5 | R6 | R7 |

|------------|----|----|----|----|----|----|----|

| <b>S</b> 1 | D  | С  | G  |    |    |    |    |

| S2         | J  | С  | G  | В  |    |    |    |

| <b>S</b> 3 | J  | F  | G  | В  | Κ  | Ι  |    |

| <b>S</b> 4 | Α  | F  | L  | В  | Κ  | Ι  |    |

| S5         | Α  | F  | L  | Н  | Κ  | Ι  | E  |

| <b>S</b> 6 | Α  |    | L  | Η  |    | Ι  | Е  |

| <b>S</b> 7 |    |    | L  |    |    | Ι  | E  |

7. (1 point) Typically, a <u>test bench</u> is developed to validate a VHDL behavioral model.

8. (1 point) A(n) \_SDF file\_ provides the gate-level circuit with accurate timing backannotated from the layout.

9. (1 point) \_\_\_\_Pragmas\_ are inserted into VHDL models to give instructions to synthesis or other tools.

10. (18 points) Create a VHDL entity named  $en_dec_328$  that represents a 3-to-8 decoder with an active-low enable input which has an architecture which uses a case statement to represent the functionality of the decoder. Create a second entity and its accompanying architecture that represents a 4-to-16 decoder by using two instances of the en\_dec\_328 entity.

```

library ieee;

use ieee.std logic 1164.all;

entity EN_DEC_3TO8 is

port (EN : in std logic;

I : in std logic vector(2 downto 0);

0 : out std logic vector(7 downto 0));

end EN_DEC 3TO8;

architecture BEHAV of EN DEC 3TO8 is

begin

process(EN, I)

beqin

case EN is

when '0' =>

case I is

when "000" => 0 <= "00000001";

when "001" => O <= "00000010";

when "010" => 0 <= "00000100";

when "011" => O <= "00001000";

when "100" => O <= "00010000";

when "101" => O <= "00100000";

when "110" => O <= "01000000";

when "111" => O <= "10000000";

when others => 0 <= "00000000";

end case;

when others =>

O <= "0000000";

end case;

end process;

end BEHAV;

library ieee;

```

```

use ieee.std logic 1164.all;

entity DEC 4T016 is

port (I : in std logic vector(3 downto 0);

0 : out std logic vector(15 downto 0));

end DEC 4T016;

architecture STRUCT of DEC 4T016 is

signal I3BAR : std logic;

component EN DEC 3TO8C

port (EN : in std logic;

I : in std logic vector(2 downto 0);

0 : out std logic vector(7 downto 0));

end component;

for all : EN DEC 3TO8C use entity work. EN DEC 3TO8 (BEHAV);

begin

I3BAR <= not I(3);

U1 : EN DEC 3TO8C

port map (I(3), I(2 downto 0), O(7 downto 0));

U2 : EN DEC 3TO8C

port map(I3BAR, I(2 downto 0), O(15 downto 8));

end;

```

11. (15 points) Modify the following VHDL model to use block(s) instead of processes.

```

library ieee;

use ieee.std logic 1164.all;

entity BUFF REG is

generic (STRB DEL, EN DEL, ODEL: TIME);

port (DI: in std logic vector (1 to 8);

DS1, NDS2, STRB : in std logic;

DO: out std logic vector (1 to 8));

end BUFF_REG;

architecture THREE_PROC of BUFF_REG is

signal REG : std_logic_vector (1 to 8);

signal ENBLD : std logic;

begin

PREG: process (STRB)

PREG: block (STRB = `1')

begin

REG <= guarded DI after STRB DEL;

if (STRB = '1') then

end PREG;

REG <= DI after STRB DEL;

end if;

end process PREG;

ENABLE : process (DS1, NDS2)

ENABLE: block

ENBLD <= DS1 and not NDS2 after

begin

ENBLD <= DS1 and not NDS2 after

EN DEL;

end ENABLE;

EN DEL;

end process ENABLE;

OUTPUT : process (REG, ENBLD)

OUTPUT: block

DO <= REG after ODEL when ENBLD =

begin

`1' else `ZZZZZZZZ' after ODEL;

if (ENBLD = 1') then

DO <= REG after ODEL;

end OUTPUT;

else

DO <= "ZZZZZZZZ" after ODEL;

end if;

end process OUTPUT;

end THREE_PROC;

```

Consider the following VHDL code:

s4

+

\*

х

12

13 ( +

v

```

_____

-- Entity declaration

_____

_____

entity SCHED2 is

port (A, B, C, D, E, F: in INTEGER;

CLK : in BIT;

W, X, Y: out INTEGER);

end SCHED2;

_____

-- Architecture declaration

------

architecture HIGH_LEVEL of SCHED2 is

signal Z: INTEGER;

begin

X <= (A - B) * Z;

Y <= (A * B) + Z;

Z <= (C * D) + D * (E + F);

W <= A/F + C*C + D* (A - B);

end HIGH_LEVEL;

```

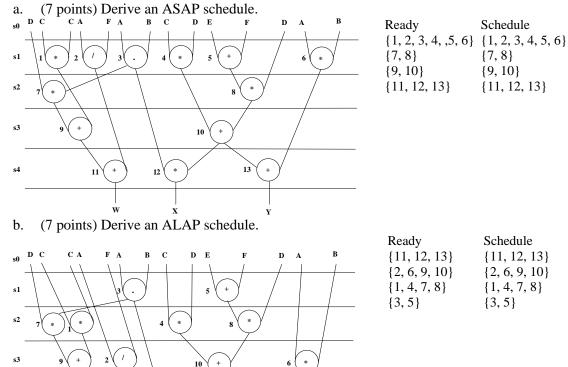

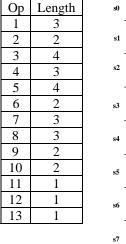

12. (14 points) The following tasks refer to the VHDL code above. Assume that there are no hardware constraints.

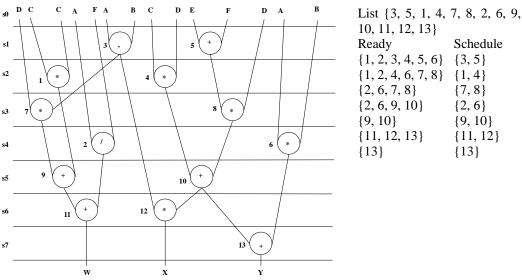

13. (10 points) Derive a list schedule using the critical path priority metric for the VHDL code above, using the following hardware constraint; all operations are done in an ALU module and there are two ALU modules available.

## Solution:

15. (1 point) \_\_\_\_\_ Communication \_\_\_\_\_ is the hardest problem.