## The University of Alabama in Huntsville ECE Department CPE 526 01 Final Exam Solution Spring 2004

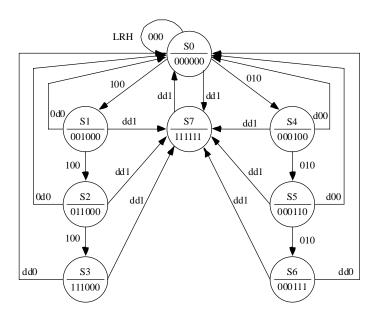

1. (15 points) An old Thunderbird car has three left and three right tail lights, which flash in unique patterns to indicate left and right turns.

| Left-turn pattern: |    |    |    |    |    |            | Ri         | ght-tu     | ırn pat | tern:      |            |

|--------------------|----|----|----|----|----|------------|------------|------------|---------|------------|------------|

| LC                 | LB | LA | RA | RB | RC | LC         | LB         | LA         | RA      | RB         | RC         |

| 0                  | 0  | 0  | 0  | 0  | 0  | $\Diamond$ | $\Diamond$ | $\Diamond$ | 0       | $\Diamond$ | $\Diamond$ |

| 0                  | 0  | •  | 0  | 0  | 0  | $\Diamond$ | $\Diamond$ | $\Diamond$ | •       | $\Diamond$ | $\Diamond$ |

| $\Diamond$         | •  | •  | 0  | 0  | 0  | 0          | $\Diamond$ | $\Diamond$ | •       |            | •          |

| •                  |    | •  | 0  | 0  | 0  | $\Diamond$ | $\Diamond$ | $\Diamond$ | •       |            |            |

Design a Moore sequential network to control these lights using VHDL. The network has three inputs, LEFT, RIGHT, and HAZ. LEFT and RIGHT come from driver's turn-signal switch and cannot be 1 at the same time. As indicated above, when LEFT = 1, the lights flash in a pattern LA on, LA and LB on, LA, LB, and LC on and all off; then the sequence repeats. When RIGHT = 1, the light sequence is similar. IF a switch from LEFT to RIGHT (or vice versa) occurs in the middle of a flashing sequence, the network should immediately go to the IDLE state (lights off) and then start the new sequence. HAZ comes from the hazard switch, and when HAZ = 1, all six lights flash on and off in unison. HAZ takes precedence if LEFT or RIGHT is also on. Assume that a clock signal is available with a frequency equal to the desired flashing rate.

```

library ieee;

use ieee.std_logic_1164.all;

entity THUNDERBIRD is

port (L, R, H, CLK : in std_logic;

LC, LB, LA, RA, RB, RC : out std_logic);

end THUNDERBIRD;

```

```

architecture BEHAVE of THUNDERBIRD is

type STATE_TYPE is (S0, S1, S2, S3, S4, S5, S6, S7);

signal CURRENT_STATE, NEXT_STATE : STATE_TYPE;

begin

process(CURRENT_STATE, L, R, H)

variable INPUTS : std logic vector(2 downto 0);

begin

INPUTS := L&R&H;

case CURRENT_STATE is

when S0 \Rightarrow if (INPUTS = "000") then

NEXT_STATE <= S0;</pre>

elsif (INPUTS = "100") then

NEXT_STATE <= S1;</pre>

elsif (INPUTS = "010") then

NEXT_STATE <= S4;</pre>

else

NEXT STATE <= S7;

end if;

when S1 \Rightarrow if (INPUTS(0) = '1') then

NEXT_STATE <= S7;</pre>

elsif (INPUTS = "100") then

NEXT_STATE <= S2;</pre>

else

NEXT_STATE <= S0;</pre>

end if;

when S2 \Rightarrow if (INPUTS(0) = '1') then

NEXT STATE <= S7;

elsif (INPUTS = "100") then

NEXT_STATE <= S3;</pre>

else

NEXT_STATE <= S0;</pre>

end if;

when S3|S6 \Rightarrow if (INPUTS(0) = '1') then

NEXT_STATE <= S7;</pre>

else

NEXT_STATE <= S0;</pre>

end if;

when S4 \Rightarrow if (INPUTS(0) = '1') then

NEXT_STATE <= S7;</pre>

elsif (INPUTS = "010") then

NEXT_STATE <= S5;</pre>

else

NEXT_STATE <= S0;</pre>

end if;

when S5 \Rightarrow if (INPUTS(0) \Rightarrow '1') then

NEXT_STATE <= S7;</pre>

elsif (INPUTS = "010") then

NEXT_STATE <= S6;</pre>

else

NEXT_STATE <= S0;</pre>

end if;

when S7 => NEXT_STATE <= S0;

end case;

end process;

```

```

process (CLK)

begin

if (CLK'event and CLK = '1') then

CURRENT STATE <= NEXT STATE;

end if;

end process;

process(CURRENT STATE)

begin

LC <= '0'; LB <= '0'; LA <= '0';

RA <= '0'; RB <= '0'; RC <= '0';

case CURRENT_STATE is

when S0 => null;

when S1 => LA <= '1';

when S2 => LA <= '1'; LB <= '1';

when S3 => LA <= '1'; LB <= '1'; LC <= '1';

when S4 \Rightarrow RA \iff '1';

when S5 => RA <= '1'; RB <= '1';

when S6 => RA <= '1'; RB <= '1'; RC <= '1';

when S7 => LA <= '1'; LB <= '1'; LC <= '1';

RA <= '1'; RB <= '1'; RC <= '1';

end case;

end process;

end BEHAVE;

```

- 2. (1 point) \_\_\_\_\_Routing\_\_\_\_\_ is the process of making the connections between standard cells.

- 3. (5 points) If the NRE costs for FPGA and CBIC circuits are \$21,000 and \$187,000, respectively, and the cost of individual parts for FPGA and CBIC circuits are \$15 and \$7, respectively, what is the breakeven manufacturing volume for these two types of circuits?

Let x be the break-even volume.

```

$21,000 +x * $15 = $187,000 + x * $7

x * $8 = $166,000

x = 20,750

```

4. (5 points) What kind of hardware element will be inferred by a synthesis tool from the following model? Answer: A flip-flop (because of edge behavior) with synchronous reset.

```

library ieee;

use ieee.std_logic_1164.all;

entity WIDGET is

Port (A, B : in SIGNED (0 to 2);

CLK, RESET : in std_logic;

Z : out SIGNED(0 to 2));

end WIDGET;

architecture EXAMPLE of WIDGET is

begin

process (CLK, RESET)

begin

if (CLK'event and CLK = '1') then

if (RESET = '1') then

```

```

Z <= `0';

else

Z <= A nor B;

end if;

end if;

end process;

end EXAMPLE;</pre>

```

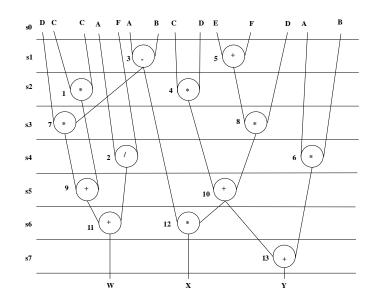

5. (10 points) For the data lifetime chart shown, use the left edge algorithm to obtain an efficient register allocation.

|            | A | В | С | D | Е | F | G | Н | I | J | K | L |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|

| <b>S</b> 1 |   |   | X | X |   |   | X |   |   |   |   |   |

| S2         |   | X | X |   |   |   | X |   |   | X |   |   |

| <b>S</b> 3 |   | X |   |   |   | X | X |   | X | X | X |   |

| S4         | X | X |   |   |   | X |   |   | X |   | X | X |

| S5         | X |   |   |   | X | X |   | X | X |   | X | X |

| <b>S</b> 6 | X |   |   |   | X |   |   | X | X |   |   | X |

| <b>S</b> 7 |   |   |   |   | X |   |   |   | X |   |   | X |

|            | D | C | G | J | В | F | K | I | A | L | Н | Е |

|------------|---|---|---|---|---|---|---|---|---|---|---|---|

| <b>S</b> 1 | X | X | X |   |   |   |   |   |   |   |   |   |

| S2         |   | X | X | X | X |   |   |   |   |   |   |   |

| <b>S</b> 3 |   |   | X | X | X | X | X | X |   |   |   |   |

| S4         |   |   |   |   | X | X | X | X | X | X |   |   |

| S4<br>S5   |   |   |   |   |   | X | X | X | X | X | X | X |

| <b>S</b> 6 |   |   |   |   |   |   |   | X | X | X | X | X |

| <b>S</b> 7 |   |   |   |   |   |   |   | X |   | X |   | X |

|            | R1 | R2 | R3 | R4 | R5 | R6 | R7 |

|------------|----|----|----|----|----|----|----|

| <b>S</b> 1 | D  | C  | G  |    |    |    |    |

| S2         | J  | C  | G  | В  |    |    |    |

| <b>S</b> 3 | J  | F  | G  | В  | K  | I  |    |

| S4         | A  | F  | L  | В  | K  | I  |    |

| S5         | A  | F  | L  | Н  | K  | I  | Е  |

| <b>S</b> 6 | A  |    | L  | Н  |    | I  | Е  |

| S7         |    |    | L  |    |    | I  | Е  |

| 6. (1 point) Typically, atest bench is developed to validate a VHDL behav |

|---------------------------------------------------------------------------|

|---------------------------------------------------------------------------|

7. (1 point) A(n) \_\_\_SDF file\_\_\_\_ provides the gate-level circuit with accurate timing backannotated from the layout.

8. (1 point) \_\_Pragmas\_\_\_ are inserted into VHDL models to give instructions to synthesis or other tools.

9. (15 points) Create a VHDL entity named en\_dec\_328 that represents a 3-to-8 decoder with an active-low enable input which has an architecture which uses a case statement to represent the functionality of the decoder. Create a second entity and its accompanying architecture that represents a 4-to-16 decoder by using two instances of the en\_dec\_328 entity.

```

entity EN DEC 328 is

port (EN : in std logic;

: in std logic vector (2 downto 0);

: out std logic vector (7 downto 0));

end EN DEC 328;

architecture BEHAV of EN DEC 3T08 is

begin

process(EN, I)

begin

case EN is

when '0' =>

case I is

when "000" \Rightarrow 0 <= "00000001";

when "001" \Rightarrow 0 <= "00000010";

when "010" \Rightarrow 0 <= "00000100";

when "011" => 0 <= "00001000";

when "100" => 0 <= "00010000";

when "101" => 0 <= "00100000";

when "110" \Rightarrow 0 <= "01000000";

when "111" \Rightarrow 0 <= "10000000";

when others => 0 <= "00000000";

end case;

when others =>

O <= "00000000";

end case;

end process;

end BEHAV;

library ieee;

use ieee.std logic 1164.all;

entity DEC_4TO16 is

port (I : in std logic vector(3 downto 0);

O : out std logic vector(15 downto 0));

end DEC 4T016;

architecture STRUCT of DEC 4T016 is

signal I3BAR : std logic;

component EN DEC 3TO8C

port (EN : in std logic;

I : in std_logic_vector(2 downto 0);

0 : out std_logic_vector(7 downto 0));

end component;

for all: EN DEC 3TO8C use entity work. EN DEC 3TO8 (BEHAV);

begin

I3BAR <= not I(3);

U1 : EN DEC 3TO8C

port map (I(3), I(2 downto 0), O(7 downto 0));

U2 : EN_DEC_3TO8C

port map(I3BAR, I(2 downto 0), O(15 downto 8));

end:

```

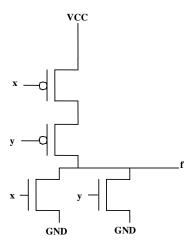

10. (5 points) Draw the transistor-level diagram of a CMOS two-input NOR gate.

11. (15 points) Modify the following VHDL model to use block(s) instead of processes.

```

library ieee;

use ieee.std logic 1164.all;

entity BUFF REG is

generic (STRB DEL, EN DEL, ODEL: TIME);

port (DI: in std_logic_vector (1 to 8);

DS1, NDS2, STRB : in std logic;

DO: out std logic vector (1 to 8));

end BUFF REG;

architecture THREE_PROC of BUFF_REG is

signal REG : std_logic_vector (1 to 8);

signal ENBLD : std_logic;

begin

PREG: process (STRB)

begin

if (STRB = '1') then

REG <= DI after STRB DEL;</pre>

end if;

end process PREG;

ENABLE: process (DS1, NDS2)

begin

ENBLD <= DS1 and not NDS2 after EN DEL;

end process ENABLE;

OUTPUT : process (REG, ENBLD)

begin

if (ENBLD = '1') then

DO <= REG after ODEL;

DO <= "ZZZZZZZZ" after ODEL;

end if;

end process OUTPUT;

end THREE PROC;

```

## Consider the following VHDL code:

```

-- Entity declaration

______

entity SCHED2 is

port (A, B, C, D, E, F: in INTEGER;

CLK : in BIT;

W, X, Y: out INTEGER);

end SCHED2;

-- Architecture declaration

_____

architecture HIGH_LEVEL of SCHED2 is

signal Z: INTEGER;

begin

X \le (A - B) * Z;

Y \le (A * B) + Z;

Z \le (C * D) + D * (E + F);

W \ll A/F + C*C + D*(A - B);

end HIGH_LEVEL;

```

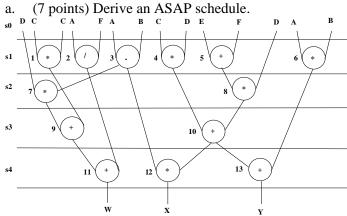

12. (14 points) The following tasks refer to the VHDL code above. Assume that there are no hardware constraints..

| Ready                  | Schedule               |

|------------------------|------------------------|

| $\{1, 2, 3, 4, 5, 6\}$ | $\{1, 2, 3, 4, 5, 6\}$ |

| {7, 8}                 | {7, 8}                 |

| {9, 10}                | {9, 10}                |

| {11, 12, 13}           | {11, 12, 13}           |

|                        |                        |

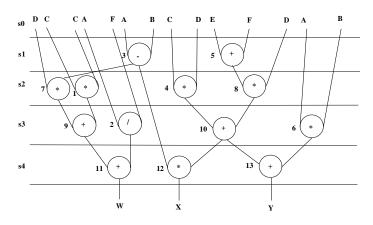

b. (7 points) Derive an ALAP schedule.

| Ready             | Schedule         |

|-------------------|------------------|

| {11, 12, 13}      | {11, 12, 13}     |

| $\{2, 6, 9, 10\}$ | {2, 6, 9, 10}    |

| $\{1, 4, 7, 8\}$  | $\{1, 4, 7, 8\}$ |

| {3, 5}            | {3, 5}           |

13. (10 points) Derive a list schedule using the critical path priority metric for the VHDL code above, using the following hardware constraint; all operations are done in an ALU module and there are two ALU modules available.

## Solution:

| Op     | Length                |

|--------|-----------------------|

| 1      | 3                     |

| 2      | 2                     |

| 3      | 3<br>2<br>4<br>3<br>4 |

| 5      | 3                     |

| 5      | 4                     |

| 6<br>7 | 2<br>3<br>3<br>2<br>2 |

| 7      | 3                     |

| 8      | 3                     |

| 9      | 2                     |

| 10     | 2                     |

| 11     | 1                     |

| 12     | 1                     |

| 13     | 1                     |

|        |                       |

| List {3, 5, 1, 4, 7 10, 11, 12, 13} | 7, 8, 2, 6, 9, |

|-------------------------------------|----------------|

| Ready                               | Schedule       |

| $\{1, 2, 3, 4, 5, 6\}$              | ${3,5}$        |

| $\{1, 2, 4, 6, 7, 8\}$              | $\{1, 4\}$     |

| $\{2, 6, 7, 8\}$                    | {7, 8}         |

| $\{2, 6, 9, 10\}$                   | $\{2, 6\}$     |

| {9, 10}                             | {9, 10}        |

| {11, 12, 13}                        | {11, 12}       |

| {13}                                | {13}           |

|                                     |                |

- 14. (1 point ) \_\_Allocation, scheduling, compilation\_\_\_\_\_ is one algorithmic-level synthesis task.

- 15. (1 point) \_\_\_\_\_\_ is the hardest problem.