## The University of Alabama in Huntsville ECE Department CPE 426 01 Final Exam Solution Spring 2013

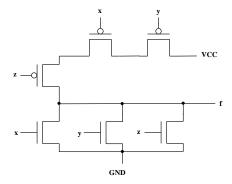

1. (6 points) Draw the transistor-level diagram of a three-input CMOS NOR gate.

2. (6 points) Has the following VHDL model been created following good synthesis style? If not, identify any problems

## No COUNT is an unconstrained integer

```

library IEEE;

use IEEE.std logic 1164.all;

entity PAR_TO_SER is

port(START,SHCLK: in STD LOGIC; PAR IN: in STD LOGIC VECTOR(7 downto 0);

SO: out STD LOGIC);

end PAR TO SER;

architecture ALG1 of PAR TO SER is

begin

P1:process(START,SHCLK)

variable COUNT: INTEGER := 0;

variable DONE: BOOLEAN;

if START = '1' then

COUNT := 7;

DONE := FALSE;

elsif SHCLK'event and SHCLK = '1' then

if DONE = FALSE then

SO <= PAR IN(COUNT);

COUNT := COUNT - 1;

end if;

if COUNT < 0 then

DONE := TRUE;

else

DONE := FALSE;

end if;

end if;

end process;

end ALG1;

```

3. (15 points) For the following VHDL architecture, give the values of A, B, C, D, and E, each time a change occurs. Carry this out until no further change occurs.

```

entity prob is

port (D : inout bit);

end prob;

architecture PROB of PROB is

signal A, B, C, E : bit;

P1: process (A, C)

begin

B <= A after 3 ns;

E <= C after 5 ns;</pre>

end process P1;

C1: C <= A after 10 ns;

C2: D \le ((A \text{ or } B) \text{ and } C)

or E after 1 ns;

process

begin process

A <= '1' after 5 ns;

wait;

end process;

```

end PROB;

| Time  | Α | В | С | D | Е |

|-------|---|---|---|---|---|

| 0 ns  | 0 | 0 | 0 | 0 | 0 |

| 5 ns  | 1 | 0 | 0 | 0 | 0 |

| 8 ns  | 1 | 1 | 0 | 0 | 0 |

| 15 ns | 1 | 1 | 1 | 0 | 0 |

| 16 ns | 1 | 1 | 1 | 1 | 0 |

| 20 ns | 0 | 1 | 1 | 1 | 1 |

|       |   |   |   |   |   |

|       |   |   |   |   |   |

|       |   |   |   |   |   |

|       |   |   |   |   |   |

|       |   |   |   |   |   |

|       |   |   |   |   |   |

| <b>Time</b>  | <b>Event</b>      | <b>Processes Triggered</b> | <b>Scheduled Transactions</b> | <b>Event?</b> |

|--------------|-------------------|----------------------------|-------------------------------|---------------|

| 5 ns         | $A \rightarrow 1$ | P1                         | B '1', 8 ns                   | Yes           |

|              |                   | P1                         | E '0', 10 ns                  | No            |

|              |                   | <b>C1</b>                  | C '1', 15 ns                  | Yes           |

|              |                   | <b>C2</b>                  | D '0', 6 ns                   | No            |

| 8 ns         | $B \rightarrow 1$ | <b>C2</b>                  | D '0', 9 ns                   | No            |

| 15 ns        | $C \rightarrow 1$ | P1                         | B '1', 18 ns                  | No            |

|              |                   | P1                         | E '1', 20 ns                  | Yes           |

|              |                   | <b>C2</b>                  | D '1', 16 ns                  | Yes           |

| 16 ns        | $D \rightarrow 1$ | None                       |                               |               |

| <b>20 ns</b> | $E \rightarrow 1$ | <b>C2</b>                  | D'1', 21 ns                   | No            |

| Scheduling Rules    | Transport          | Inertial                                                                                                                                                                                                                                   |

|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| New before existing | Overwrite existing | Overwrite existing                                                                                                                                                                                                                         |

| New after existing  | Append new         | $\begin{aligned} &\text{If } v_{\text{new}} = v_{\text{existing}}, & \text{append new} \\ &\text{Elsif } t_{\text{new}} \text{-} t_{\text{existing}} > \text{reject append new} \\ &\text{Else} & \text{overwrite existing} \end{aligned}$ |

4. (10 points) Develop an entity and architecture for an inhibited toggle flip-flop. This flip-flop has inputs I0, T, and Reset, and outputs Q and QN. Reset is active high and overrides the action of the other inputs. The flip-flop works as follows. If I0 = '1', the flip-flop changes state on the rising edge of T, if I0 = '0', no state change occurs (except on reset). Make the propagation delays from T to output and reset to output generics.

```

library ieee;

use ieee.std logic 1164.all;

entity INHIBITED TFF is

generic (TPHTQ, TPHRQ : time);

port (IO, T, RESET : in std logic;

Q, QN : out std logic);

end INHIBITED TFF;

architecture BEHAV of INHIBITED TFF is

begin

process (IO, T, RESET)

begin

if (RESET = '1') then

Q <= '0' after TPHRQ;

QN <= '1' after TPHRQ;

elsif (T'event and T = '1' and I0 = '1') then

Q <= not Q after TPHTQ;</pre>

QN <= not QN after TPHTQ;

end if;

end process;

end BEHAV;

```

- 5. (1 point) SDF files provide realistic delays for post-layout simulation.

- 6. (1 point) \_Xilinx\_ and \_Altera\_ are the two main FPGA vendors.

- 7. (1 point) **False** (True or False) Gate delay is by far the biggest contributor to circuit delay.

- 8. (1 point) \_True\_ (True or False) A synthesis tool will ignore all after clauses in a VHDL model.

- 9. (5 points) If the NRE costs for CBIC and ASIC circuits are \$100,000 and \$750,000, respectively, and the cost of individual parts for CBIC and ASIC circuits are \$20 and \$6, respectively, what is the break-even manufacturing volume for these two types of circuits?

```

$100,000 + $20x = $750,000 + $6x

14x = 650,000

x = 46429

```

10. (10 points) Write a VHDL procedure called scan\_results with an in-mode std\_logic\_vector signal parameter results, and out-mode variable parameters majority\_value of type std\_logic, majority\_count of type natural and tie of type Boolean. The procedure counts the occurrences of '0' and '1' values in results. It sets majority\_value to the most frequently occurring value, majority\_count to the number of occurrences and tie to true if there are an equal number of occurrences of '0' and '1'. If the number of occurrences is equal, the procedure sets majority\_value to 'X' and majority\_count to the number of occurrences.

```

library ieee;

use ieee.std logic 1164.all;

package MINE is

procedure scan results (signal results : in std logic vector;

variable majority value : out std logic;

variable majority count : out natural;

variable tie : out Boolean);

end package MINE;

package body MINE is

procedure scan results (signal results : in std logic vector;

variable majority value : out std logic;

variable majority count : out natural;

variable tie : out Boolean) is

variable one count, zero count : natural:= 0;

begin

tie := false;

majority value := 'X';

for i in results'range loop

if results(i) = '0' then

zero count := zero count + 1;

elsif results(i) = '1' then

one count := one count + 1;

end if;

end loop;

if (one count = zero count) then

tie := true;

majority count := zero count;

elsif (one count > zero count) then

majority_value := '1';

majority_count := one_count;

majority value := '0';

majority count := zero count;

end if;

return;

end scan results;

end package body MINE;

```

11. (15 points) Design an FSM circuit for controlling a simple home security system. The operation of the system is as follows.

Inputs: Front gate switch (FS)

Motion detector switch (MS) Asynchronous reset switch (R)

Clear switch (C)

Outputs: Front gate melody (FM)

Motion detector melody (MM)

- When the reset switch (R) is asserted, the FSM goes to the initialization state (S\_init) immediately.

- From state S\_init, the FSM unconditionally goes to the wait state (S\_wait).

- From state S\_wait, the FSM waits for one of the four switches to be activated. All the switches are active-high, so when a switch is pressed or activated, it sends out a 1. The following actions are taken when a switch is pressed:

- When FS is pressed, the FSM goes to state S\_front. In state S\_front, the front gate melody is turned on by setting FM = 1. The FSM remains in state S\_frontuntil the clear switch is pressed.

Once the clear switch is pressed, the FSM goes back to S\_wait.

- When MS is activated, the FSM goes to state S\_motion. In state S\_motion, MM is turned on with a 1. MM will remain on for two more clock periods and then the FSM will go back to S\_wait.

- From any state, as soon as the reset switch is pressed, the FSM immediately goes back to state S init.

- o Pressing the clear switch only affects the FSM when it is in state S\_front. The clear switch had no effect on the FSM when it is in any other state.

- o Any unused state encoding will have S\_init as their next state.

```

entity ALARM is

Port (CLK, R, MS, FS, C : in bit;

MM, FM : out bit);

end ALARM;

architecture BEHAV of ALARM is

type STATES is (S INIT, S WAIT, S FRONT, S MOTION0, S MOTION1, S MOTION2);

signal NEXT STATE, CURRENT STATE : STATES;

process (CURRENT STATE, C, MS, FS)

begin

case (CURRENT STATE) is

when S INIT => NEXT STATE <= S WAIT;

when S WAIT => if (FS = '1') then

NEXT STATE <= S FRONT;

elsif (MS = '1') then

NEXT STATE <= S MOTION0;

NEXT STATE <= S WAIT;

end if;

when S FRONT \Rightarrow if (C = '1') then

NEXT STATE <= S WAIT;

else

NEXT STATE <= S FRONT;

end if;

when S MOTIONO => NEXT STATE <= S MOTION1;

when S MOTION1 => NEXT STATE <= S MOTION2;

when S MOTION2 => NEXT STATE <= S WAIT;

end case;

end process;

process (R, CLK)

begin

if (R = '1') then

CURRENT STATE <= S INIT;

elsif (CLK'event and CLK = '1') then

CURRENT STATE <= NEXT STATE;

end if;

end process;

```

- 12. (1 point) The starting point from which a verification plan can be created is a \_design specification\_.

- 13. (1 point) List one type of coverage considered during the verification process. \_code, path, assertion, functional

- 14. (2 points) List two layers that may be present in a layered testbench:

```

__scenario____

_transaction

```

- 15. (1 point) A(n) \_interface\_ is a construct in System Verilog that represents a bundle of wires and has intelligence.

- 16. (10 points) Create a VHDL entity named en\_mux\_821 that represents a 8:1 multiplexer with an active-low enable input which has an architecture that uses a case statement to represent the functionality of the multiplexer. Create a second entity and its accompanying architecture that represents a 16:1 multiplexer by using two instances of the en\_mux\_821 entity.

```

library ieee;

use ieee.std_logic_1164.all;

entity EN_MUX_821 is

port (EN : in std_logic;

S : in std_logic_vector(2 downto 0);

D : in std_logic_vector(7 downto 0);

O : out std_logic);

end EN MUX 821;

```

```

architecture BEHAVE of EN_MUX_821 is

begin

process (EN, S, D)

variable TEMP : std logic;

begin

case S is

when "000" \Rightarrow TEMP := d(0);

when "001" => TEMP := d(1);

when "010" \Rightarrow TEMP := d(2);

when "011" \Rightarrow TEMP := d(3);

when "100" \Rightarrow TEMP := d(4);

when "101" \Rightarrow TEMP := d(5);

when "110" \Rightarrow TEMP := d(6);

when "111" \Rightarrow TEMP := d(7);

when others \Rightarrow TEMP := d(0);

end case;

if (EN = '0') then

O \le TEMP;

else

0 \le 'Z';

end if;

end process;

end BEHAVE;

library ieee;

use ieee.std logic 1164.all;

entity EN MUX 1621 is

port (EN : in std logic;

S : in std logic vector(3 downto 0);

d : in std logic vector(15 downto 0);

O : out std logic);

end EN MUX 1621;

architecture STRUCT of EN MUX 1621 is

signal T0, T1 : std logic;

begin

T0 \le not S(3);

U1: entity work.EN MUX 821(behave)

port map (EN \Rightarrow T0, S \Rightarrow S(2 \text{ downto } 0),

D \Rightarrow D(7 \text{ downto } 0), O \Rightarrow t1);

U2: entity work.EN MUX 821(behave)

port map (EN \Rightarrow s(3), s \Rightarrow s(2 \text{ downto } 0),

D \implies D(15 \text{ downto } 8), O \implies T1);

O \le T1 when EN = '0' else 'Z';

end STRUCT;

```

- 17. (1 point) **\_False\_** (True or False) A signal initialized in its declaration will be properly initialized post-synthesis.

- 18. (1 point) \_True\_ (True or False) Wait statements can be used to imply clocked behavior to the synthesis tool.

- 19. (1 point) The @ construct in System Verilog is similar to the \_wait\_ construct in VHDL.

- 20. (1 point) A **\_constrained random**\_ test environment allows you to run hundreds of tests without having to hand check the results.

21. (10 points) Develop a functional model of a 4-bit carry-look-ahead adder. The-adder has two 4-bit data inputs a (3 downto 0) and b (3 downto 0); a 4-bit data output, s (3 downto 0); a carry input, c\_in; a carry output, c\_out; a carry generate output, g, and a carry propagate output, p. The adder is described by the logic equations:

```

\begin{split} S_i &= A_i \oplus B_i \ C_{i\text{--}1} \oplus (\text{delay is 5 ns}) \\ G_i &= A_i B_i \ (\text{delay is 2 ns}) \\ P_i &= A_i + B_i \ (\text{delay is 3 ns}) \\ C_i &= G_i + P_i C_{i\text{--}1} \\ G &= G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 \\ P &= P_3 P_2 P_1 P_0 \end{split}

```

where the  $G_i$  are the intermediate carry generate signals, the  $P_i$  are the intermediate carry propagate signals and the  $C_i$  are the intermediate carry signals.  $C_{-1}$  is  $c_{-1}$  in and  $C_3$  is  $c_{-1}$  out. Use a loop construct for  $S_i$ ,  $G_i$ ,  $P_i$  and  $C_i$ .

```

library ieee;

use ieee.std logic 1164.all;

entity CLA ADDER is

port (A, B : in std logic vector(3 downto 0);

S : out std logic vector(3 downto 0);

C IN : in std logic;

C OUT, P, G : out std logic);

end CLA ADDER;

architecture BEHAVE of CLA ADDER is

signal PS, GS : std logic vector(3 downto 0);

process (A, B, C IN)

variable C : std logic vector(3 downto 0);

begin

S(0) \le A(0)  xor B(0)  xor C  IN  after 5  ns ;

PS(0) \le A(0) or B(0) after 3 ns;

GS(0) \le A(0) and B(0) after 2 ns;

C(0) := GS(0) \text{ or } (PS(0) \text{ and } C \text{ IN});

for i in 1 to 3 loop

S(i) \le A(i)  xor B(i)  xor C(i-1)  after 5  ns;

PS(i) \le A(i) or B(i) after 3 ns;

GS(i) \le A(i) and B(i) after 2 ns;

C(i) := GS(i) \text{ or } (PS(i) \text{ and } C(i-1));

end loop;

C OUT \leftarrow C(3);

G \leftarrow GS(3) or (PS(3)) and GS(2) or (PS(3)) and PS(2) and GS(1)

or (PS(3) and PS(2) and PS(1) and GS(0));

P \le PS(3) and PS(2) and PS(1) and PS(0);

end process;

end BEHAVE;

```

## Bonus:

(5 points) A synchronous (4-bit) up/down decade counter with outputs COUNT and CO works as follows: All state changes occur on the rising edge of the CLK input, except the asynchronous clear (CLR). When CLR = 0, the counter is reset regardless of the values of the other inputs. The inputs are DATA, CLR, LOAD, EN, UP.

```

If the LOAD input is 0, the data input DATA is loaded into the counter. If LOAD = EN = UP = 1, the counter is incremented. If LOAD = EN = 1, and UP = 0, the counter is decremented. If LOAD = EN = UP = 1, the carry output (CO) = 1 when the counter is in state 9. If LOAD = EN = 1 and UP = 0, the carry output (CO) = 1 when the counter is in state 0.

```

Create a SystemVerilog interface for this circuit that has a clocking block that defines directions relative to the test bench.

```

interface counter_if(input bit CLK);

logic LOAD, EN, UP, CO, CLR;

logic [3:0] COUNT, DATA;

clocking cb @(posedge CLK);

input COUNT, CO;

output LOAD, EN, UP, CLR, DATA;

endclocking

modport TEST (clocking cb);

endinterface

```