## The University of Alabama in Huntsville ECE Department EE 202 – 02 Fall 2013 Test 2 Solution

- (1 point) A <u>Karnaugh map</u> is a diagram made up of squares representing one minterm of the function that is to be minimized.

- (1 point) When two numbers with n digits each are added and the sum is a number occupying n + 1 digits, we say that an \_overflow\_ occurred.

- 3. (1 point) **\_False**\_.(True/False) When minimizing a function, all don't care terms must be included.

- 4. (1 point) A **\_prime implicant**\_.is a product term obtained by combining the maximum possible number of adjacent squares in the map.

- (1 point) The implementation of Boolean functions with NAND gates requires that the functions be in \_sum of products\_ form.

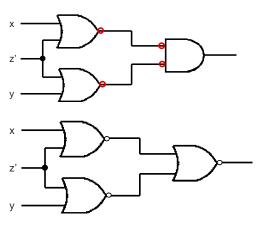

- 6. (10 points) Simplify the following function and implement it with two-level NOR gates: F(x, y, z) = x'z' + y'z' + yz' + xy

F' = x'z + y'zF = (x + z')(y + z') 7. (20 points) Design a circuit that has four inputs w, x, y, and z and four outputs A, B, C, and D. wxyz represents a binary-coded decimal digit. AB represents the quotient and CD the remainder when wxyz is divided by 3 (AB and CD represent 2-bit unsigned binary numbers. Output ABCD = 1111 if an invalid value appears on the inputs. You do not have to draw a circuit diagram.

| w | х | у | Z | А | В | С | D |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

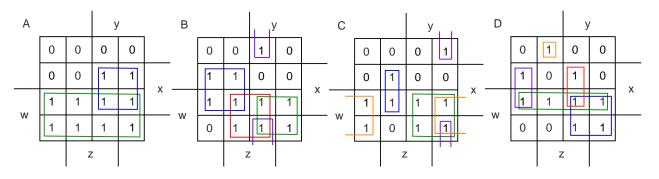

A = w + xy

B = wy + wz + xy' + x'yz

C = wy + wz' + x'yz' + xy'z

$\mathsf{D} = \mathsf{w}\mathsf{y} + \mathsf{x}\mathsf{y}\mathsf{z} + \mathsf{w}\mathsf{x} + \mathsf{x}\mathsf{y}'\mathsf{z}' + \mathsf{w}'\mathsf{x}'\mathsf{y}'\mathsf{z}$

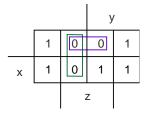

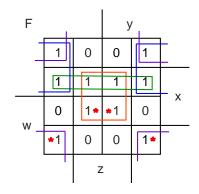

8. (15 points) Find all the prime implicants for the following Boolean function, and determine which are essential:

F (w, x, y, z) =Σ (0, 2, 4, 5, 6, 7, 8, 10, 13, 15)

Prime Implicants: xz, x'z', w'x, w'z' Essential Prime Implicants: xz, x'z'

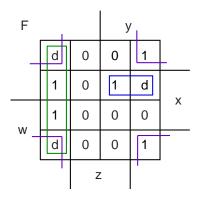

9. (10 points) Simplify the following Boolean function, using four-variable maps:

F (w, x, y, z) =  $\Sigma$ (4, 12, 7, 2, 10) d (w, x, y, z) =  $\Sigma$ (0, 6, 8)

F = x'z' + y'z' + w'xy

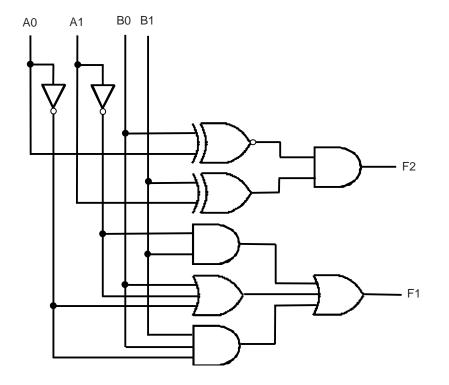

10. (15 points) Draw the logic diagram of the digital circuit specified by the following Verilog description:

```

module Circuit B (F1, F2, A0, A1, B0, B1);

input

A0, A1, B0, B1;

F1, F2;

output

w1, w2, w3, w4, w5, w6, w7;

wire

or

(F1, w1, w2, w3);

and (F2, w4, w5);

and (w1, w6, B1);

or

(w2, w6, w7, B0);

and (w3, w7, B0, B1);

not (w6, A1);

not (w7, A0);

xor (w4, A1, B1);

xnor

(w5, A0, B0);

endmodule

```

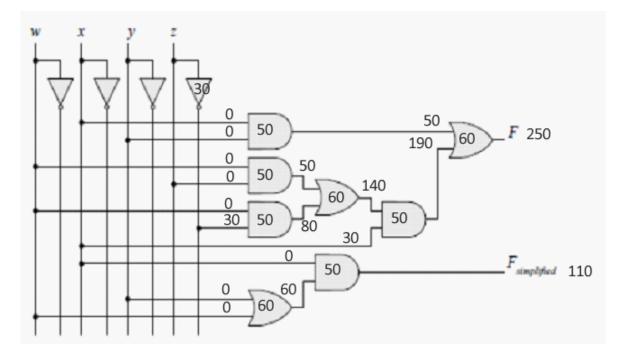

11. (10 points) Write a Verilog gate-level description of the circuit for F in problem 12, including delays.

```

`timescale 1 ps

module problem_12 (F, w, x, y, z);

output F;

input w, x, y, z;

wire w1, w2, w3, w4, w5, w6;

not #30(w1, z);

and #50(w2, x, y);

and #50(w3, w, z);

and #50(w4, w, w1);

or #60(w5, w3, w4);

and #50(w6, x, w5);

or #60(F, w2, w6);

endmodule

```

12. (15 points) If the delays in the circuit below are as given in the table, find the propagation delays from the inputs to F and F<sub>simplified</sub>.

| Logic Element | Propagation Delay |  |  |

|---------------|-------------------|--|--|

| Inverter      | 30 ps             |  |  |

| AND/NAND      | 50 ps             |  |  |

| OR/NOR        | 60 ps             |  |  |

| XOR           | 80 ps             |  |  |

| Full Adder    | 150 ps            |  |  |