## The University of Alabama in Huntsville ECE Department EE 202 – 02 Test 2 November 15, 2016

Name: \_\_\_\_\_

- 1. (1 point) An \_\_\_\_\_\_ is a digital circuit that has 2n input lines and n output lines. The output lines generate the binary code corresponding to the input value.

- 2. (1 point) \_\_\_\_\_ (True/False) Multiple outputs of a decoder can be 1 at the same time.

- 3. (1 point).\_\_\_\_\_ (True/False) Flip-flops exhibit edge sensitive behavior.

- 4. (1 points) A \_\_\_\_\_\_ state machine has outputs that depend only on the state.

- 5. (1 point) An \_\_\_\_\_\_ specifies the flip flop inputs necessary for a present state, next state pair.

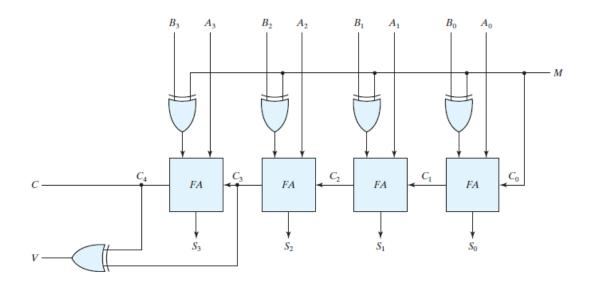

- 6. (15 points) If the delays in the circuit below are as given in the table, find the propagation delays from the inputs to  $S_0$ ,  $S_1$ ,  $S_2$ ,  $S_3$ , C and V

| Logic Element | Propagation Delay |

|---------------|-------------------|

| Inverter      | 30 ps             |

| AND/NAND      | 50 ps             |

| OR/NOR        | 60 ps             |

| XOR           | 80 ps             |

| Full Adder    | 150 ps            |

| J | К | Q(t+1) | D | Q(t+1) |   | Т | Q(t+1) |

|---|---|--------|---|--------|---|---|--------|

| 0 | 0 | Q(t)   | 0 | 0      |   | 0 | Q(t)   |

| 0 | 1 | 0      | 1 | 1      |   | 1 | Q'(t)  |

| 1 | 0 | 1      |   |        | - |   |        |

| 1 | 1 | Q'(t)  |   |        |   |   |        |

7. (20 points) Design a 3-bit counter which counts in the sequence 000, 001, 011, 010, 110, 111, 101, 100, 000 using clocked JK flip-flops. You do not have to draw the circuit diagram.

8. (15 points) A synchronous sequential circuit has one input and one output plus a synchronous reset which is active low. If the input sequence 1001 or 0101 occurs, an output of two successive 1s will occur. The first of these 1s should occur coincident with the last input of the 1001 or 0101 sequence. The network should reset when the second 1 output occurs. For example,

Input sequence:

01101100010010 0101010

Output sequence:

0000000000011 0000011

Draw a Mealy state diagram for this circuit. Do not include the reset in your diagram.

9. (15 points) Construct a 16 x 1 multiplexer with as many 2 x 1 multiplexers as you need. Use block diagrams.

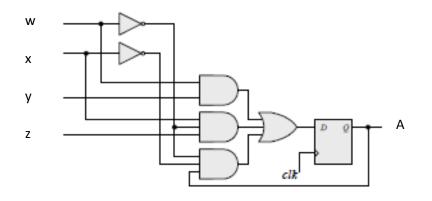

10. (15 points) For the figure given, derive the state table.

| W | Х | у | Z | A(t) | A(t+1) |

|---|---|---|---|------|--------|

| 0 | 0 | 0 | 0 | 0    |        |

| 0 | 0 | 0 | 0 | 1    |        |

| 0 | 0 | 0 | 1 | 0    |        |

| 0 | 0 | 0 | 1 | 1    |        |

| 0 | 0 | 1 | 0 | 0    |        |

| 0 | 0 | 1 | 0 | 1    |        |

| 0 | 0 | 1 | 1 | 0    |        |

| 0 | 0 | 1 | 1 | 1    |        |

| 0 | 1 | 0 | 0 | 0    |        |

| 0 | 1 | 0 | 0 | 1    |        |

| 0 | 1 | 0 | 1 | 0    |        |

| 0 | 1 | 0 | 1 | 1    |        |

| 0 | 1 | 1 | 0 | 0    |        |

| 0 | 1 | 1 | 0 | 1    |        |

| 0 | 1 | 1 | 1 | 0    |        |

| 0 | 1 | 1 | 1 | 1    |        |

| 1 | 0 | 0 | 0 | 0    |        |

| 1 | 0 | 0 | 0 | 1    |        |

| 1 | 0 | 0 | 1 | 0    |        |

| 1 | 0 | 0 | 1 | 1    |        |

| 1 | 0 | 1 | 0 | 0    |        |

| 1 | 0 | 1 | 0 | 1    |        |

| 1 | 0 | 1 | 1 | 0    |        |

| 1 | 0 | 1 | 1 | 1    |        |

| 1 | 1 | 0 | 0 | 0    |        |

| 1 | 1 | 0 | 0 | 1    |        |

| 1 | 1 | 0 | 1 | 0    |        |

| 1 | 1 | 0 | 1 | 1    |        |

| 1 | 1 | 1 | 0 | 0    |        |

| 1 | 1 | 1 | 0 | 1    |        |

| 1 | 1 | 1 | 1 | 0    |        |

| 1 | 1 | 1 | 1 | 1    |        |

|        | BCD |   |   | 8 | 4 | -2 | -1 |   |

|--------|-----|---|---|---|---|----|----|---|

| Number | Α   | В | С | D | w | х  | у  | z |

| 0      |     |   |   |   |   |    |    |   |

| 1      |     |   |   |   |   |    |    |   |

| 2      |     |   |   |   |   |    |    |   |

| 3      |     |   |   |   |   |    |    |   |

| 4      |     |   |   |   |   |    |    |   |

| 5      |     |   |   |   |   |    |    |   |

| 6      |     |   |   |   |   |    |    |   |

| 7      |     |   |   |   |   |    |    |   |

| 8      |     |   |   |   |   |    |    |   |

| 9      |     |   |   |   |   |    |    |   |

| 10     |     |   |   |   |   |    |    |   |

| 11     |     |   |   |   |   |    |    |   |

| 12     |     |   |   |   |   |    |    |   |

| 13     |     |   |   |   |   |    |    |   |

| 14     |     |   |   |   |   |    |    |   |

| 15     |     |   |   |   |   |    |    |   |

(15 points) Design a code converter that converts a decimal digit from binary coded decimal to the 8,

4, -2, -1 code. You do not need to draw the circuit diagram, equations are good enough.