## The University of Alabama in Huntsville ECE Department EE 202 – 01 Spring 2017 Final Exam Solution

| J | Κ | Q(t+1) |

|---|---|--------|

| 0 | 0 | Q(t)   |

| 0 | 1 | 0      |

| 1 | 0 | 1      |

| 1 | 1 | Q'(t)  |

| D | Q(t+1) |

|---|--------|

| 0 | 0      |

| 1 | 1      |

| Т | Q(t+1) |

|---|--------|

| 0 | Q(t)   |

| 1 | Q'(t)  |

1. (5 points Convert (5B2.1A<sub>12</sub>) to decimal.

5 x 12<sup>2</sup> + 11 x 12<sup>1</sup> + 2 x 12<sup>0</sup> + 1 x 12<sup>-1</sup> + 10 x 12<sup>-2</sup> = 5 x 144 + 11 x 12 + 2 x 1 + 1 x 0.08333 + 10 x 0.006944 = 720 + 132 + 2 + 0.08333 + 0.06944 = 854.1528

2. (10 points) How many 4 x 1 multiplexers does it take to make a 512 x 1 multiplexer?

```

First Level512/4 = 128Second Level128/4 = 32Third Level32/4 = 8Fourth Level8/4 = 2Fifth Level2/4 = 0, but need one, so make 2 to 1 out of 4 to 1The total number of multiplexers is 128 + 32 + 8 + 2 + 1 = 171

```

(10 points) Convert decimal +102 and +109 to binary, using 8-bit signed-2's-complement representation. Then perform the binary equivalent of (+102) + (+109). Convert the answer back to decimal and verify that it is correct or explain why it is not.

The result does not match because 211 does not fall between -128 and +127. This is a case of overflow.

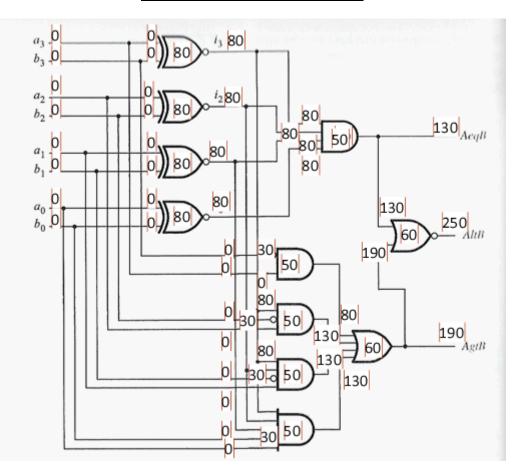

4. (10 points) If the delays in the circuit below are as given in the table, find the propagation delays from the inputs to A < B, A > B, and A = B.

| Logic Element | Propagation Delay |  |  |  |

|---------------|-------------------|--|--|--|

| Inverter      | 30 ps             |  |  |  |

| AND/NAND      | 50 ps             |  |  |  |

| OR/NOR        | 60 ps             |  |  |  |

| XOR/XNOR      | 80 ps             |  |  |  |

| Full Adder    | 150 ps            |  |  |  |

- 5 (1 point). A shift register that has bits transferred in one bit per clock cycle is said to have a <u>serial</u> load.

- 6. (1 point) <u>ASCII</u> assigns a unique binary representation for specific characters and symbols.

- 7. (1 point) <u>False</u> (True/False) Unsigned numbers can be both positive and negative.

- 8. (1 point) A <u>synchronous</u> counter is one that goes through a predefined set of states when a common clock signal is received at the clock inputs of all flip-flops.

- EE 202

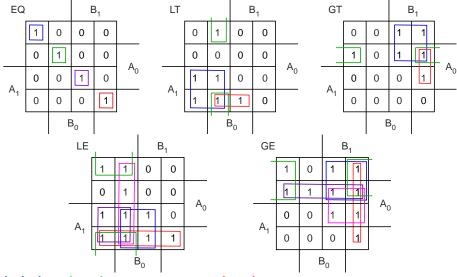

- 9. (15 points) Consider a circuit that compares two signed two-bit numbers and produces EQ if they are equal, LT if A < B, GT if A > B, LE if A  $\leq$  B, and GE if A  $\geq$  B, as outputs. Derive the equations for the circuitry for EQ, LT, GT, LE, and GE.

| A <sub>1</sub> | A <sub>0</sub> | B <sub>1</sub> | B <sub>0</sub> | EQ | LT | GT | LE | GE |

|----------------|----------------|----------------|----------------|----|----|----|----|----|

| 0              | 0              | 0              | 0              | 1  | 0  | 0  | 1  | 1  |

| 0              | 0              | 0              | 1              | 0  | 1  | 0  | 1  | 0  |

| 0              | 0              | 1              | 0              | 0  | 0  | 1  | 0  | 1  |

| 0              | 0              | 1              | 1              | 0  | 0  | 1  | 0  | 1  |

| 0              | 1              | 0              | 0              | 0  | 0  | 1  | 0  | 1  |

| 0              | 1              | 0              | 1              | 1  | 0  | 0  | 1  | 1  |

| 0              | 1              | 1              | 0              | 0  | 0  | 1  | 0  | 1  |

| 0              | 1              | 1              | 1              | 0  | 0  | 1  | 0  | 1  |

| 1              | 0              | 0              | 0              | 0  | 1  | 0  | 1  | 0  |

| 1              | 0              | 0              | 1              | 0  | 1  | 0  | 1  | 0  |

| 1              | 0              | 1              | 0              | 1  | 0  | 0  | 1  | 1  |

| 1              | 0              | 1              | 1              | 0  | 1  | 0  | 1  | 0  |

| 1              | 1              | 0              | 0              | 0  | 1  | 0  | 1  | 0  |

| 1              | 1              | 0              | 1              | 0  | 1  | 0  | 1  | 0  |

| 1              | 1              | 1              | 0              | 0  | 0  | 1  | 0  | 1  |

| 1              | 1              | 1              | 1              | 1  | 0  | 0  | 1  | 1  |

$A_1A_0$  represents the first signed two-bit number and  $B_1B_0$  represents the second signed two-bit number.

$EQ = A_{1}'A_{0}'B_{1}'B_{0}' + A_{1}'A_{0}B_{1}'B_{0} + A_{1}A_{0}B_{1}B_{0} + A_{1}A_{0}'B_{1}B_{0}'$

- $LT = A_{1}'B_{1}' + A_{0}'B_{1}'B_{0} + A_{1}A_{0}'B_{0}$

- $GT = A_{1}'B_{1} + A_{1}'A_{0}B_{1}' + A_{0}B_{1}B_{0}'$

- $\mathsf{LE} = \mathbf{A}_{1}\mathbf{B}_{0} + \mathbf{A}_{0}'\mathbf{B}_{1}' + \mathbf{A}_{1}\mathbf{A}_{0}' + \mathbf{A}_{1}\mathbf{B}_{1}' + \mathbf{B}_{1}'\mathbf{B}_{0}$

$\mathsf{GE} = \mathbf{A_1'B_1} + \mathbf{A_1'B_0'} + \mathbf{B_1B_0'} + \mathbf{A_1'A_0} + \mathbf{A_0B_1}$

- EE 202

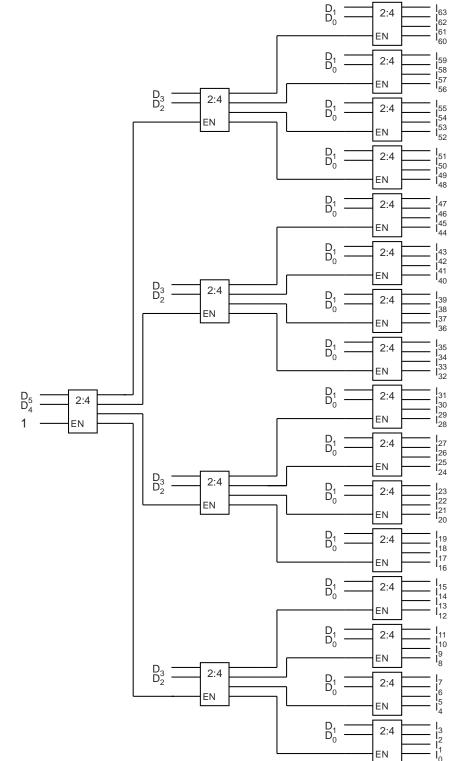

- 10. (15 points) Construct a 6 to 64decoder with 2 to 4 decoders with enable. If necessary, configure a 3 to 8 decoder to represent any additional logic needed. Use block diagrams for the components.

- 11. (1 point) A <u>self-correcting</u> is the name given to a sequential circuit that returns to a valid state after entering an unused state.

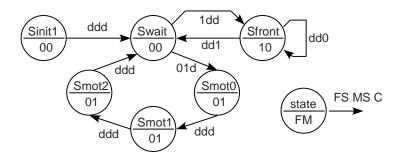

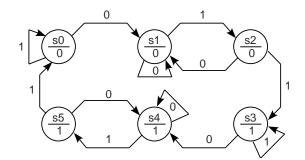

- 12. (15 points) For the following state diagram.

- (a) (5 points) Draw the state table

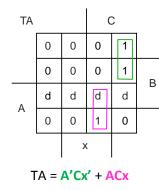

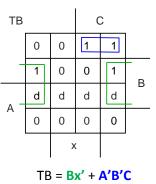

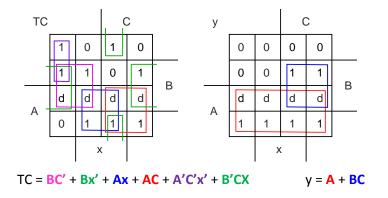

- (b) (4 points) Derive the excitation for implementing this circuit with T flip-flops.

- (c) (6 points) Derive the equations for the inputs of the T flip-flops and for the output.

| Pre | sent St | ate |   | Next State |   | Output | FF Inputs |    |    |    |

|-----|---------|-----|---|------------|---|--------|-----------|----|----|----|

| А   | В       | С   | х | А          | В | С      | у         | TA | ТВ | тс |

| 0   | 0       | 0   | 0 | 0          | 0 | 1      | 0         | 0  | 0  | 1  |

| 0   | 0       | 0   | 1 | 0          | 0 | 0      | 0         | 0  | 0  | 0  |

| 0   | 0       | 1   | 0 | 1          | 1 | 1      | 0         | 1  | 1  | 0  |

| 0   | 0       | 1   | 1 | 0          | 1 | 0      | 0         | 0  | 1  | 1  |

| 0   | 1       | 0   | 0 | 0          | 0 | 1      | 0         | 0  | 1  | 1  |

| 0   | 1       | 0   | 1 | 0          | 1 | 1      | 0         | 0  | 0  | 1  |

| 0   | 1       | 1   | 0 | 1          | 0 | 0      | 1         | 1  | 1  | 1  |

| 0   | 1       | 1   | 1 | 0          | 1 | 1      | 1         | 0  | 0  | 0  |

| 1   | 0       | 0   | 0 | 1          | 0 | 0      | 1         | 0  | 0  | 0  |

| 1   | 0       | 0   | 1 | 1          | 0 | 1      | 1         | 0  | 0  | 1  |

| 1   | 0       | 1   | 0 | 1          | 0 | 0      | 1         | 0  | 0  | 1  |

| 1   | 0       | 1   | 1 | 0          | 0 | 0      | 1         | 1  | 0  | 1  |

| 1   | 1       | 0   | 0 | d          | d | d      | 0         | d  | d  | d  |

| 1   | 1       | 0   | 1 | d          | d | d      | 0         | d  | d  | d  |

| 1   | 1       | 1   | 0 | d          | d | d      | 0         | d  | d  | d  |

| 1   | 1       | 1   | 1 | d          | d | d      | 0         | d  | d  | d  |

- 13. (15 points) A simple home security system operates as follows.

- Inputs:Front gate switch (FS), Motion detector switch (MS)Asynchronous reset switch (R), Clear switch (C)Outputs:Front gate melody (FM), Motion detector melody (MM)

- When the R is asserted, the FSM goes to the initialization state (S\_init) immediately.

- From state S\_init, the FSM unconditionally goes to the wait state (S\_wait).

- From state S\_wait, the FSM waits for one of the four switches to be activated. All the switches are active-high, so when a switch is pressed or activated, it sends out a 1. The following actions are taken when a switch is pressed:

- When FS is pressed, the FSM goes to state S\_front. In state S\_front, the front gate melody is turned on by setting FM = 1. The FSM remains in state S\_front until the clear switch is pressed. Once the clear switch is pressed, the FSM goes back to S\_wait.

- 2. When MS is activated, the FSM goes to state S\_motion. In state S\_motion, MM is turned on with a 1. MM will remain on for two more clock periods and then the FSM will go back to S\_wait.

- 3. From any state, as soon as R is pressed, the FSM immediately goes back to state S\_init.

- 4. Pressing the clear switch only affects the FSM when it is in state S\_front. The clear switch had no effect on the FSM when it is in any other state.

Draw a Moore state diagram of this system that does not include R as an input.