Building a PIC18C and System-on-a-Chip in an FPGA

Project Description

People

VHDL Model

Test Programs

Implementation

Links

Photo Album

Project Description

The goal of the PIC18C project is to design, develop

a synthesizible VHDL model, verify it using test programs, and implement

a core of the Microchip PIC18C microcontroller. The microcontroller core

is fully compatibile with the PIC18 series allowing program development

using high-level programming languages such as C.

The project phases are described below.

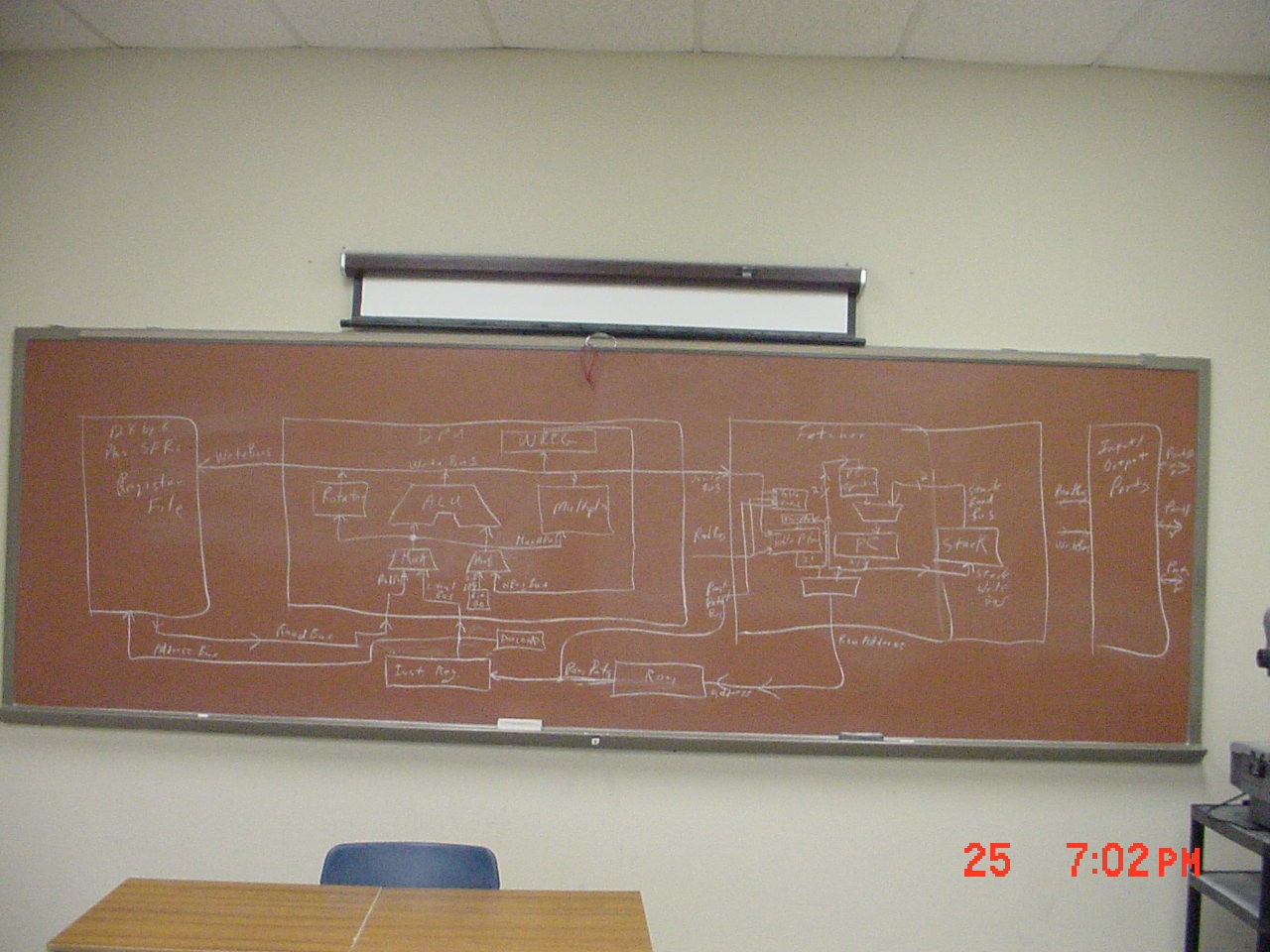

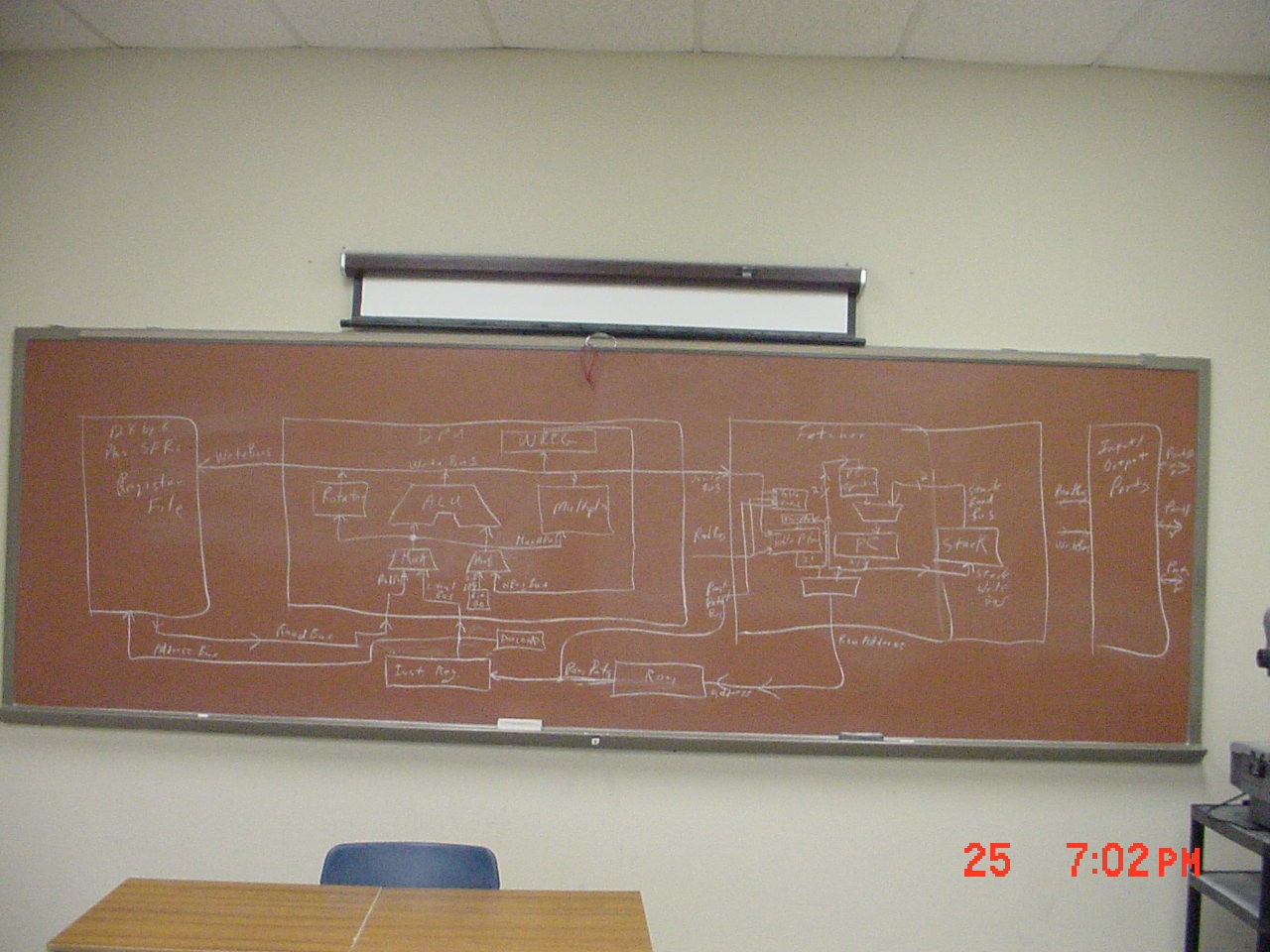

1. Design

The design phase involves the detailed study of the

architecture and instruction set. The key elements of the architecture

are defined: instruction fetcher, decoder, register file, etc. The instruction

set is examined and grouped to facilitate decoding.

2. VHDL Model Development

The key architectural components derived from the design

phase are used to form the VHDL model hierarchy. The hierarchy is shown

below.

PIC

Data Processing Unit (DPU)

Arithmetic-Logic

Unit (ALU)

Multiplier

Rotater

Bit-Operation

Processor (BOP)

Instruction Decoder

Fetcher

Instruction

Register

Program Counter

Hardware Return Stack

Block RAM

Constant Data

Fetcher

Register File

Block RAM

Reset

Watchdog Timer

ROM

Block RAM

3. Verification

The initial PIC operation verification is done by writing

a single assembly language test file for each instruction. The program

was assembled using Microchip’s MPLAB development system. A simple C program

is used to convert the output of the Assembler (HEX format) into a format

suitable for cut-and-paste into the ROM array.

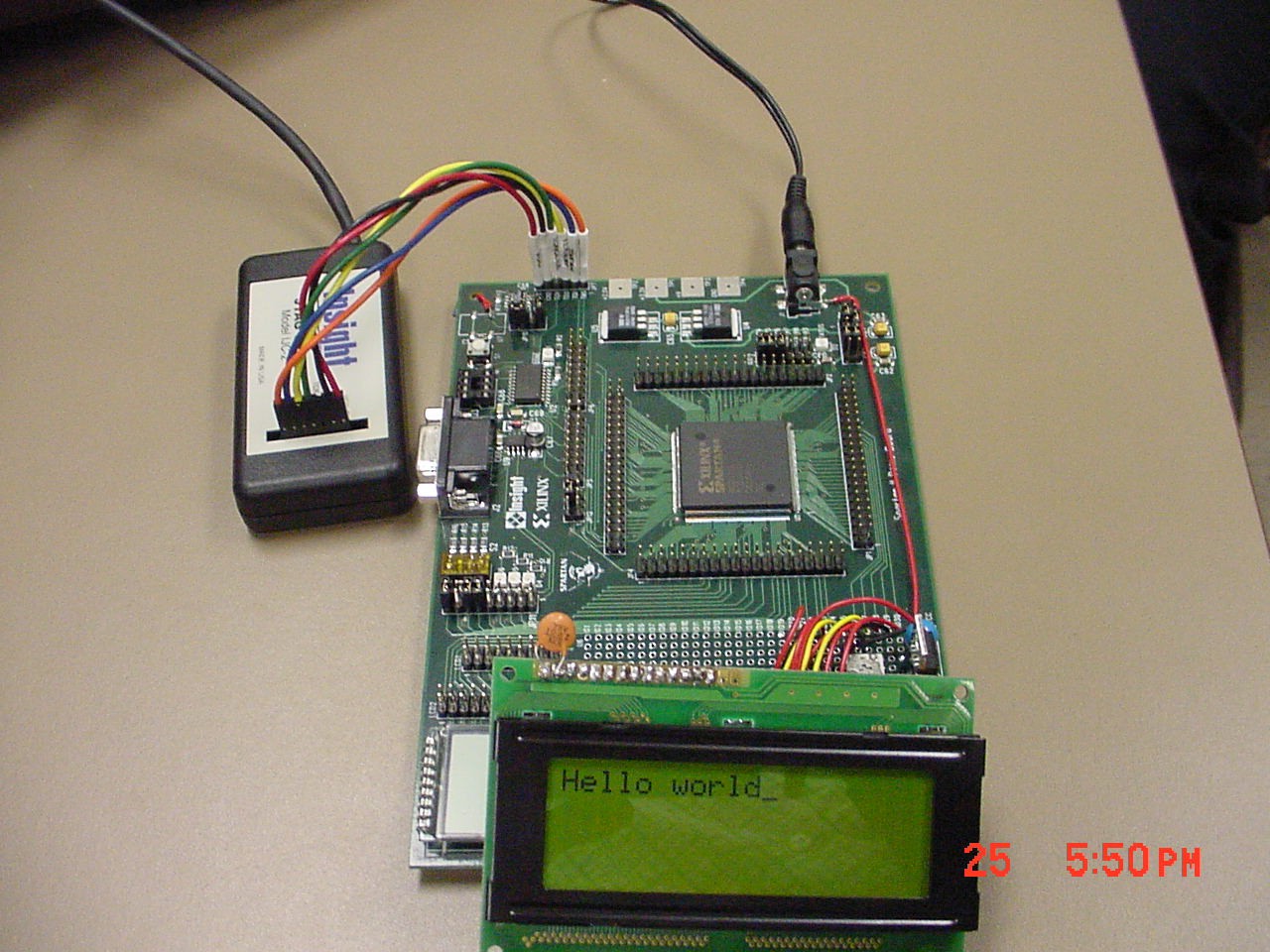

4. Implementation & Demonstation

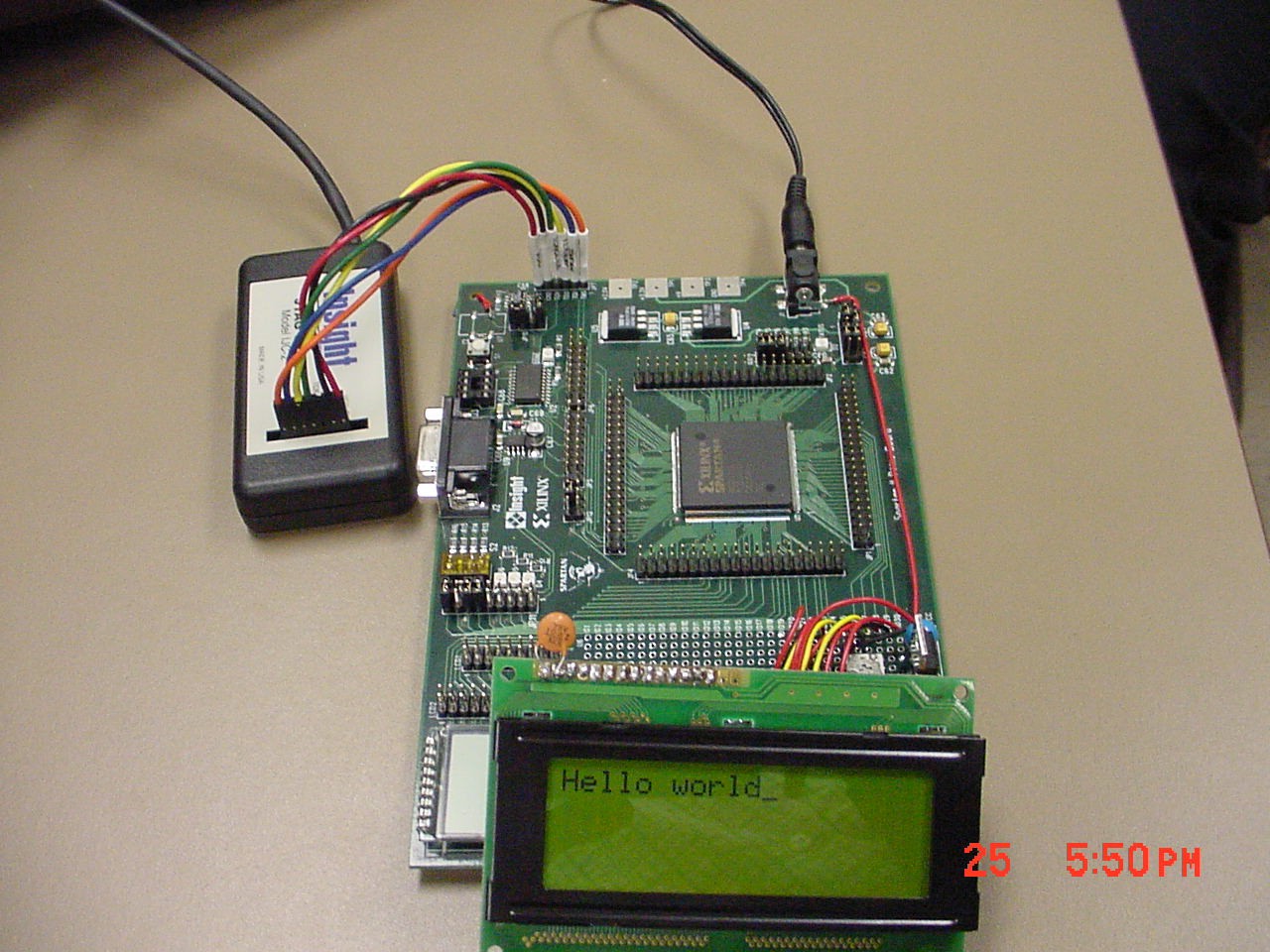

The PIC is sucessfully synthesized and implemented using

Spartan-II Development Kit with Xilinx Spartan-II XC2S100 FPGA. The PIC

operation is demonstrated by displaying a “Hello world” type string onto

a standard text-based LCD module. This milestone is reached on April 20th.

People

1. David Fatzer, team manager, chief architect, responsible for majority

of VHDL modules and testing. Email:

davidfatzer@netscape.net

2. Lee Pitts, team member, responsible for multiplier and UART VHDL

modules, and testing. Email: flaggle@yahoo.com

3. William Cruger, team member, responsible for implementation. Email:

crugerw@eng.uah.edu

4. Donn Hall, team member, responsible for UART VHDL model, and implementation.

Email: donn@halldoc.com

Advisor: Dr. Aleksandar

Milenkovic

VHDL Model

Coming soon!

Test Programs

Coming soon!

Implementation

Coming soon!

Links

PIC18C Reference Manual

MPLAB IDE

Spartan-II Development Kit

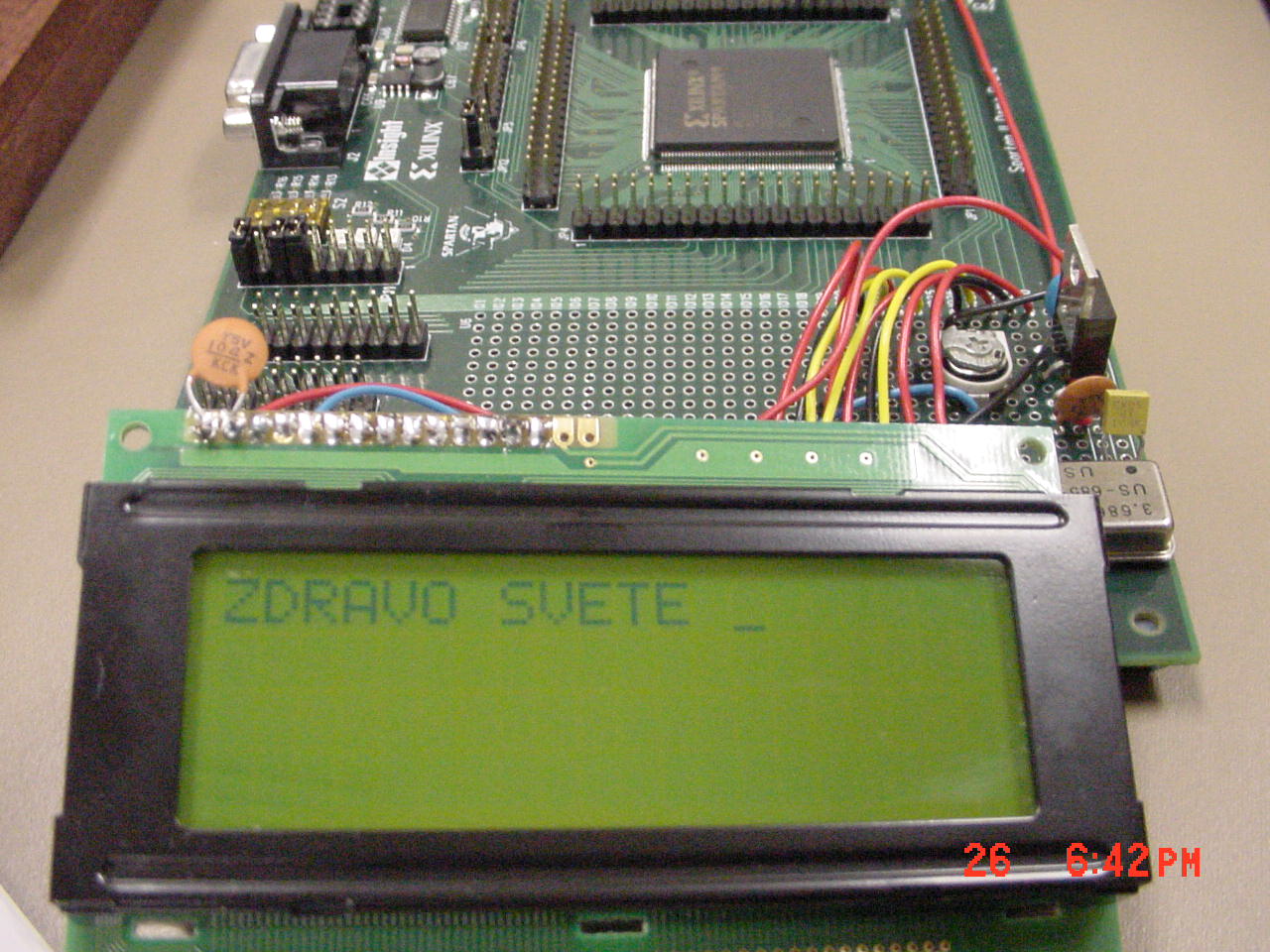

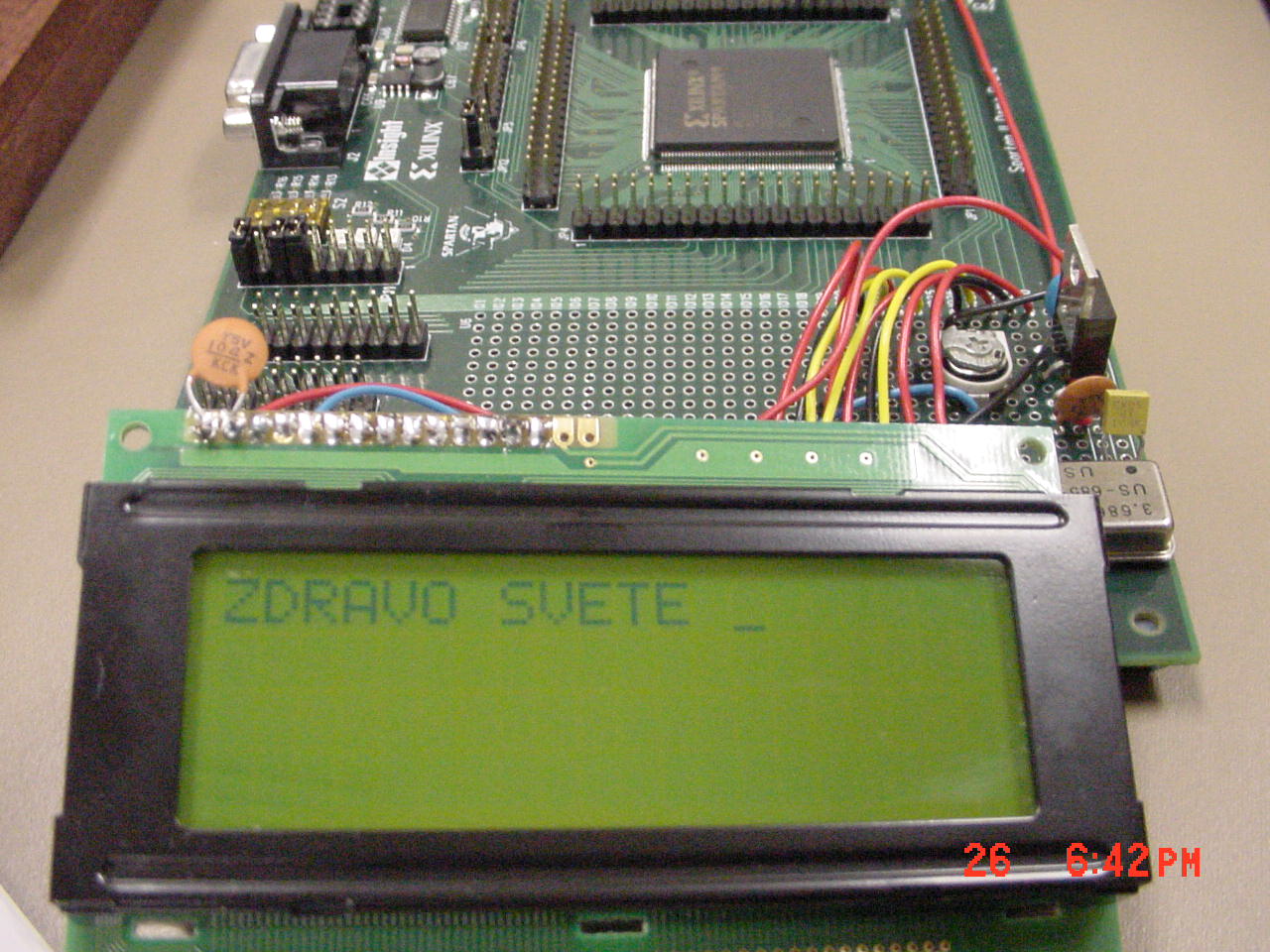

Photo Album

PIC18 on a board

Greetings from PIC

Greetings from PIC (2)