# CPE 323 Introduction to Embedded Computer Systems: The MSP430 System Architecture

Instructor: Dr Aleksandar Milenkovic Lecture Notes

### MSP430: System Architecture

- System Resets, Interrupts, and Operating Modes

- Basic Clock Module

- Watchdog Timer

## **MSP430: System Resets, Interrupts, and Operating Modes**

## **System Reset**

- Power-on Reset (POR)

- Powering up the device

- A low signal on the RST/NMI pin when configured in the reset mode

- An SVS low condition when PORON=1.

- Power-up Clear

- A POR signal

- Watchdog timer expiration when in watchdog mode only

- Watchdog timer security key violation

- A Flash memory security key violation

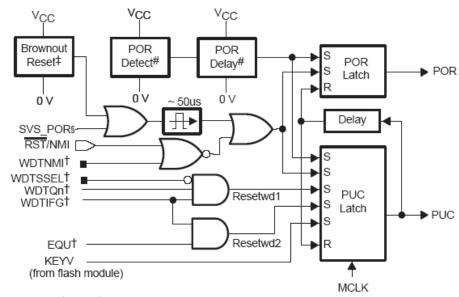

Figure 2-1. Power-On Reset and Power-Up Clear Schematic

- † From watchdog timer peripheral module

- # Devices with BOR only

- # Devices without BOR only

- § Devices with SVS only

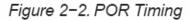

## Power-On Reset (POR)

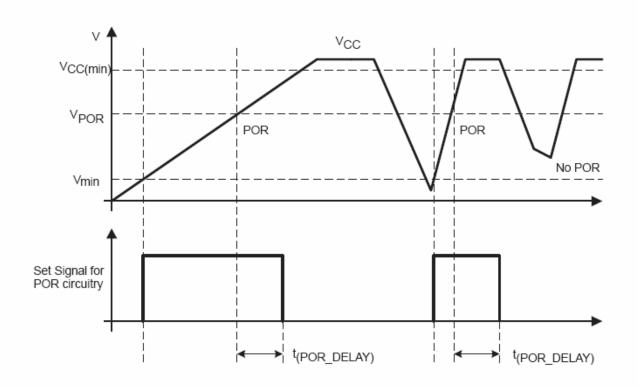

#### **Brownout Reset**

Figure 2-3. Brownout Timing

- The RST/NMI pin is configured in the reset mode

- I/O pins are switched to input mode as described in the Digital I/O chapter

- Other peripheral modules and registers are initialized as described in their respective chapters in this manual

- Status register (SR) is reset

- The watchdog timer powers up active in watchdog mode

- Program counter (PC) is loaded with address contained at reset vector location (0FFFEh).

CPU execution begins at that address

CPE 323

#### Software initialization

#### Your SW must initialize the MSP430

- Initialize the SP, typically to the top of RAM

- Initialize the watchdog to the requirements of the application

- Configure peripheral modules to the requirements of the application

- Additionally, the watchdog timer, oscillator fault, and flash memory flags can be evaluated to determine the source of the reset

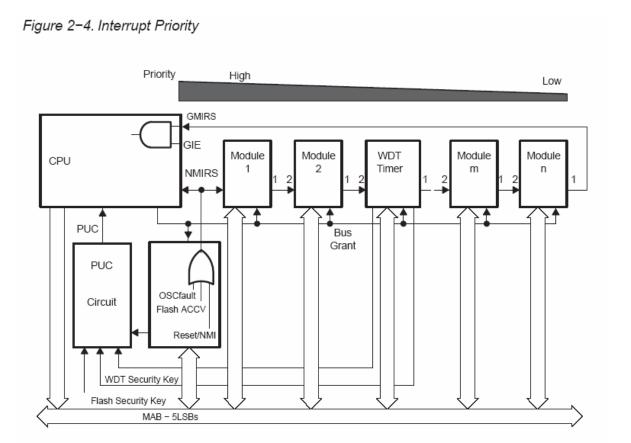

#### **Interrupts**

- 3 types

- System reset

- (Non)maskable NMI

- Maskable

- Interrupt

priorities are

fixed and

defined by the

arrangement of

modules

## (Non)-Maskable Interrupts (NMI)

- Sources

- An edge on the RST/NMI pin when configured in NMI mode

- An oscillator fault occurs

- An access violation to the flash memory

- Are not masked by GIE (General Interrupt Enable), but are enabled by individual interrupt enable bits (NMIIE, OFIE, ACCVIE)

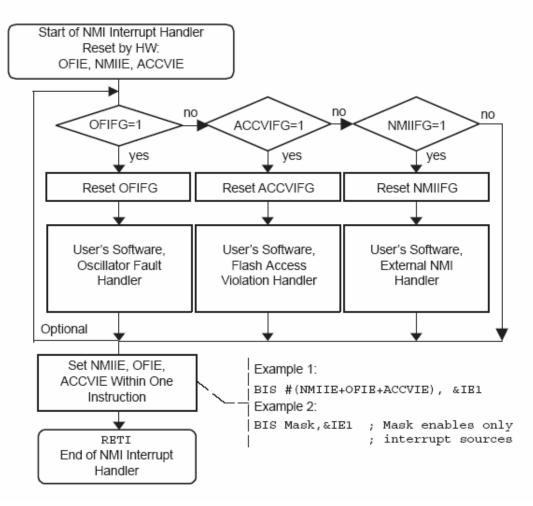

#### **NMI** Interrupt Handler

Figure 2-6. NMI Interrupt Handler

- Caused by peripherals with interrupt capability

- Each can be disabled individually by an interrupt enable bit

- All can be disabled by GIE bit in the status register

## Interrupt acceptance

- 1) Any currently executing instruction is completed.

- 2) The PC, which points to the next instruction, is pushed onto the stack.

- 3) The SR is pushed onto the stack.

- 4) The interrupt with the highest priority is selected if multiple interrupts occurred during the last instruction and are pending for service.

- 5) The interrupt request flag resets automatically on single-source flags. Multiple source flags remain set for servicing by software.

- 6) The SR is cleared with the exception of SCG0, which is left unchanged. This terminates any low-power mode. Because the GIE bit is cleared, further interrupts are disabled.

- 7) The content of the interrupt vector is loaded into the PC: the program continues with the interrupt service routine at that address.

- Takes 6 cc to execute

#### **Return from Interrupt**

- RETI Return from Interrupt Service Routine

- 1) The SR with all previous settings pops from the stack. All previous settings of GIE, CPUOFF, etc. are now in effect, regardless of the settings used during the interrupt service routine.

- 2) The PC pops from the stack and begins execution at the point where it was interrupted.

- Takes 5 cc to execute

## **Interrupt Vectors**

Table 2-1. Interrupt Sources, Flags, and Vectors

| INTERRUPT SOURCE                                           | INTERRUPT<br>FLAG          | SYSTEM<br>INTERRUPT                                | WORD<br>ADDRESS | PRIORITY    |

|------------------------------------------------------------|----------------------------|----------------------------------------------------|-----------------|-------------|

| Power-up, external reset, watchdog, flash password         | WDTIFG<br>KEYV             | Reset 0FFFEh 15,                                   |                 | 15, highest |

| NMI, oscillator fault,<br>flash memory access<br>violation | NMIIFG<br>OFIFG<br>ACCVIFG | (non)-maskable<br>(non)-maskable<br>(non)-maskable | 0FFFCh          | 14          |

| device-specific                                            |                            |                                                    | 0FFFAh          | 13          |

| device-specific                                            |                            |                                                    | 0FFF8h          | 12          |

| device-specific                                            |                            |                                                    | 0FFF6h          | 11          |

| Watchdog timer                                             | WDTIFG                     | maskable                                           | 0FFF4h          | 10          |

| device-specific                                            |                            |                                                    | 0FFF2h          | 9           |

| device-specific                                            |                            |                                                    | 0FFF0h          | 8           |

| device-specific                                            |                            |                                                    | 0FFEEh          | 7           |

| device-specific                                            |                            |                                                    | 0FFECh          | 6           |

| device-specific                                            |                            |                                                    | 0FFEAh          | 5           |

| device-specific                                            |                            |                                                    | 0FFE8h          | 4           |

| device-specific                                            |                            |                                                    | 0FFE6h          | 3           |

| device-specific                                            |                            |                                                    | 0FFE4h          | 2           |

| device-specific                                            |                            |                                                    | 0FFE2h          | 1           |

| device-specific                                            |                            |                                                    | 0FFE0h          | 0, lowest   |

## H

#### **Interrupt Service Routines**

#### Interrupt Service Routine declaration

```

// Func. declaration

Interrupt[int_vector] void myISR (Void);

Interrupt[int_vector] void myISR (Void)

{

// ISR code

}

```

#### EXAMPLE

```

Interrupt[TIMERA0_VECTOR] void myISR (Void);

Interrupt[TIMERA0_VECTOR] void myISR (Void)

{

// ISR code

}

```

#### **Interrupt Vectors**

```

Interrupt Vectors (offset from 0xFFE0)

************************************

#define PORT2 VECTOR 1 * 2 /* 0xFFE2 Port 2 */

\#define UART1TX VECTOR 2 * 2 /* 0xFFE4 UART 1 Transmit */

#define UART1RX_VECTOR 3 * 2 /* 0xFFE6 UART 1 Receive */

#define PORT1 VECTOR 4 * 2 /* 0xFFE8 Port 1 */

#define TIMERA1 VECTOR

5 * 2 /* 0xFFEA Timer A CC1-2, TA */

6 * 2 /* 0xFFEC Timer A CCO */

#define TIMERAO VECTOR

#define ADC VECTOR

7 * 2 /* 0xffEE ADC */

#define UARTOTX VECTOR

8 * 2 /* 0xFFF0 UART 0 Transmit */

#define UARTORX VECTOR

9 * 2 /* 0xFFF2 UART 0 Receive */

#define WDT VECTOR

10 * 2 /* 0xFFF4 Watchdog Timer */

#define COMPARATORA VECTOR 11 * 2 /* 0xFFF6 Comparator A */

#define TIMERB1 VECTOR 12 * 2 /* 0xFFF8 Timer B 1-7 */

#define TIMERBO VECTOR

13 * 2 /* OxFFFA Timer B O */

14 * 2 /* OxFFFC Non-maskable */

#define NMI VECTOR

#define RESET VECTOR

15 * 2 /* OxFFFE Reset [Highest Pr.] */

```

## Operating Modes (to be discussed later)

| SCG1 | SCG0 | OSCOFF | CPUOFF | Mode   | CPU and Clocks Status                                                                                                                    |

|------|------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | 0      | 0      | Active | CPU is active, all enabled clocks are active                                                                                             |

| 0    | 0    | 0      | 1      | LPM0   | CPU, MCLK are disabled SMCLK , ACLK are active                                                                                           |

| 0    | 1    | 0      | 1      | LPM1   | CPU, MCLK, DCO osc. are disabled DC generator is disabled if the DCO is not used for MCLK or SMCLK in active mode SMCLK, ACLK are active |

| 1    | 0    | 0      | 1      | LPM2   | CPU, MCLK, SMCLK, DCO osc. are disabled DC generator remains enabled ACLK is active                                                      |

| 1    | 1    | 0      | 1      | LPM3   | CPU, MCLK, SMCLK, DCO osc. are disabled DC generator disabled ACLK is active                                                             |

| 1    | 1    | 1      | 1      | LPM4   | CPU and all clocks disabled                                                                                                              |

## MSP430: Basic Clock System

#### **Basic Clock System**

#### **MSP430 Clock System**

- Low System Cost

- Low Power

- Variety of operating modes driven by application, software selectable

- Support for the Burst Mode –

when activated system starts and reacts rapidly

- Stability over voltage and temperature

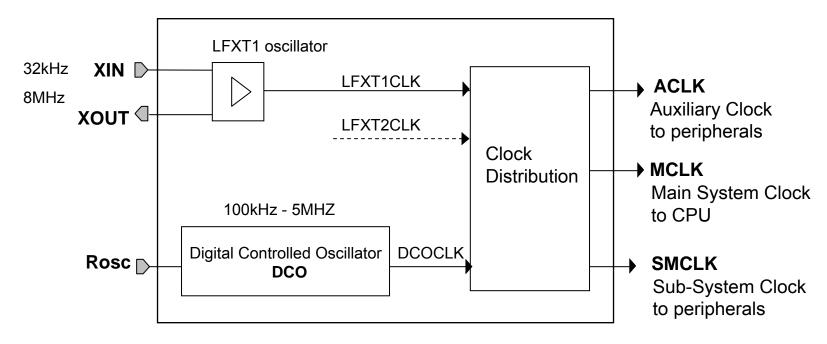

#### **Basic Clock System: MSP430x1xx**

- One DCO, internal digitally controlled oscillator

- Generated on-chip RC-type frequency controlled by SW + HW

- One LF/XT oscillator

- LF: 32768Hz

- XT: 450kHz .... 8MHz

- Second LF/XT2 oscillator

Optional XT: 450kHz .... 8MHz

- Clocks:

- ACLK auxiliary clock ACLK

- MCLK main system clock MCLK

- SMCLK sub main system clock

- DCOCLK Generated on-chip with 6μs start-up

- 32KHz Watch Crystal or High Speed Crystal / Resonator to 8MHz

- (our system is 4MHz/8MHz high Speed Crystal)

- Flexible clock distribution tree for CPU and peripherals

- Programmable open-loop DCO Clock with internal and external current source

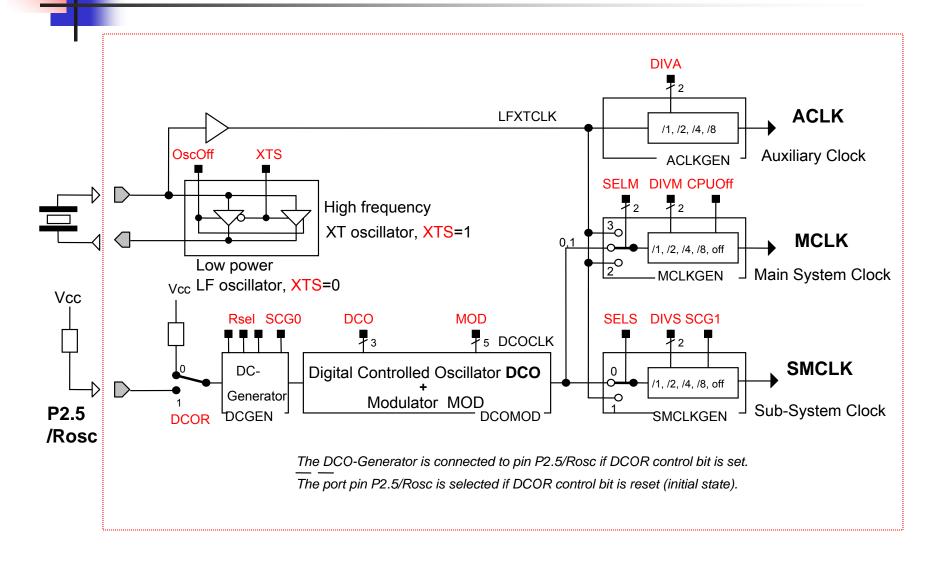

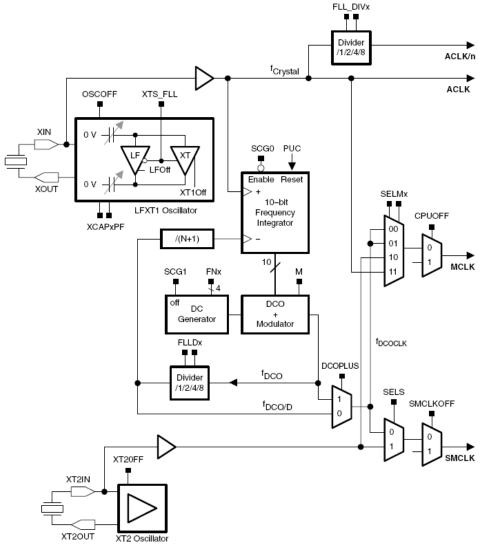

#### **Basic Clock System – Block Diagram**

## Basic clock block diagram (MSP430x13x/14x/15x/16x)

## **Basic operation**

- After POC (Power Up Clear)

MCLK and SMCLK are sourced by DCOCLK (approx. 800KHz) and ACLK is sourced by LFXT1 in LF mode

- Status register control bits SCG0, SCG1, OSCOFF, and CPUOFF configure the MSP430 operating modes and enable or disable portions of the basic clock module

- SCG1 when set, turns off the SMCLK

- SCG0 when set, turns off the DCO dc generator (if DCOCLK is not used for MCLK or SMCLK)

- OSCOFF when set, turns off the LFXT1 crystal oscillator (if LFXT1CLK is not use for MCLK or SMCLK)

- CPUOFF when set, turns off the CPU

- DCOCTL, BCSCTL1, and BCSCTL2 registers configure the basic clock module

- The basic clock can be configured or reconfigured by software at any time during program execution

#### **Basic Clock Module - Control Registers**

The Basic Clock Module is configured using control registers DCOCTL, BCSCTL1, and BCSCTL2, and four bits from the CPU status register: SCG1, SCG0, OscOff, and CPUOFF.

User software can modify these control registers from their default condition at any time. The Basic Clock Module control registers are located in the byte-wide peripheral map and should be accessed with byte (.B) instructions.

| Register State               | Short Form | Register Type | Address | Initial State |

|------------------------------|------------|---------------|---------|---------------|

| DCO control                  |            |               |         |               |

| register<br>Basic clock      | DCOCTL     | Read/write    | 056h    | 060h          |

| system control 1 Basic clock | BCSCTL1    | Read/write    | 057h    | 084h          |

| system control 2             | BCSCTL2    | Read/write    | 058h    | reset         |

### **Basic Clock Module - Control Registers**

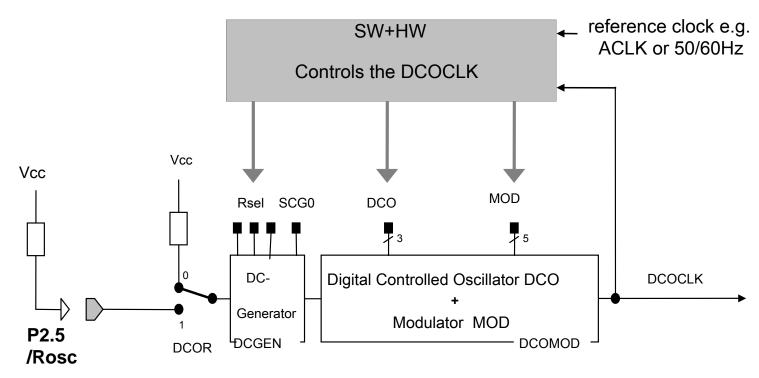

- Direct SW Control

- DCOCLK can be Set Stabilized

- Stable DCOCLK over Temp/Vcc.

#### **BCSCTL2**

058h

#### **BCSCTL1**

057h

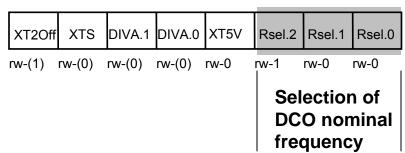

#### **DCOCTL**

056h

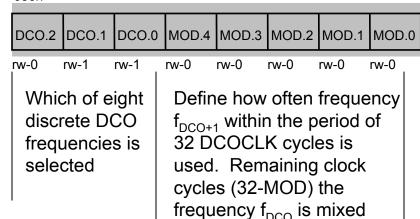

RSEL.x Select DCO nominal frequency

DCO.x and MOD.x set exact DCOCLK

.. select other clock tree options

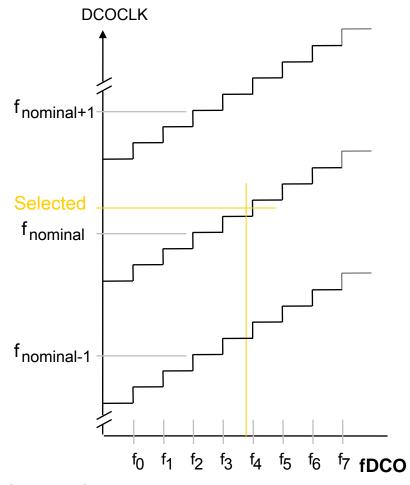

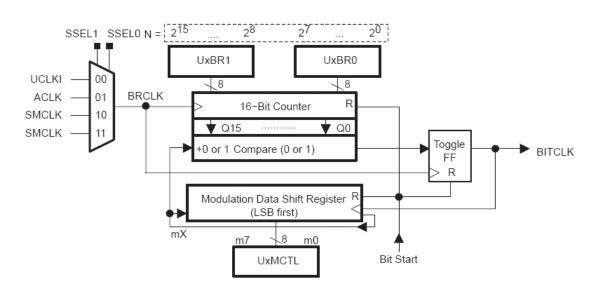

#### Digitally-Controlled Oscillator (DCO) Clock-Frequency Control

DCOCTL is loaded with a value of 060h with a valid PUC condition.

7

DCOCTL DCO.2 DCO.1 DCO.0 MOD.4 MOD.3 MOD.2 MOD.1 MOD.0

056H 0 1 1 0 0 0 0 0

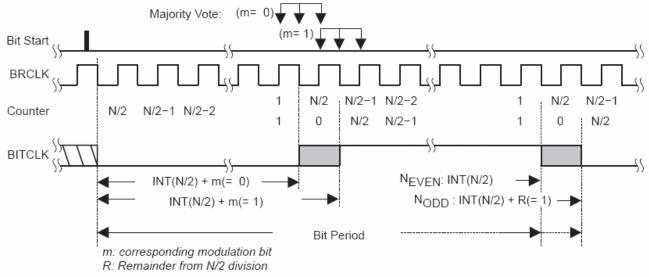

**MOD.0** .. **MOD.4**: The MOD constant defines how often the discrete frequency  $f_{DCO+1}$  is used within a period of 32 DCOCLK cycles.

During the remaining clock cycles (32–MOD) the discrete frequency f  $_{\rm DCO}$  is used. When the DCO constant is set to seven, no modulation is possible since the highest feasible frequency has then been selected.

**DCO.0** .. **DCO.2**: The DCO constant defines which one of the eight discrete frequencies is selected. The frequency is defined by the current injected into the dc generator.

Oscillator and Clock Control Register

BCSCTL1 is affected by a valid PUC or POR condition.

7

BCSCTL1 XT2Off XTS DIVA.1 DIVA.0 XT5V Rsel.2 Rsel.1 Rsel.0

057h 1 0 0 0 1 0 0

Bit0 to Bit2: The internal resistor is selected in eight different steps.

Rsel.0 to Rsel.2 The value of the resistor defines the nominal frequency.

The lowest nominal frequency is selected by setting Rsel=0.

Bit3, XT5V: XT5V should always be reset.

**Bit4 to Bit5**: The selected source for ACLK is divided by:

DIVA = 0: 1

DIVA = 1: 2

DIVA = 2: 4

DIVA = 3: 8

## BCSCTL1

**Bit6, XTS**: The LFXT1 oscillator operates with a low-frequency or with a high-frequency crystal:

XTS = 0: The low-frequency oscillator is selected.

XTS = 1: The high-frequency oscillator is selected.

The oscillator selection must meet the external crystal's operating condition.

Bit7, XT2Off: The XT2 oscillator is switched on or off:

XT2Off = 0: the oscillator is on

XT2Off = 1: the oscillator is off if it is not used for MCLK or SMCLK.

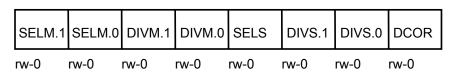

#### **BCSCTL2** is affected by a valid PUC or POR condition.

7

**BCSCTL2** SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR 058h

**Bit0**, **DCOR**: The DCOR bit selects the resistor for injecting current into the dc generator. Based on this current, the oscillator operates if activated.

DCOR = 0: Internal resistor on, the oscillator can operate. The fail-safe mode is on.

DCOR = 1: Internal resistor off, the current must be injected externally if the DCO output drives any clock using the DCOCLK.

Bit1, Bit2: The selected source for SMCLK is divided by:

DIVS.1 .. DIVS.0 DIVS = 0:1

DIVS = 1: 2

DIVS = 2:4

DIVS = 3:8

#### **BCSCTL2**

```

Bit3, SELS: Selects the source for generating SMCLK:

SELS = 0: Use the DCOCLK

SELS = 1: Use the XT2CLK signal (in three-oscillator systems)

or

LFXT1CLK signal (in two-oscillator systems)

Bit4, Bit5: The selected source for MCLK is divided by DIVM.0 .. DIVM.1

DIVM = 0.1

DIVM = 1: 2

DIVM = 2:4

DIVM = 3:8

Bit6, Bit7: Selects the source for generating MCLK:

SELM.0 .. SELM.1

SELM = 0: Use the DCOCLK

SELM = 1: Use the DCOCLK

SELM = 2: Use the XT2CLK (x13x and x14x devices)

or

Use the LFXT1CLK (x11x(1) devices)

SELM = 3: Use the LFXT1CLK

CPF 323

```

## Range (RSELx) and Steps (DCOx)

## F149 default DCO clock setting

| PARAMETER      | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | MIN             | NOM             | MAX             | UNIT   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|-----------------|-----------------|--------|

| PARAMETER      | R <sub>Sel</sub> = 0, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 0.08            | 0.12            | 0.15            | ONIT   |

| f(DCO03)       | NSGI - 0, DOO - 3, MOD - 0, DOOK - 0, 14 - 23 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CC</sub> = 3 V       | 0.08            | 0.12            | 0.16            | MHz    |

|                | R <sub>sel</sub> = 1, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 0.14            | 0.19            | 0.10            |        |

| f(DCO13)       | Ngal - 1, 200 - 0, 1102 - 0, 2001 - 0, 14 - 20 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>CC</sub> = 3 V       | 0.14            | 0.18            | 0.22            | MHz    |

|                | R <sub>Sel</sub> = 2, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 0.22            | 0.30            | 0.36            |        |

| f(DCO23)       | Sel 2, 200 0, mod 0, 200 0, 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VCC = 3 V                   | 0.22            | 0.28            | 0.34            | MHz    |

|                | R <sub>Sel</sub> = 3, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 0.37            | 0.49            | 0.59            |        |

| f(DCO33)       | , and a state of the state of t | V <sub>CC</sub> = 3 V       | 0.37            | 0.47            | 0.56            | MHz    |

| f(DCO43)       | R <sub>Sel</sub> = 4, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 0.61            | 0.77            | 0.93            |        |

|                | 301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>CC</sub> = 3 V       | 0.61            | 0.75            | 0.90            | MHz    |

| _              | R <sub>sel</sub> = 5, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 1               | 1.2             | 1.5             |        |

| f(DCO53)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCC = 3 V                   | 1               | 1.3             | 1.5             | MHz    |

| 4              | R <sub>Sel</sub> = 6, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 1.6             | 1.9             | 2.2             |        |

| f(DCO63)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>CC</sub> = 3 V       | 1.69            | 2.0             | 2.29            | MHz    |

| 4              | R <sub>sel</sub> = 7, DCO = 3, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 2.4             | 2.9             | 3.4             |        |

| f(DCO73)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCC = 3 V                   | 2.7             | 3.2             | 3.65            | MHz    |

| f(DCO47)       | R <sub>Sel</sub> = 4, DCO = 7, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V/3 V | fDCO40<br>× 1.7 | fDCO40<br>× 2.1 | fDCO40<br>× 2.5 | MHz    |

| 6              | R <sub>Sel</sub> = 7, DCO = 7, MOD = 0, DCOR = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = 2.2 V     | 4               | 4.5             | 4.9             | MHz    |

| f(DCO77)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VCC = 3 V                   | 4.4             | 4.9             | 5.4             | IVITIZ |

| S(Rsel)        | SR = fRsel+1 / fRsel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>CC</sub> = 2.2 V/3 V | 1.35            | 1.65            | 2               |        |

| S(DCO)         | S <sub>DCO</sub> = f <sub>DCO+1</sub> / f <sub>DCO</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>CC</sub> = 2.2 V/3 V | 1.07            | 1.12            | 1.16            |        |

| Dt             | Temperature drift, R <sub>Sel</sub> = 4, DCO = 3, MOD = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>CC</sub> = 2.2 V     | -0.31           | -0.36           | -0.40           | %/°C   |

|                | (see Note 30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VCC = 3 V                   | -0.33           | -0.38           | -0.43           |        |

| D <sub>V</sub> | Drift with V <sub>CC</sub> variation, R <sub>Sel</sub> = 4, DCO = 3, MOD = 0 (see Note 30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>CC</sub> = 2.2 V/3 V | 0               | 5               | 10<br>052.72    | %/V    |

CPE 323 3/432726/page 40

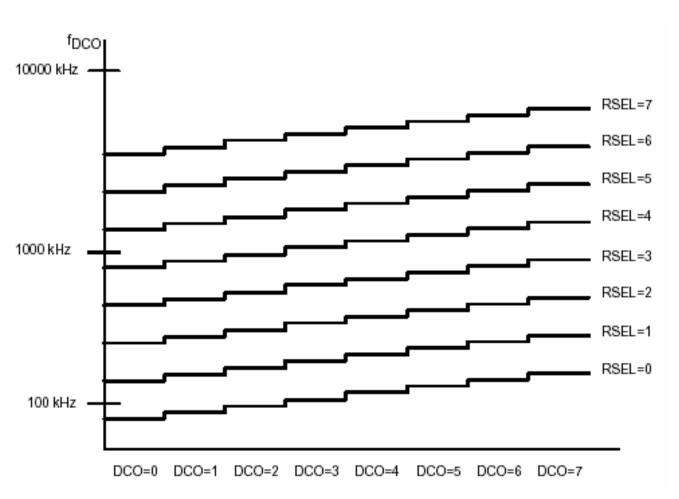

- The DCO temperature coefficient can be reduced by using an external resistor ROSC to source the current for the DC generator.

- ROSC also allows the DCO to operate at higher frequencies.

- Internal resistor nominal value is approximately 200 kOhm

DCO to operate up to 5 MHz.

- External ROSC of approximately 100 kOhm => the DCO can operate up to approximately 10 MHz.

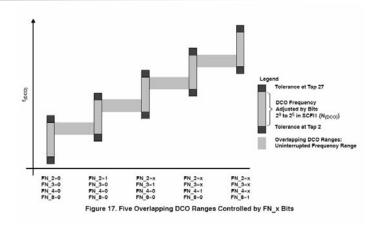

#### **Basic Clock Systems-DCO TAPS**

#### ► **UCOCLK** frequency control

- nominal injected current into DC generator

1) internal resistors Rsel2, Rsel1 and Rsel0

2) an external resistor at Rosc (P2.5/11x)

- Control bits DCO0 to DCO2 set fDCO tap

- Modulation bits MOD0 to MOD4 allow mixing of fDCO and fDCO+1 for precise frequency generation

| Example   | Frequency | Cycle time |  |  |

|-----------|-----------|------------|--|--|

| Selected: | 1000kHz   | 1000 nsec  |  |  |

| f3:       | 943kHz    | 1060 nsec  |  |  |

| f4:       | 1042kHz   | 960 nsec   |  |  |

| MOD=19    |           |            |  |  |

To produce an intermediate effective frequency between  $f_{DCO}$  and  $f_{DCO+1}$  Cycle\_time = ((32-MOD)\* $t_{DCO}$ +MOD\* $t_{DCO+1}$ )/32 = 1000.625 ns, selected frequency  $\approx$  1 MHz.

**CPE 323**

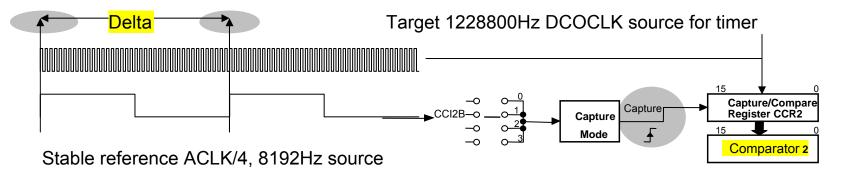

### **Software FLL**

- Basic Clock DCO is an open loop close with SW+HW

- ❖ A reference frequency e.g. ACLK or 50/60Hz can be used to measure DCOCLK's

- ❖ <u>Initialization or Periodic</u> software set and stabilizes DCOCLK over reference clock

- DCOCLK is programmable 100kHz 5Mhz and stable over voltage and temperature

## **Software FLL Implementation**

- Example: Set DCOCLK= 1228800, ACLK= 32768

- ACLK/4 captured on CCI2B, DCOCLK is clock source for Timer\_A

- Comparator2 HW captures SMCLK (1228800Hz) in one ACLK/4 (8192Hz) period

- Target Delta = 1228800/8192= 150

```

CCI2BInt ...

; Compute Delta

#150,Delta

; Delta= 1228800/8192

cmp

ilo

IncDCO

; JMP to IncDCO

DecDCO dec

&DCOCTL

; Decrease DCOCLK

reti

IncDCO inc

&DCOCTL

; Increase DCOCLK

reti

```

- Basic module incorporates an oscillator-fault detection fail-safe feature.

- The oscillator fault detector is an analog circuit that monitors the LFXT1CLK (in HF mode) and the XT2CLK.

- An oscillator fault is detected when either clock signal is not present for approximately 50 us.

- When an oscillator fault is detected, and when MCLK is sourced from either LFXT1 in HF mode or XT2, MCLK is automatically switched to the DCO for its clock source.

- When OFIFG is set and OFIE is set, an NMI interrupt is requested. The NMI interrupt service routine can test the OFIFG flag to determine if an oscillator fault occurred. The OFIFG flag must be cleared by software.

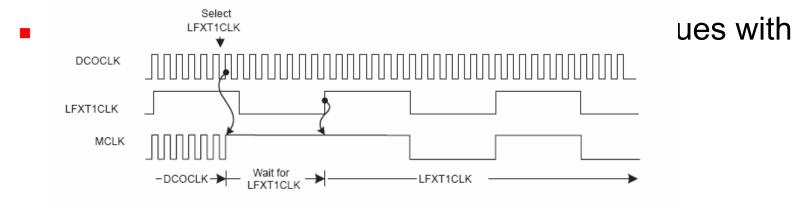

- When switching MCLK and SMCLK from one clock source to another

- => avoid race conditions

- The current clock cycle continues until the next rising edge

- The clock remains high until the next rising edge of Figure 4-11. Switch MCLK from DCOCLK to LFXT1CLK

# 1

## **Basic Clock Module - Examples**

#### How to select the Crystal Clock

## **Basic Clock Systems-Examples**

#### Adjusting the Basic Clock

The control registers of the Basic Clock are under full software control. If clock requirements other than those of the default from PUC are necessary, the Basic Clock can be configured or reconfigured by software at any time during program execution.

- ACLKGEN from LFXT1 crystal, resonator, or external-clock source and divided by 1, 2, 4, or 8. If no LFXTCLK clock signal is needed in the application, the OscOff bit should be set in the status register.

- □ SCLKGEN from LFXTCLK, DCOCLK, or XT2CLK (x13x and x14x only) and divided by 1, 2, 4, or 8. The SCG1 bit in the status register enables or disables SMCLK.

- ☐ MCLKGEN from LFXTCLK, DCOCLK, or XT2CLK (x13x and x14x only) and divided by 1, 2, 4, or 8. When set, the CPUOff bit in the status register enables or disables MCLK.

- □ DCOCLK frequency is adjusted using the RSEL, DCO, and MOD bits. The DCOCLK clock source is stopped when not used, and the dc generator can be disabled by the SCG0 bit in the status register (when set).

- ☐ The XT2 oscillator sources XT2CLK (x13x and x14x only) by clearing the XT2Off bit.

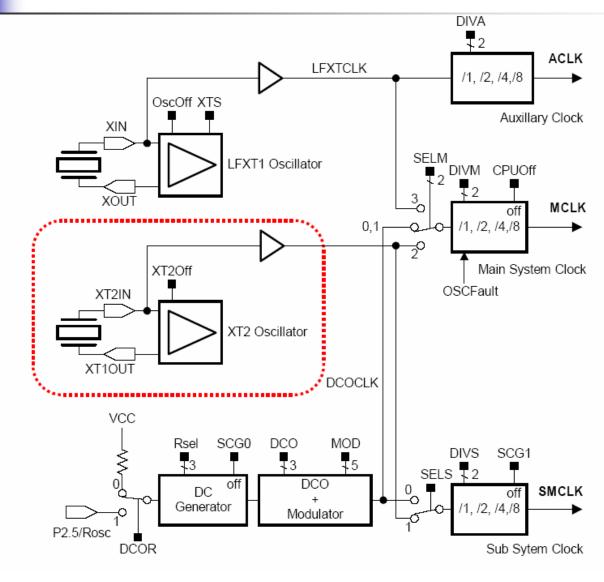

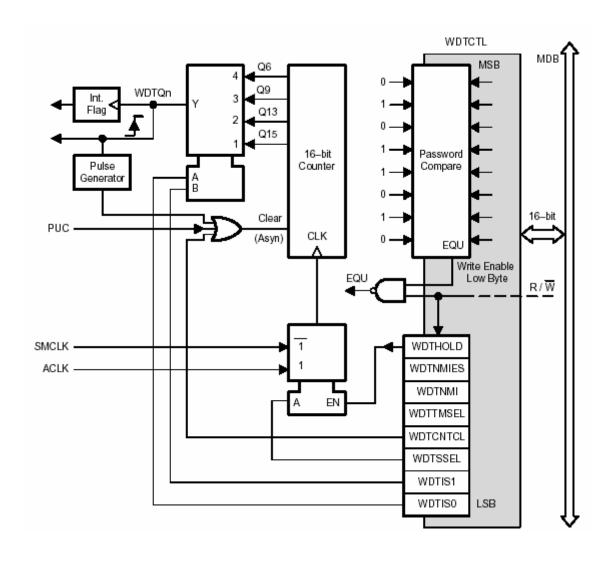

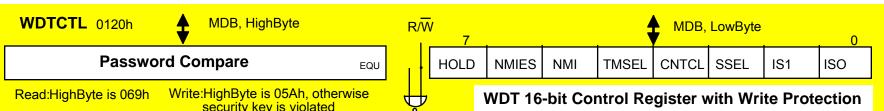

## FLL+ Clock Module (MSP430x4xx)

- FLL+ clock module: frequency-locked loop clock module

- Low system cost

- Ultra-low power consumption

- Can operate with no external components

- Supports one or two external crystals or resonators (LFXT1 and XT2)

- Internal digitally-controlled oscillator with stabilization to a multiple of the LFXT1 watch crystal frequency

- Full software control over 4 output clocks: ACLK, ACLK/n, MCLK, and SMCLK

## MSP430x43x, MSP430x44x and MSP430x461x Frequency-Locked Loop

### **FLL+ Clock Module**

- LFXT1CLK: Low-frequency/high-frequency oscillator that can be used

- either with low-frequency 32768-Hz watch crystals, or

- standard crystals or resonators in the 450-kHz to 8-MHz range.

- XT2CLK: Optional high-frequency oscillator that can be used with standard crystals, resonators, or external clock sources in the 450kHz to 8-MHz range. In MSP430F47x devices the upper limit is 16 MHz.

- DCOCLK: Internal digitally controlled oscillator (DCO) with RC-type characteristics, stabilized by the FLL.

- Four clock signals are available from the FLL+ module:

- ACLK: Auxiliary clock. The ACLK is the LFXT1CLK clock source. ACLK is software selectable for individual peripheral modules.

- ACLK/n: Buffered output of the ACLK. The ACLK/n is ACLK divided by 1,2,4 or 8 and only used externally.

- MCLK: Master clock. MCLK is software selectable as LFXT1CLK, XT2CLK (if available), or DCOCLK. MCLK can be divided by 1, 2, 4, or 8 within the FLL block. MCLK is used by the CPU and system.

- SMCLK: Sub-main clock. SMCLK is software selectable as XT2CLK (if available), or DCOCLK. SMCLK is software selectable for individual peripheral modules.

## **FLL+ Clock Module Operation**

- After a PUC, MCLK and SMCLK are sourced from DCOCLK at 32 times the ACLK frequency. When a 32,768-Hz crystal is used for ACLK, MCLK and SMCLK will stabilize to 1,048576 MHz.

- Status register control bits SCG0, SCG1, OSCOFF, and CPUOFF configure the MSP430 operating modes and enable or disable components of the FLL+ clock module.

- The SCFQCTL, SCFI0, SCFI1, FLL\_CTL0, and FLL\_CTL1 registers configure the FLL+ clock module. The FLL+ can be configured or reconfigured by software at any time during program execution.

- Example, MCLK = 64 × ACLK = 2097152

```

BIC #GIE, SR; Disable interrupts

MOV.B #(64-1), &SCFQTL; MCLK = 64 * ACLK, DCOPLUS=0

MOV.B #FN_2, &SCFIO; Select DCO range

BIS #GIE, SR; Enable interrupts

```

## **LFXT1 Oscillator**

- Low-frequency (LF) mode (XTS\_FLL=0) with 32,768 Hz watch crystal connected to XIN and XOUT

- High-frequency (HF) mode (XTS\_FLL=1) with high-frequency crystals or resonators connected to XIN and XOUT (~450 KHz to 8 MHz)

- XCPxPF bits configure the internally provided load capacitance for the LFXT1 crystal (1, 6, 8, or 10 pF)

- OSCOFF bit can be set to disable LFXT1

### **XT2 Oscillator**

- XT2 sources XT2CLK and its characteristics are identical to LFXT1 in HF mode, except it does not have internal load capacitors (must be provided externally)

- XT2OFF bit disables the XT2 oscillator if XT2CLK is not used for MCLK and SMCLK

## DCO

- Integrated ring oscillator with RC-type characteristics

- DCO frequency is stabilized by the FLL to a multiple of ACLK as defined by N (the lowest 7 bits of the SCFQCTL register)

- DCOPLUS bit sets the f<sub>DCOCLK</sub> to f<sub>DCO</sub> or f<sub>DCO/D</sub> (divider). The FLLDx bits define the divider D to 1, 2, 4 or 8. By default DCOPLUS=0 and D=2, providing f<sub>DCOCLK</sub>= f<sub>DCO/2</sub>

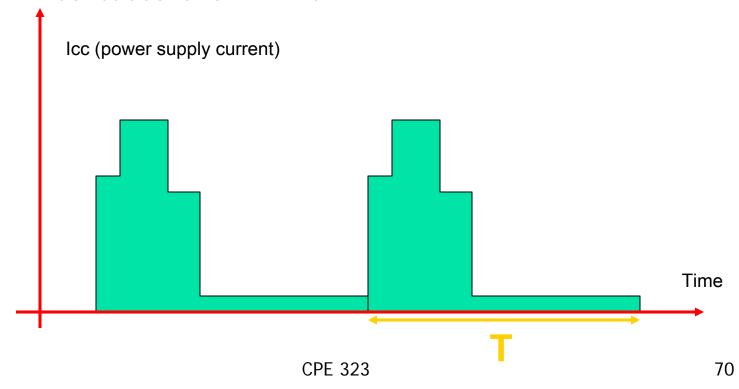

- DCOPLUS = 0:  $f_{DCOCLK} = (N + 1) \times f_{ACLK}$