# CPE/EE 427, CPE 527 VLSI Design I L15: Power and Designing for Low Power

Department of Electrical and Computer Engineering

University of Alabama in Huntsville

Aleksandar Milenkovic ( <a href="www.ece.uah.edu/~milenka">www.ece.uah.edu/~milenka/cpe527-05F</a>

### **Why Power Matters**

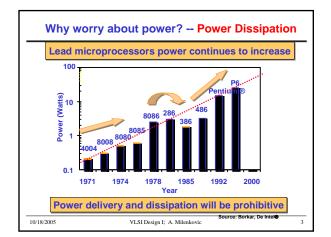

- · Packaging costs

- · Power supply rail design

- · Chip and system cooling costs

- · Noise immunity and system reliability

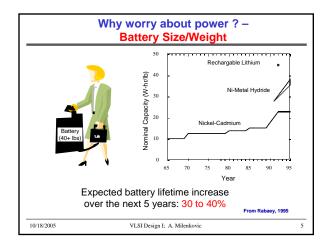

- Battery life (in portable systems)

- · Environmental concerns

- Office equipment accounted for 5% of total US commercial energy usage in 1993

- Energy Star compliant systems

10/18/2005

VLSI Design I; A. Milenkovic

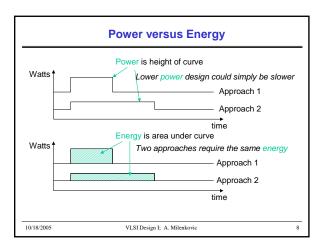

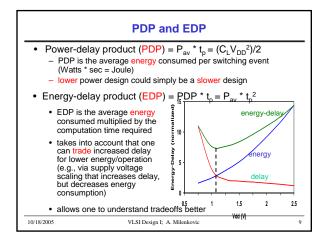

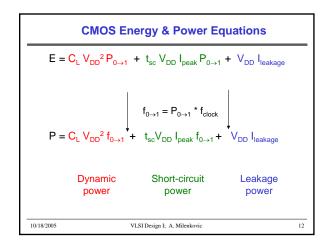

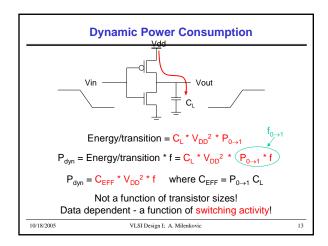

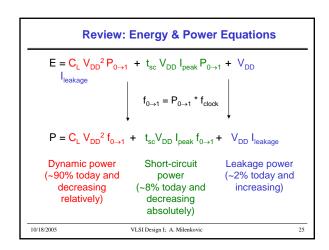

# Power and Energy Figures of Merit Power consumption in Watts determines battery life in hours Peak power determines power ground wiring designs sets packaging limits impacts signal noise margin and reliability analysis Energy efficiency in Joules rate at which power is consumed over time Energy = power \* delay Joules = Watts \* seconds lower energy number means less power to perform a computation at the same frequency

|                                       | CL018<br>G | CL018<br>LP | CL018<br>ULP | CL018<br>HS | CL015<br>HS | CL013<br>HS |

|---------------------------------------|------------|-------------|--------------|-------------|-------------|-------------|

| $V_{dd}$                              | 1.8 V      | 1.8 V       | 1.8 V        | 2 V         | 1.5 V       | 1.2 V       |

| T <sub>ox</sub> (effective)           | 42 Å       | 42 Å        | 42 Å         | 42 Å        | 29 Å        | 24 Å        |

| L <sub>gate</sub>                     | 0.16 μm    | 0.16 μm     | 0.18 μm      | 0.13 μm     | 0.11 μm     | 0.08 μm     |

| I <sub>DSat</sub> (n/p)<br>(μΑ/μm)    | 600/260    | 500/180     | 320/130      | 780/360     | 860/370     | 920/400     |

| I <sub>off</sub> (leakage)<br>(ρΑ/μm) | 20         | 1.60        | 0.15         | 300         | 1,800       | 13,000      |

| V <sub>Tn</sub>                       | 0.42 V     | 0.63 V      | 0.73 V       | 0.40 V      | 0.29 V      | 0.25 V      |

| FET Perf.<br>(GHz)                    | 30         | 22          | 14           | 43          | 52          | 80          |

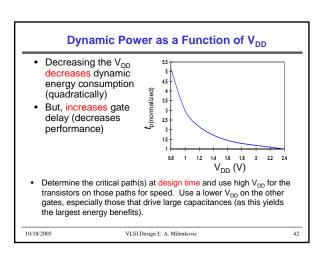

# **Dynamic Power as a Function of Device Size** Device sizing affects dynamic energy consumption gain is largest for networks with large overall effective fan-outs (F = $C_{\rm L}/C_{\rm g,1}$ ) · The optimal gate sizing factor (f) for dynamic energy is smaller than the one for performance, especially for large F's - e.g., for F=20, $f_{opt}(energy) = 3.53$ while $f_{opt}(performance) = 4.47$ · If energy is a concern avoid oversizing beyond the optimal 10/18/2005 VLSI Design I; A. Milenkovic

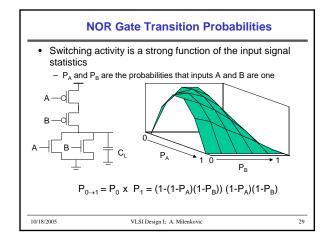

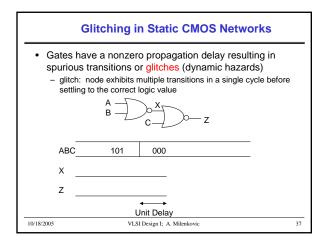

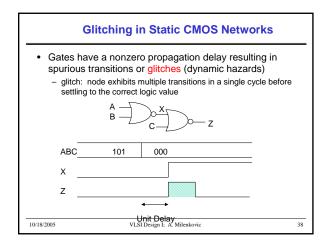

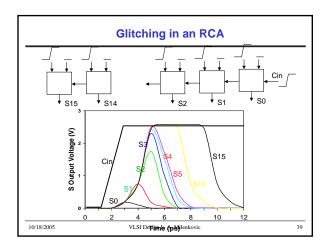

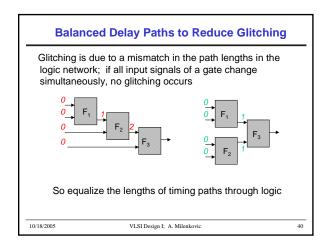

**Dynamic Power Consumption is Data Dependent** Switching activity,  $P_{0\rightarrow 1}$ , has two components A static component – function of the logic topology - A dynamic component - function of the timing behavior (glitching) Static transition probability  $P_{0\to 1} = P_{\text{out}=0} \times P_{\text{out}=1}$ 2-input NOR Gate  $= P_0 \times (1-P_0)$ With input signal probabilities 0  $P_{A=1} = 1/2$  $P_{B=1} = 1/2$ 0 0 NOR static transition probability  $= 3/4 \times 1/4 = 3/16$ VLSI Design I; A. Milenkovic

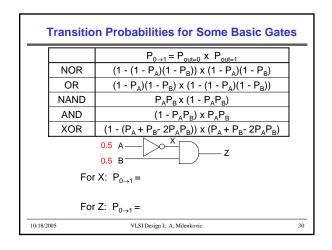

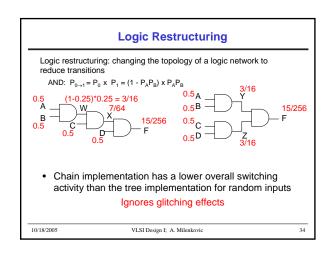

### **Transition Probabilities for Some Basic Gates** $P_{0\rightarrow 1} = P_{out=0} x P_{out=1}$ (1 - (1 - P<sub>A</sub>)(1 - P<sub>B</sub>)) x (1 - P<sub>A</sub>)(1 - P<sub>B</sub>) NOR $(1 - P_A)(1 - P_B) \times (1 - (1 - P_A)(1 - P_B))$ OR NAND $P_A P_B x (1 - P_A P_B)$ AND $(1 - P_A P_B) \times P_A P_B$ XOR $(1 - (P_A + P_{B^-} 2P_A P_B)) \times (P_A + P_{B^-} 2P_A P_B)$ For X: $P_{0\to 1} = P_0 x P_1 = (1-P_A) P_A$ For Z: $P_{0\to 1} = P_0 \times P_1 = (1-P_X P_B) P_X P_B$ $= (1 - (0.5 \times 0.5)) \times (0.5 \times 0.5) = 3/16$ VLSI Design I; A. Milenkovic 10/18/2005

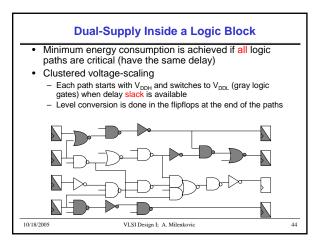

### Multiple V<sub>DD</sub> Considerations

- How many V<sub>DD</sub>? Two is becoming common

- Many chips already have two supplies (one for core and one for I/O)

- When combining multiple supplies, level converters are required whenever a module at the lower supply drives a gate at the higher supply (step-up)

- If a gate supplied with V<sub>DDL</sub> drives a gate at V<sub>DDH</sub>, the PMOS never turns off

- The cross-coupled PMOS transistors do the level conversion

- The NMOS transistor operate on a reduced supply

- Level converters are not needed for a step-down change in voltage

- Overhead of level converters can be mitigated by doing conversions at register boundaries and embedding the level conversion inside the flipflop

10/18/2005

VLSI Design I; A. Milenkovic

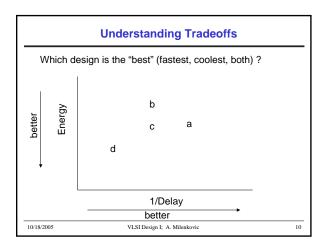

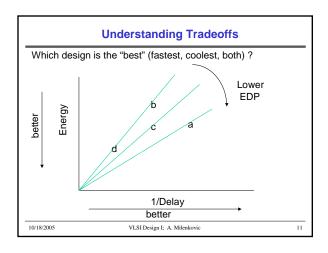

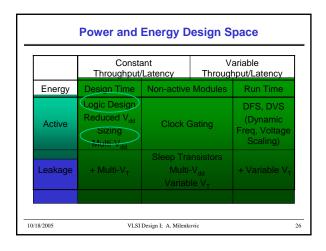

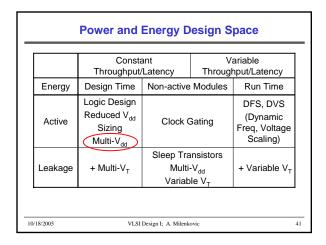

# **Power and Energy Design Space**

|         | Consta<br>Throughput/                                             |                                                                       | Variable<br>Throughput/Latency |                                                   |  |

|---------|-------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------|---------------------------------------------------|--|

| Energy  | Design Time                                                       | ne Non-active Modules                                                 |                                | Run Time                                          |  |

| Active  | Logic Design Reduced V <sub>dd</sub> Sizing Multi-V <sub>dd</sub> | Clock Gating                                                          |                                | DFS, DVS<br>(Dynamic<br>Freq, Voltage<br>Scaling) |  |

| Leakage | + Multi-V <sub>T</sub>                                            | Sleep Transistors<br>Multi-V <sub>dd</sub><br>Variable V <sub>⊤</sub> |                                | + Variable V <sub>T</sub>                         |  |

10/18/2005

VLSI Design I; A. Milenkovic

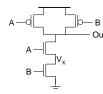

### **Stack Effect**

Leakage is a function of the circuit topology and the value of the inputs

| Α | В | V <sub>x</sub>         | I <sub>SUB</sub>                    |

|---|---|------------------------|-------------------------------------|

| 0 | 0 | V <sub>T</sub> ln(1+n) | $V_{GS}=V_{BS}=-V_X$                |

| 0 | 1 | 0                      | V <sub>GS</sub> =V <sub>BS</sub> =0 |

| 1 | 0 | $V_{DD}$ - $V_{T}$     | V <sub>GS</sub> =V <sub>BS</sub> =0 |

| 1 | 1 | 0                      | V <sub>SG</sub> =V <sub>SB</sub> =0 |

- Leakage is least when A = B = 0

- Leakage reduction due to stacked transistors is called the stack effect

10/18/2005

45

47

VLSI Design I; A. Milenkovic

### **Short Channel Factors and Stack Effect**

- In short-channel devices, the subthreshold leakage current depends on V<sub>GS</sub>, V<sub>BS</sub> and V<sub>DS</sub>. The V<sub>T</sub> of a short-channel device decreases with increasing V<sub>DS</sub> due to DIBL (drain-induced barrier loading).

- Typical values for DIBL are 20 to 150mV change in V<sub>T</sub> per voltage change in V<sub>Ds</sub> so the stack effect is even more significant for short-channel devices.

- $\rm V_X$  reduces the drain-source voltage of the top nfet, increasing its  $\rm V_T$  and lowering its leakage

- For our 0.25 micron technology, V<sub>X</sub> settles to ~100mV in steady state so V<sub>BS</sub> = -100mV and V<sub>DS</sub> = V<sub>DD</sub> -100mV which is 20 times smaller than the leakage of a device with V<sub>BS</sub> = 0mV and V<sub>DS</sub> = V<sub>DD</sub>

10/18/2005

VLSI Design I; A. Milenkovic

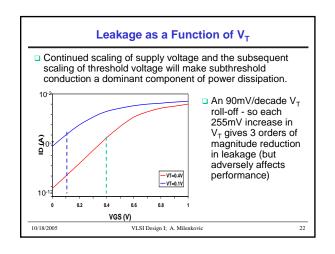

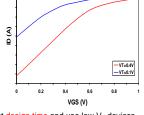

### Leakage as a Function of Design Time V<sub>T</sub>

- Reducing the V<sub>T</sub> increases the subthreshold leakage current (exponentially)

- 90mV reduction in V<sub>T</sub> increases leakage by an order of magnitude

- But, reducing V<sub>T</sub>

decreases gate delay

(increases

performance)

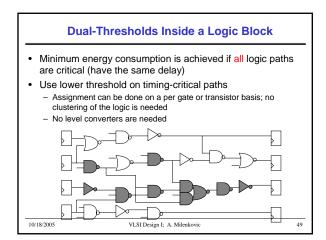

- Determine the critical path(s) at design time and use low V<sub>T</sub> devices on the transistors on those paths for speed. Use a high V<sub>T</sub> on the other logic for leakage control.

- A careful assignment of V<sub>T</sub>'s can reduce the leakage by as much as 80%

10/18/2005

VLSI Design I; A. Milenkovic