## Outline

## ➢ Introduction

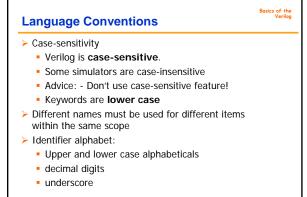

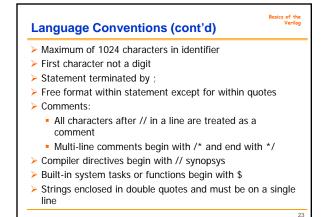

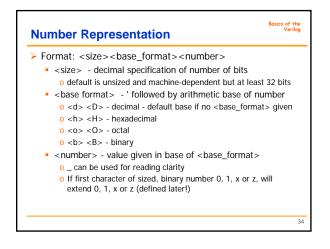

- > Basics of the Verilog Language

- Operators

- Hierarchy/Modules

- Procedures and Assignments

- Timing Controls and Delay

- Control Statement

- Logic-Gate Modeling

- Modeling Delay

- > Other Verilog Features

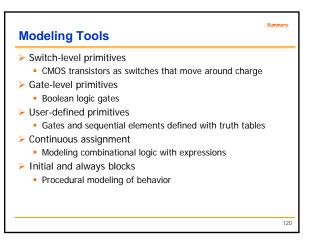

- Summary

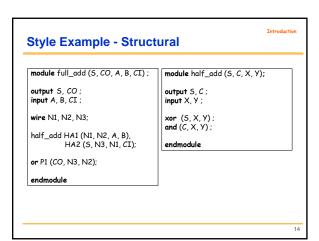

## **Styles**

Structural - instantiation of primitives and modules

Introduction

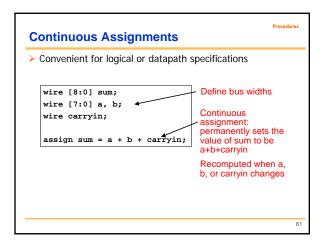

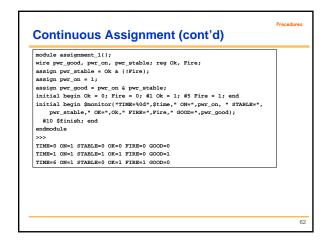

- RTL/Dataflow continuous assignments

- Behavioral procedural assignments

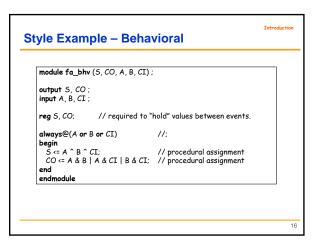

## **Behavioral Modeling**

- > A much easier way to write testbenches

- > Also good for more abstract models of circuits

- Easier to write

- Simulates faster

- > More flexible

- Provides sequencing

- Verilog succeeded in part because it allowed both the model and the testbench to be described together

| module fa_rtl (S, CO, A, B, CI) ;                              |                                                    |  |

|----------------------------------------------------------------|----------------------------------------------------|--|

| output S, CO ;<br>input A, B, CI ;                             |                                                    |  |

| assign S = A ^ B ^ CI;<br>assign CO = A & B   A & CI   B & CI; | //continuous assignment<br>//continuous assignment |  |

| endmodule                                                      |                                                    |  |

## How Verilog Is Used Virtually every ASIC is designed using either Verilog or VHDL (a similar language) Behavioral modeling with some structural elements "Synthesis subset" Can be translated using Synopsys' Design Compiler or others into a netlist Design written in Verilog Simulated to death to check functionality Synthesized (netlist generated) Static timing analysis to check timing

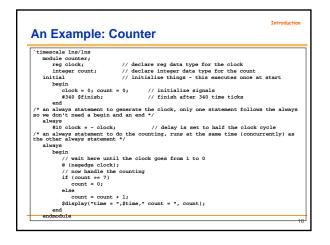

| An I | Example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Count                                                                                                                       | er (co                                                                               | nt'd)                                          | Introduction |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------|--------------|

|      | rilog using N<br>Assume working of<br>Invoke <u>ModelSim</u><br>Change Directory.<br>Copy file counter.<br>Create a design II<br>Compile counter.<br>Start the simulatio<br>Run the simulatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tirectory: cpe<br>to cpe626/Vie<br>v to the work<br>brary: <i>vlib wc</i><br><i>v: vlog counte</i><br>vr: <i>vsim count</i> | ogExamples/<br>ing directory<br>ork<br>er. v<br>ter                                  | Counter                                        | r            |

|      | <pre>&gt; run 200 # time = # time</pre> | 20<br>40<br>60<br>100<br>120<br>140<br>160<br>180                                                                           | count =<br>count =<br>count =<br>count =<br>count =<br>count =<br>count =<br>count = | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>0<br>1<br>2 |              |

|      | u da                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                             |                                                                                      |                                                | 15           |

## Outline

## Introduction

- ➢ Basics of the Verilog Language

- Operators

- Hierarchy/Modules

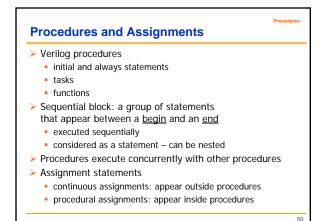

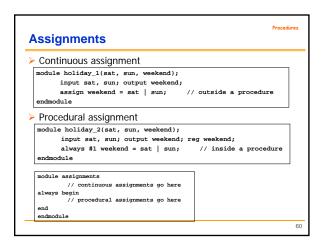

- Procedures and Assignments

- Timing Controls and Delay

- Control Statement

- ➢ Logic-Gate Modeling

- Modeling Delay

- > Other Verilog Features

- Summary

20

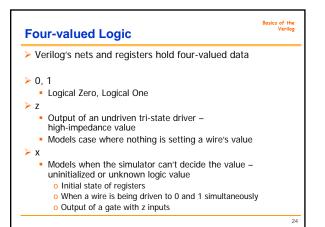

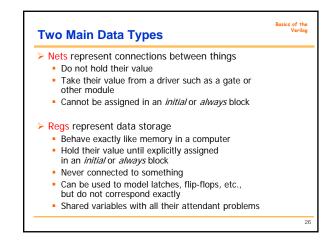

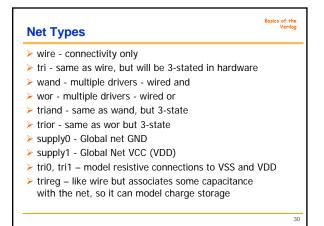

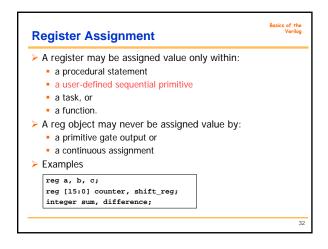

## Data Types > nets are further divided into several net types wire, tri, supply0, ... > registers - stores a logic value - reg > integer - supports computation > time - stores time 64-bit unsigned > real - stores values as real num > realtime - stores time values as real numbers > event - an event data type

| odule declarations_1;                |                                                           |

|--------------------------------------|-----------------------------------------------------------|

| wire pwr_good,pwr_on,pw              | r_stable; // Explicitly declare wires                     |

| integer i;                           | <pre>// 32-bit, signed (2's complement)</pre>             |

| time t;                              | <pre>// 64-bit, unsigned, behaves like a 64-bit reg</pre> |

| event e;                             | // Declare an event data type                             |

| real r;                              | // Real data type of implementation defined size          |

| // assign statement con              | tinuously drives a wire                                   |

| assign pwr_stable = 1'b              | l; assign pwr_on = l; // l or l'bl                        |

| assign pwr_good = pwr_o              | 1 & pwr_stable;                                           |

| initial begin                        |                                                           |

| <pre>\$display("pwr_on=",pwr_</pre>  | ; (nc                                                     |

| i = 123.456;                         | // There must be a digit on either side                   |

| r = 123456e-3;                       | <pre>// of the decimal point if it is present.</pre>      |

| t = 123456e-3;                       | // Time is rounded to 1 second by default.                |

| \$display("i=%0g",i," t=             | <pre>k6.2f",t," r=%f",r);</pre>                           |

| <pre>#2 \$display("TIME=%0d",:</pre> | <pre>\$time," ON=",pwr_on,</pre>                          |

| " STABLE=",pwr_stable                | e," GOOD=",pwr_good);                                     |

| end                                  |                                                           |

| ndmodule                             |                                                           |

| -                                    |                                                           |

| pwr_on=x                             |                                                           |

|                                      | 000                                                       |

| Constants                                                                                                 |                                     |   |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------|---|

| parameter A = 2'b00, B = 2'b01,                                                                           | C = 2'b10;                          | 1 |

| parameter regsize = 8;                                                                                    |                                     |   |

| reg [regsize - 1:0]; /* illu                                                                              | strates use of parameter regsize */ |   |

| <ul> <li>Strings</li> <li>No explicit data type</li> </ul>                                                |                                     |   |

| <ul><li>No explicit data type</li><li>Must be stored in reg (or</li></ul>                                 | 5.                                  | 7 |

| <ul> <li>No explicit data type</li> <li>Must be stored in reg (or</li> <li>reg [255:0] buffer;</li> </ul> | //stores 32 characters              | ] |

| <ul><li>No explicit data type</li><li>Must be stored in reg (or</li></ul>                                 | 5.                                  | ] |

| <ul> <li>Examples:</li> <li>6'b010_111</li> <li>8'b0110</li> <li>4'bx01</li> <li>16'H3AB</li> <li>24</li> <li>5'036</li> </ul> | gives 010111<br>gives 00000110<br>gives xx01<br>gives 0000001110101011<br>gives 00011000<br>gives 11100 |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| <ul><li>16'Hx</li><li>8'hz</li></ul>                                                                                           | gives xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                                              |  |

## Outline Introduction Basics of the Verilog Language Operators Hierarchy/Modules Procedures and Assignments Timing Controls and Delay Control Statement Logic-Gate Modeling Modeling Delay Other Verilog Features Summary

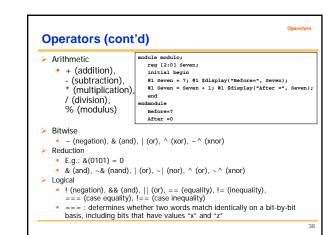

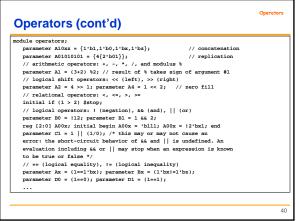

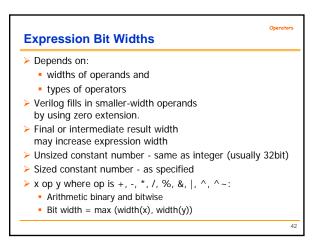

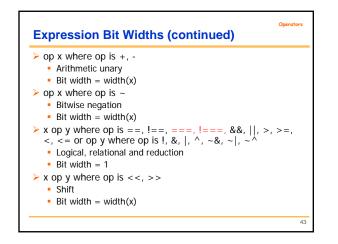

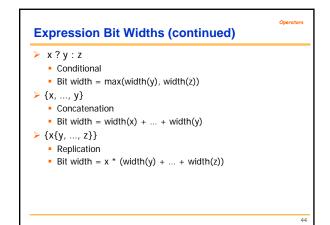

## Operators

- Arithmetic (pair of operands, binary word) [binary: +, -,\*,/,%\*]; [unary: +, -]

- Bitwise (pair of operands, binary word) [~, &, |,^,~^,^~]

- > Reduction (single operand, bit)  $[\&, \sim\&, |, \sim|, \land, \sim\land, \land\sim]$

Operators

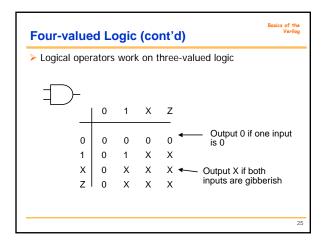

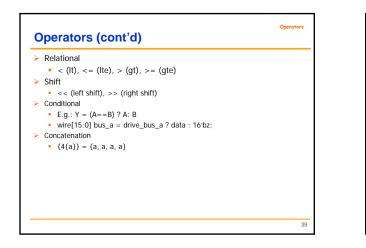

- Logical (pair of operands, boolean value) [!,&&,||,==,!=,===,!==]

- Relational (pair of operands, boolean value) [<,<=,>,>=]

- > Shift (single operand, binary word) [>>,<<]

- > Conditional ? : (three operands, expression)

- Concatenation and Replications {,} {int{ }}

- \* unsupported for variables

| Decretors (cont'd)                                     | Operato            |

|--------------------------------------------------------|--------------------|

| Operators (cont'd)                                     |                    |

|                                                        |                    |

| parameter D0 = (1==0); parameter D1 = (1==1)           | ;                  |

| <pre>// === case equality, !== (case inequality)</pre> |                    |

| // case operators only return true or false            |                    |

| parameter E0 = (1===1'bx); parameter E1 = 4            | b01xz === 4'b01xz; |

| parameter F1 = (4'bxxxx === 4'bxxxx);                  |                    |

| <pre>// bitwise logical:</pre>                         |                    |

| // ~ (negation), & (and),   (inclusive or),            |                    |

| // ^ (exclusive or), ~^ or ^~ (equivalence)            |                    |

| parameter A00 = 2'b01 & 2'b10;                         |                    |

| <pre>// unary logical reduction:</pre>                 |                    |

| // & (and), ~& (nand),   (or), ~  (nor),               |                    |

| // ^ (xor), ~^ or ^~ (xnor)                            |                    |

| parameter G1= & 4'b1111;                               |                    |

| <pre>// conditional expression x = a ? b : c</pre>     |                    |

| <pre>// if (a) then x = b else x = c</pre>             |                    |

| reg H0, a, b, c; initial begin a=1; b=0; c=1           | L; H0=a?b:c; end   |

| reg[2:0] J01x, Jxxx, J01z, J011;                       |                    |

| initial begin Jxxx = 3'bxxx; J01z = 3'b01z;            | J011 = 3'b011;     |

| J01x = Jxxx ? J01z : J011; end                         | // bitwise result  |

|                                                        |                    |

## **Expressions with Operands** Containing x or z Arithmetic

0

47

- If any bit is x or z, result is all x's.

- Divide by 0 produces all x's.

- Relational

- If any bit is x or z, result is x.

- Logical

- = = and != If any bit is x or z, result is x.

- === and !== All bits including x and z values must match for equality

## **Expressions with Operands** One Containing x or z (cont'd) Bitwise Defined by tables for 0, 1, x, z operands. Reduction Defined by tables as for bitwise operators. Shifts z changed to x. Vacated positions zero filled.

- Conditional

- If conditional expression is ambiguous (e.g., x or z), both expressions are evaluated and bitwise combined as follows: f(1,1) = 1, f(0,0) = 0, otherwise x.

46

Modules

## Outline

- Introduction

- Basics of the Verilog Language

- > Operators

- Hierarchy/Modules

- Procedures and Assignments

- Timing Controls and Delay

- Control Statement

- Logic-Gate Modeling

- Modeling Delay

- Other Verilog Features

- > Summary

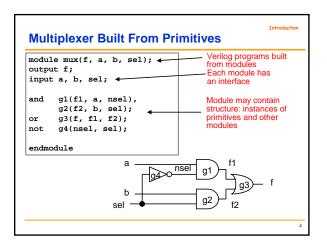

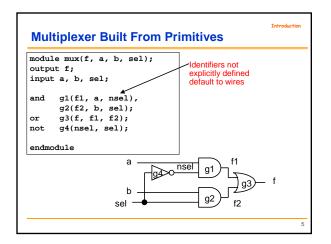

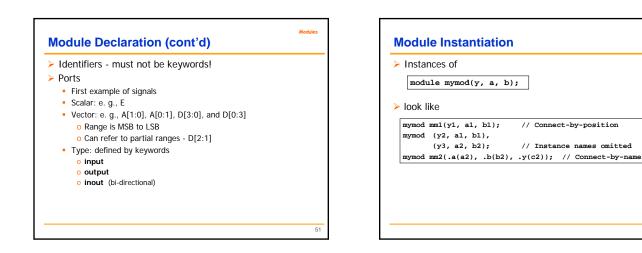

**Modules** Basic design units Verilog program build from modules with I/O interfaces Modules are: Declared Instantiated > Module interface is defined using ports each port must be explicitly declared as one of o input (wire or other net) o output (reg or wire; can be read inside the module) o inout (wire or other net) Modules declarations cannot be nested > Modules may contain instances of other modules Modules contain local signals, etc. > Module configuration is static and all run concurrently 48

## **Module Declaration**

> Basic structure of a Verilog module:

module mymod(output1, output2, ... input1, input2); output output1; output [3:0] output2; input input1; input [2:0] input2;

endmodule

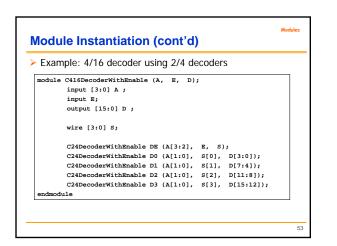

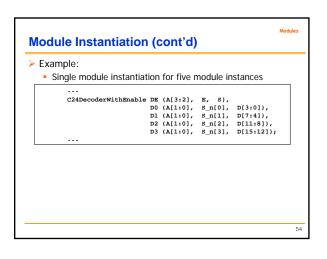

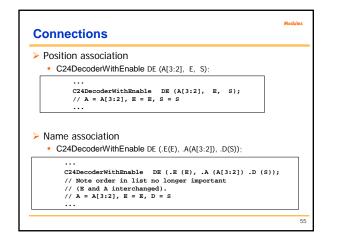

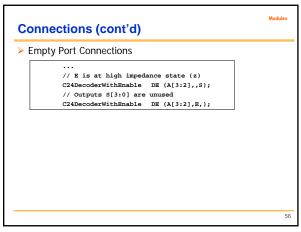

### Modules Module Declaration (cont'd) > Example: /\* module\_keyword module\_identifier (list of ports) \*/ module C24DecoderWithEnable (A, E, D); // input\_declaration input [1:0] A; // input declaration input E; output [3:0] D; // output\_declaration assign D = $\{4\{E\}\}$ & ((A == 2'b00) ? 4'b0001 : (A == 2'b01) ? 4'b0010 : (A == 2'b10) ? 4'b0100 : (A == 2'b11) ? 4'b1000 : 4'bxxxx) ; // continuous\_assign endmodule 50

Modules

| Array of Instances                                                                                                                                                                              | Outline                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| { , } is concatenate                                                                                                                                                                            | Introduction                                                                                                                                                                                      |

| > Example                                                                                                                                                                                       | <ul> <li>Basics of the Verilog Language</li> <li>Operators</li> </ul>                                                                                                                             |

| <pre>module add_array (A, B, CIN, S, COUT) ;</pre>                                                                                                                                              | Hierarchy/Modules                                                                                                                                                                                 |

| <pre>input [7:0] A, B ;<br/>input CIN ;<br/>output [7:0] S ;<br/>output COUT ;<br/>wire [7:1] carry;<br/>full_add FA[7:0] (A,B,{carry, CIN},S,{COUT, carry});<br/>// full_add is a module</pre> | <ul> <li>Procedures and Assignments</li> <li>Timing Controls and Delay</li> <li>Control Statement</li> <li>Logic-Gate Modeling</li> <li>Modeling Delay</li> <li>Other Verilog Features</li> </ul> |

| endmodule                                                                                                                                                                                       | > Summary                                                                                                                                                                                         |

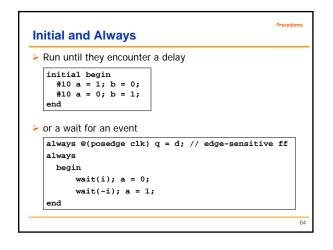

| Sequential block may appea<br>initial statement                                   | r in an always or                                                            |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| initial                                                                           | always                                                                       |

| begin                                                                             | begin                                                                        |

| imperative statements                                                             | imperative statements                                                        |

| end                                                                               | end                                                                          |

| Runs when simulation starts                                                       | Runs when simulation starts                                                  |

| Terminates when control<br>reaches the end<br>(one time sequential activity flow) | Restarts when control<br>reaches the end<br>(cycle sequential activity flow) |

| Good for providing stimulus<br>(testbenches); not synthesizable                   | Good for modeling/specifying<br>hardware                                     |

| Initial and Always (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              |                                                                               | ocedures                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------|

| <pre>module always_1; reg Y, Clk;<br/>always // Statements in an always statement execute repeatedly:<br/>begin: my_block // Start of sequential block.<br/>@(poesdge Clk) #5 Y = 1; // At +ve edge set Y=1,<br/>@(poesdge Clk) #5 Y = 0; // at the NEXT +ve edge set Y=0.<br/>end // End of sequential block.<br/>always #10 Clk = - Clk; // We need a clock.<br/>initial Y = 0; // These initial statements execute<br/>initial Clk = 0; // only once, but first.<br/>initial #0; finish;<br/>endmodule</pre> | T=10<br>T=15<br>T=20<br>T=30<br>T=35<br>T=40<br>T=50<br>T=55 | Clk=0<br>Clk=1<br>Clk=1<br>Clk=0<br>Clk=1<br>Clk=1<br>Clk=1<br>Clk=1<br>Clk=0 | Y=0<br>Y=1<br>Y=1<br>Y=1<br>Y=0<br>Y=0<br>Y=0<br>Y=1 |

## **Outline**

- Introduction

- Basics of the Verilog Language

- > Operators

- Hierarchy/Modules

- Procedures and Assignments

- Timing Control and Delay

- Control Statement

- Logic-Gate Modeling

- Modeling Delay

- > Other Verilog Features

- Summary

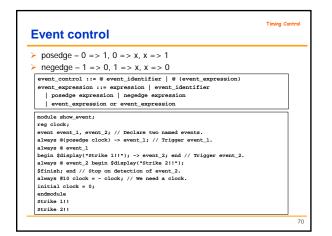

## Timing Control Statements within a sequential block are executed in order In absence of any delay they will execute at the same simulation time – the current time stamp Timing control Delay control Event control Delay control – delays an assignment by a specified amount of time Event control – delays an assignment until a specified event occur

Timing Control

| Delay control                                                                                                                                                                                                                               | Timing Contro |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Timescale compiler directive                                                                                                                                                                                                                |               |

| <pre>`timescale lns/l0ps // Units of time are ns. Round times to<br/>// Allowed unit/precision values: {1   10   100, s   ms   us</pre>                                                                                                     | -             |

| Intra-assignment delay vs. delayed assignment                                                                                                                                                                                               |               |

| <pre>x = #1 y; // intra-assignment delay<br/>// Equivalent to intra-assignment delay.<br/>begin<br/>hold = y; // Sample and hold y immediately.<br/>#1; // Delay.<br/>x = hold; // Assignment to x. Overall same as x = #1 y.<br/>end</pre> |               |

| <pre>#1 x = y; // delayed assignment<br/>// Equivalent to delayed assignment.<br/>begin<br/>#1; // Delay.<br/>x = y; // Assign y to x. Overall same as #1 x = y.<br/>end</pre>                                                              |               |

|                                                                                                                                                                                                                                             |               |

| nodule delay_controls; reg X, Y, Clk, Dummy;             |      |     |     |  |

|----------------------------------------------------------|------|-----|-----|--|

| always #1 Dummy=!Dummy; // Dummy clock, just for graphic | в. Т | Clk | хч  |  |

| <pre>// Examples of delay controls:</pre>                | 0    | 0   | хх  |  |

| always begin #25 X=1;#10 X=0;#5; end                     | 10   | 1   | хx  |  |

| // An event control:                                     | 20   | 0   | хх  |  |

| always @(posedge Clk) Y=X; // Wait for +ve clock edge.   | 25   | 0   | 1 x |  |

| always #10 Clk = !Clk; // The real clock.                | 30   | 1   | 11  |  |

| initial begin Clk = 0;                                   | 35   | 1   | 0 1 |  |

| <pre>\$display("T Clk X Y");</pre>                       | 40   | 0   | 0 1 |  |

| <pre>\$monitor("%2g",\$time,,,Clk,,,,X,,Y);</pre>        | 50   | 1   | 0 0 |  |

| <pre>\$dumpvars;#100 \$finish; end</pre>                 | 60   | 0   | 0 0 |  |

| endmodule                                                | 65   | 0   | 1 0 |  |

|                                                          | 70   | 1   | 11  |  |

|                                                          | 75   | 1   | 0 1 |  |

|                                                          | 80   | 0   | 0 1 |  |

|                                                          | 90   | 1   | 0 0 |  |

| Data Slip Problem           module data_slip_1 (); reg Clk, D, Ql, Q2;           /************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                               |      | т   | îmir | ng C | ontro |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|-----|------|------|-------|

| <pre>/************************************</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Data Slip Problem                                             |      |     |      |      |       |

| <pre>always @(posedge Clk) Q1 = D;<br/>always @(posedge Clk) Q2 = Q1; // Data slips here!<br/>// initial begin Clk = 0; D = 1; end always #50 Clk = -Clk;<br/>initial begin Clk = 0; D = 1; end always #50 Clk = -Clk;<br/>initial begin %; \$time, (Clk D Q1 Q2");<br/>\$monitor("%]%; \$time, (Clk, D, D1 Q2");<br/>initial \$400 \$finish; // Run for 8 cycles.<br/>initial \$40mgvars;<br/>endmodule<br/>lways @(posedge Clk) Q1 = #1 D; // The delays in the assgn.<br/>lways @(posedge Clk) Q2 = #1 Q1;// fix the data slip.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | wodule data slip 1 (); reg Clk, D, Q1, Q2;                    | t    | Clk | D    | Q1   | Q2    |

| <pre>always @(posedge Clk) Q2 = Q1; // Data slips here!<br/>/************************************</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | **************************************                        | c    | 0   | 1    | x    | x     |

| <pre>/************************************</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | lways @(posedge Clk) Q1 = D;                                  | 50   | 1   | 1    | 1    | 1     |

| <pre>initial begin Clk = 0; D = 1; end always #50 Clk = -Clk;<br/>initial begin \$display("t Clk D Q1 Q2");<br/>smonitor("\$32",\$time,.(bx,,D,,Q1,r,Q1); end<br/>initial \$400 \$finish; // Run for 8 cycles.<br/>initial \$dumpvars;<br/>endmodule<br/>lways @(posedge Clk) Q1 = #1 D; // The delays in the assgn.<br/>lways @(posedge Clk) Q2 = #1 Q1;// fix the data slip.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | lways @(posedge Clk) Q2 = Q1; // Data slips here!             | 100  | 0   | 1    | 1    | 1     |

| <pre>initial begin \$display("t Clk D Q1 Q2");<br/>\$monitor("%3g",\$time,,Clk,,,D,,Ql,,.Q2); end<br/>initial \$dumpvars;<br/>endmodule</pre> 250 1 1 1 2 300 0 1 1 1<br>t Clk D Q1 Q<br>0 0 1 x 2<br>50 1 1 2<br>50 1 1 1<br>10 0 1 x 2<br>51 1 1 2<br>10 0 1 1 2<br>51 1 1 1<br>51 1 1<br>51 1 1 1 | ***************** bad sequential logic above ***************/ | 150  | 1   | 1    | 1    | 1     |

| <pre>\$monitor("%3g*,\$time,,Clk,,,D,,Ql,,Q2); end<br/>initial #400 \$finish; // Run for 8 cycles.<br/>initial \$400 pvars;<br/>endmodule<br/>lways @(posedge Clk) Q1 = #1 D; // The delays in the assgn.<br/>lways @(posedge Clk) Q2 = #1 Q1;// fix the data slip.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nitial begin Clk = 0; D = 1; end always #50 Clk = ~Clk;       | 200  | 0   | 1    | 1    | 1     |

| <pre>initial #400 \$finish; // Run for 8 cycles.<br/>initial \$dumpvars;<br/>endmodule<br/>lvays @(posedge Clk) Q1 = #1 D; // The delays in the assgn.<br/>lvays @(posedge Clk) Q2 = #1 Q1;// fix the data slip.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nitial begin \$display("t Clk D Q1 Q2");                      | 250  | 1   | 1    | 1    | 1     |

| <pre>initial \$dumpvars;<br/>endmodule</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | monitor("%3g",\$time,,Clk,,,,D,,Q1,,,Q2); end                 | 300  | 0   | 1    | 1    | 1     |

| endmodule         t         Clk p Q1 (           lways @(posedge Clk)         Q1 = #1 D; // The delays in the assign.         51         1         1         2           lways @(posedge Clk)         Q2 = #1 Q1;// fix the data slip.         100         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nitial #400 \$finish; // Run for 8 cycles.                    | 350  | 1   | 1    | 1    | 1     |

| endmodule 0 0 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                               | +    | Clk |      | 01   | 02    |

| <pre>llways @(posedge Clk) Q1 = #1 b; // The delays in the assgn. llways @(posedge Clk) Q2 = #1 Q1;// fix the data slip. 50 1 1 2 51 1 1 1 50 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 1 1 55 1 55 1 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1 55 1</pre>                                                                                                                                                                                   | endmodule                                                     |      |     |      | ~    | ~     |

| <pre>lways @(posedge Clk) Q1 = #1 b; // The delays in the asgr  s1 1 1 1 100 0 11 2 151 1 1 150 1 1 150 1 1 150 1 1 150 1 150 1 1 150 150 1 1 1 151 1 1 1 15 15 10 0 1 1 1 15 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                               | - 50 | -   | -    |      |       |

| lways @(posedge Clk) 02 = #1 01;// fix the data slip.<br>100 0 1 1 2<br>150 1 1 1 2<br>151 1 1 1 2<br>200 0 1 1 2<br>250 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                               |      |     |      |      |       |

| 151 1 1 1<br>200 0 1 1 1<br>250 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ways @(posedge Clk) Q2 = #1 Q1;// fix the data slip.          |      |     | -    | -    |       |

| 200 0 1 1 1<br>250 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                               | 150  | 1   | 1    | 1    | x     |

| 250 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               | 151  | 1   | 1    | 1    | 1     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                               | 200  | 0   | 1    | 1    | 1     |

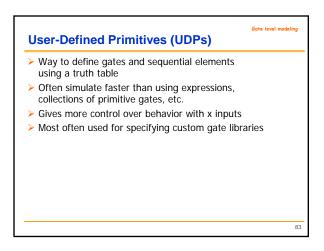

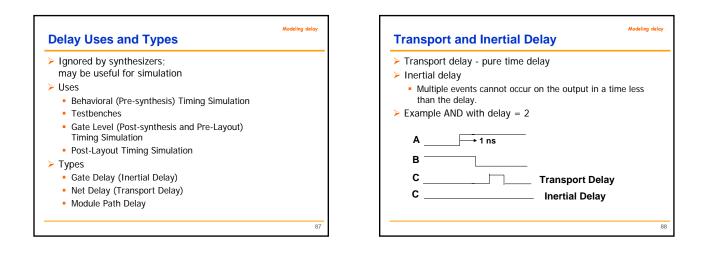

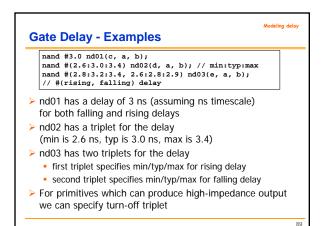

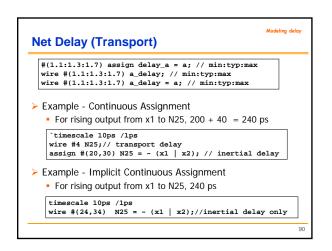

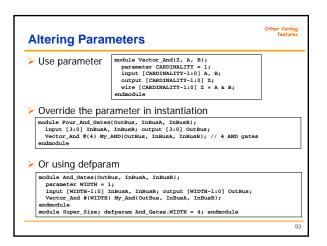

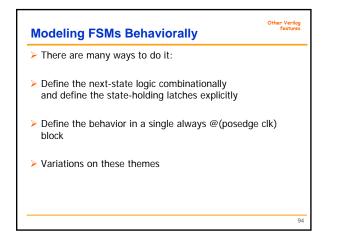

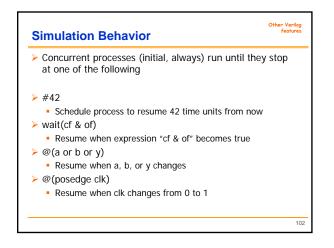

| 300 0 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               | 250  | 1   | 1    | 1    | 1     |