| Netv       | vorks for Arithmetic Operations                                                                                                     |   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|---|

| Ca         | se Study: Serial Parallel Multiplier                                                                                                |   |

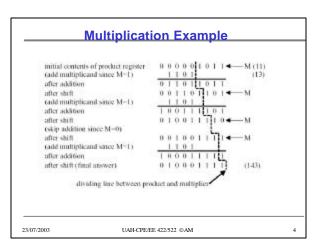

| Note: N    | Mukipikard 1101 (13)<br>Mukipikar 1011 (11)<br>Partial 100111<br>Products 100111<br>1001111 (143)<br>we use unsigned binary numbers |   |

| 23/07/2003 | UAH-CPE/EE 422/522 @AM                                                                                                              | 2 |

| Time | State | Counter | Product<br>Register | 8 | м | к | Load | Ad  | Sh  | Done  |

|------|-------|---------|---------------------|---|---|---|------|-----|-----|-------|

| 10   | 50    | 00      | 0000000000          | 0 | 0 | D | 0    | - Ô | 0   | ō     |

| ti   | 50    | 00      | 0000000000          | 1 | 0 | 0 | 1    | 0   | 0   | 0     |

| £2   | 51    | 00      | 000001011           | 0 | 1 | 0 | 0    | 1   | 0   | 0     |

| t3   | 52    | 00      | 011011011           | 0 | 1 | 0 | 0    | 0   | 1   | 0     |

| .b4  | 51    | 01      | 001101101           | 0 | 1 | 0 | 0    | 1   | σ   | 0     |

| t5   | 52    | 01      | 100111101           | 0 | 1 | 0 | 0    | 0   | 1   | 0     |

| - 85 | 51    | 10      | 010011110           | 0 | 0 | D | 0    | 0   | 101 | 0     |

| £7   | 51    | 11      | 001001111           | 0 | 1 | 1 | 0    | 1   | 0   | 0 0 0 |

| t8   | 52    | 11      | 100011111           | 0 | 1 | 1 | 0    |     |     |       |

| 19   | 53    | 00      | 010001111           | 0 | 1 | 0 | 0    | 0   | 0   | 1     |

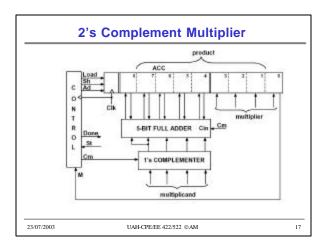

# Multiplication of Signed Binary Numbers

- How to multiply signed binary numbers?

- Procedure

- Complement the multiplier if negative

- Complement the multiplicand if negative

- Multiply two positive binary numbers

- Complement the product if it should be negative

- Simple but requires more hardware and time than other available methods

UAH-CPE/EE 422/522 © AM

# Multiplication of Signed Binary Numbers

- Four cases

- Multiplicand is positive, multiplier is positive

- Multiplicand is negative, multiplier is positive

- Multiplicand is positive, multiplier is negative

- Multiplier is negative, multiplicand is negative

UAH-CPE/EE 422/522 © AM

- Examples

- $-0111 \times 0101 = ?$

- 1101 x 0101 = ?

- $-0101 \times 1101 = ?$

- 1 x 1101 = ?

- 1011 x 1101 = ?

- Preserve the sign of the partial product at each step

If multiplier is negative, complement

- the multiplicand before adding it in at the last step

23/07/2003

15

16

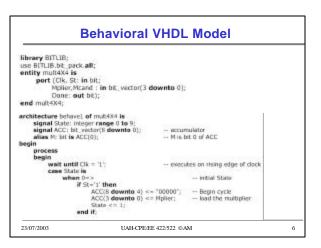

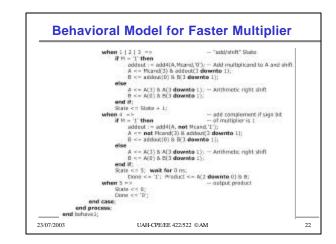

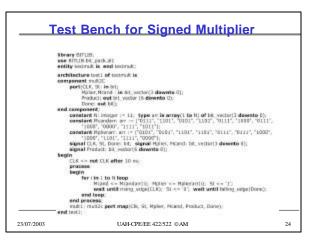

| Behavioral Model for F                                                                                                                                   | aster multiplier                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| ilbrary BITLIB;<br>user BITLIB.ist_pack.eff;                                                                                                             |                                    |

| entity mail2C is<br>pert (CJK, St. in bit;<br>Mplor, Mand : in bit, vector(3 dow<br>Product; out bit, vector (6 downto<br>Done; out bit)/<br>end mail2C; |                                    |

| anchitecture behave1 of mult2C is<br>signal State : integer range 0 to 5:<br>signal A, 5: htt. vector(3 downto 0);<br>alias M: bit is 800);<br>beau      |                                    |

| begin<br>process<br>variable addout: bit_vector[4 downto 0<br>begin                                                                                      | Pic .                              |

| wait until CLK = '1';<br>case State is                                                                                                                   | and a Picker                       |

| when 0=><br>af St~'1' then                                                                                                                               | initial State                      |

| A <= "0000";<br>8 <= Mpler;                                                                                                                              | Begin cycle<br>load the multiplier |

| State <= 1;<br>and if                                                                                                                                    |                                    |

| First CLP<br>force to<br>Porce c<br> | munid file (<br>1 St State<br>1 1 2, 0 22<br>k 1 0, 0 1<br>* -3/6)<br>kand 020<br>plier 110)<br>7 | A B Des<br>D - tepe<br>I | e Prod |       |       |      |      |          |

|--------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------|--------|-------|-------|------|------|----------|

| 118                                  | delta                                                                                             | CLK                      | St     | State |       |      | Done | Product  |

| 0                                    | +1                                                                                                | 1                        | D      | D     | 0000  | 0000 | D    | 0000000  |

| 2                                    | + D                                                                                               | 1                        | 1      | D     | 8000  | 0000 | D    | 0000000  |

| 10                                   | +0                                                                                                | 0                        | - 1    | D     | 8000  | 0000 | D    | 0000000  |

| 25                                   | +1                                                                                                | 1                        | 1      | 1     | 8000  | 3303 | D    | 0000000  |

| 22                                   | +0                                                                                                | - E                      | D      | - 1   | 0000  | 3301 | D    | 0000000  |

| 30                                   | +0                                                                                                | - a -                    | D      | 1     | \$000 | 3301 | D    | 0000003  |

| 45                                   | +1                                                                                                | 1                        | D.     | 2     | 0010  | 3330 | D    | 0000000  |

| 50                                   | +0                                                                                                | - a -                    | D      | 2     | 0030  | 3330 | 0    | 0000000  |

| 62                                   | +1                                                                                                | ÷ î                      | 0      | 3     | 0001  | 0111 | D    | 0000003  |

| 70                                   | +0                                                                                                | a a                      | D      | 3     | 0001  | 0111 | D    | 0000000  |

| 89                                   | +1                                                                                                | 1 E                      | 0      | 4     | \$011 | 0011 | 0    | 0000000  |

| 92                                   | +0                                                                                                | 0                        | D      |       | 8011  | 0011 | D    | 10000003 |

| 100                                  | +2                                                                                                | ÷.                       | 0      | 5     | 1111  | 5001 | 1    | 1110001  |

| 110                                  | +0                                                                                                | - a .                    | 0      | 5     | 1111  | 2001 | 4    | 1110001  |

| 1.20                                 | +1                                                                                                | 1. 110                   | Ú.     | 0     | 1111  | 0001 | D    | 1110001  |

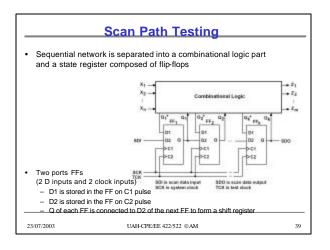

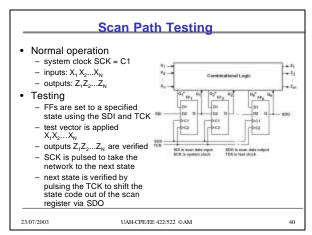

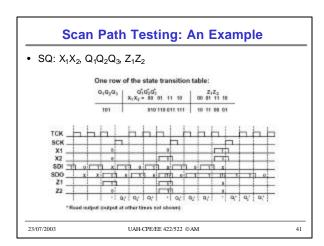

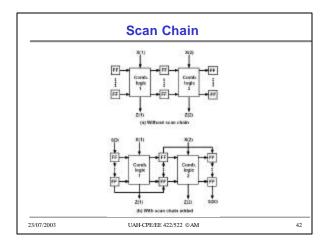

### Hardware Testing and Design for Testability

Testing during design process

use VHDL test benches to verify that the overall design and algorithms used are correct

verify timing and logic after the synthesis

- · Post-fabrication testing

- when a digital system is manufactured, test to verify that it is free from manufacturing defects

- today, cost of testing is major component of the manufacturing cost

- efficient techniques are needed to test and design digital systems so that they are easy to test

23/07/2003

UAH-CPE/EE 422/522 © AM

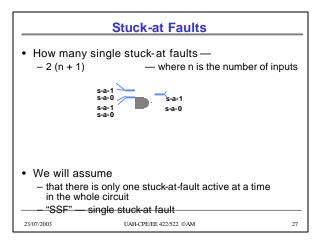

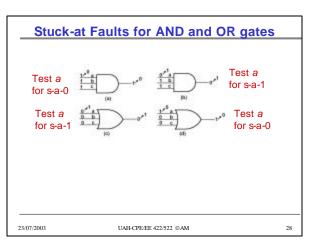

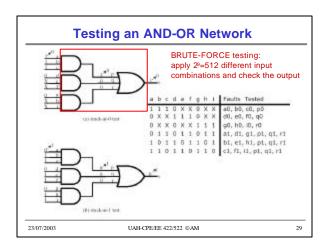

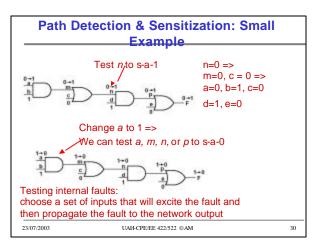

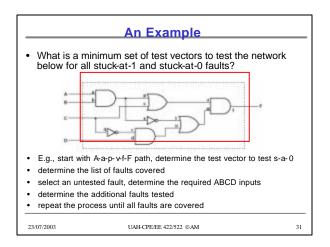

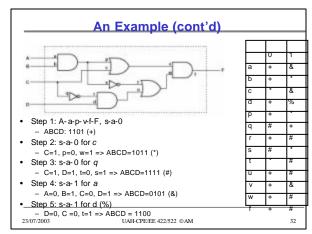

# Testing Combinational Logic Common types of errors short circuit open circuit If the input to a gate is shorted to ground, the input acts as if it is stuck at logic 0 sa-0 (stuck-at-0) faults If the input to a gate is shorted to positive supply voltage, the input acts as if it is stuck at logic 1 sa-1 (stuck-at-1) faults

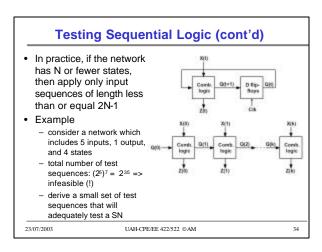

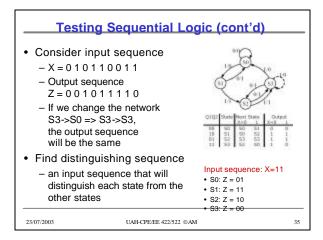

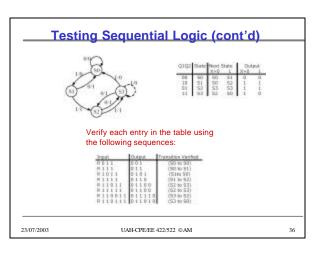

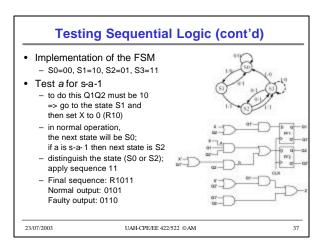

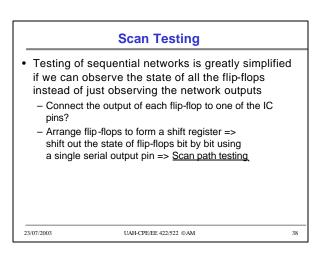

- In general, much more difficult than testing combinational logic since we must use sequences of inputs

- typically we can observe inputs and outputs,

- not the state of flip-flops

- assume the reset input,

- so we can reset the network to the initial state

- Test procedure

- reset the network to the initial state

- apply a test sequence and observe the output sequence

- if the output is correct, repeat the test for another sequence

- How many test sequences do we have?

- how do we test that the initial state of the network under test is equivalent to the initial state of the correct network?

UAH-CPE/EE 422/522 @AM

– what is the sequence length?

23/07/2003

33

# •9

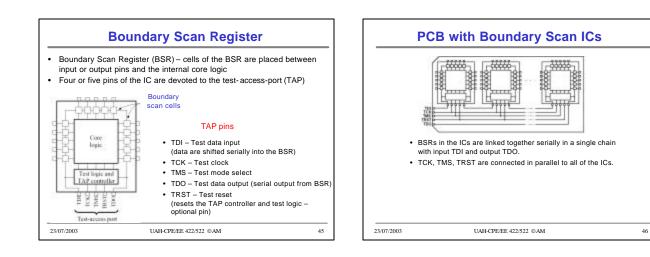

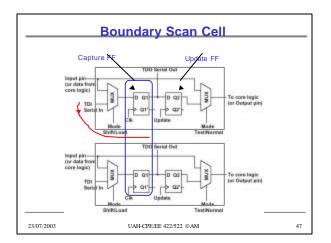

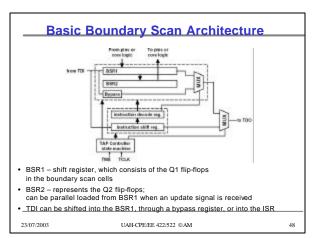

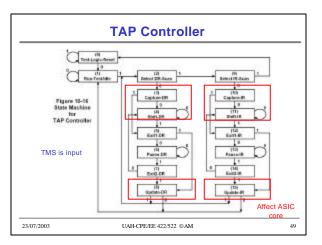

| TAP Contro                       | ller                                                                             |             |

|----------------------------------|----------------------------------------------------------------------------------|-------------|

| <ul> <li>– 16 state F</li> </ul> | SM                                                                               |             |

| <ul> <li>Change st</li> </ul>    | ates depending on TMS and T                                                      | CK          |

|                                  | gnals to control the test data reg<br>register (including serial shift c<br>cks) |             |

| • Test-logic-re                  | eset is the initial state;                                                       |             |

| on a low TN                      | IS go to Run-Test/Idle stat                                                      | e           |

| • TMS: 1100                      | => Shift-IR                                                                      |             |

| • In Shift-IR c                  | command is shifted in throu                                                      | gh TDI port |

| •                                |                                                                                  |             |

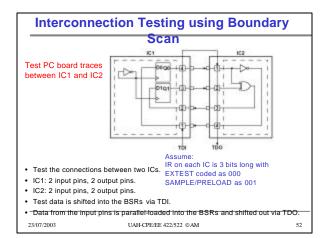

| Instructions in the IEEE Standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>BYPASS: allows the TDI serial data to go trough 1- bit bypass register<br/>on the IC instead of through the BSR1. In this way one or more ICs on<br/>the PCB may be bypassed.</li> <li>SAMPE/RELOAD: used to scan the BSR without interfering with the<br/>normal operation of the core logic. Data is transferred to or from the<br/>core logic from or to the IC pins without interference. Samples of this<br/>data can be taken and scanned out through the BSR. Test data can be<br/>shifted into the BSR.</li> </ul> |    |

| <ul> <li>EXTEST: allows board-level interconnect testing and testing of clusters of components which do not incorporate the boundary scan test features. Test data is shifted into the BSR and then it goes to the outpu pins. Data from the input pins is captured by the BSR.</li> <li>INTEST (optional): this instruction allows testing of the core logic by</li> </ul>                                                                                                                                                         |    |

| <ul> <li>shifting test data into the boundaryscan register. Data shifted into the BSR takes the place of data from the input pins, and output data from the core logic is loaded into the BSR.</li> <li>RUNBIST (optional): this instruction causes special built-in self-test (BIST) logic within the IC to execute.</li> </ul>                                                                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51 |

- 1. Reset the TAP state machine to the Test-Logic-Reset state by inputting a sequence of five 1's on TMS. The TAP controller is designed so that a sequence of five 1's will always reset it regardless of the present state. Alternatively, TRST could be asserted if it is available.

- 2. Scan in the SAMPLE/PRELOAD instruction to both ICs using the sequences for TMS and TDI given below. State: 0 1 2 9 10 11 11 11 11 11 11 12 15 2

- 0110 0 0 0 0 0 0 1 1 1 ---- <u>1 0 0</u> 1 0 0 -TMS: TDI:

- The TMS sequence 01100 takes the TAP controller to the Shift-IR state. In this state, copies of the SAMPLE/PRELOAD instruction (code 001) are shifted into the instruction registers on both ICs. In the Update-IR state, the instructions are loaded into the instruction decode registers. Then the TAP controller goes back to the Select DR-scan state.

23/07/2003

UAH-CPE/EE 422/522 © AM

53

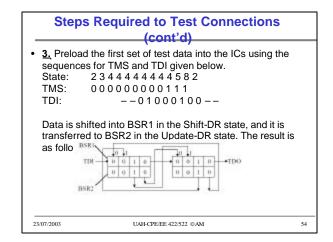

|                                           | (cont'd)                                                                                                                                                                                                                                              |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. Scan in                                | the EXTEST instruction to both ICs using the                                                                                                                                                                                                          |

| following s                               | equences:                                                                                                                                                                                                                                             |

| State:                                    | 2 9 10 11 11 11 11 11 11 12 15 2                                                                                                                                                                                                                      |

| TMS:                                      | 10000000111                                                                                                                                                                                                                                           |

| TDI:                                      | 0 0 0 0 0 0                                                                                                                                                                                                                                           |

| instruction<br>instruction<br>the preload | ST instruction (000) is scanned into the register in state Shift-IR and loaded into the decode register in state Update-IR. At this point ded test data goes to the output pins, and it is d to the adjacent IC input pins via the printed rd traces. |

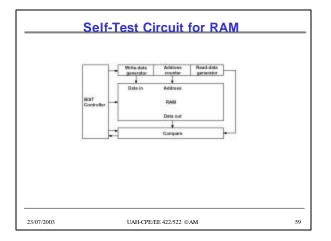

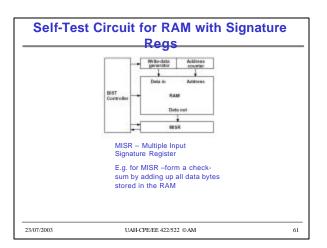

| Steps Required t                                                                                                                                                                                                                                                                                                                                                                                                                                       | o Test Connecti<br>ont'd)                                                                                                                                                                                        | ons                                                                 |                                                                                                                       | Built-In Self-Test                                                                                                                                                                                                                                     |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

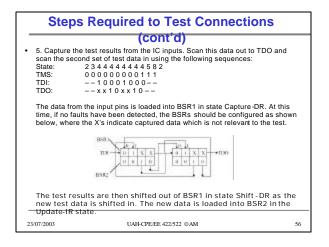

| <ul> <li>6. Capture the test results<br/>out to TDO and scan all 0'<br/>sequences:<br/>State: 2 3 4 4 4 4 4 4 4 4 5<br/>TMS: 0 0 0 0 0 0 0 0 0 1 1<br/>TDI: 0 0 0 0 0 0 0 0 0 -<br/>TDO: x x 0 1 x x 0 1 -</li> <li>The data from the input pir<br/>Capture-DR. Then it is shi<br/>are shifted in. The 0's are<br/>IR state. The controller the<br/>state and normal operatior<br/>interconnection test passe<br/>match the ones given abor</li> </ul> | s in using the following<br>8 2 9 0<br>1 1 1<br><br>hs is loaded into BSR1<br>fted out in state Shift-<br>loaded into BSR2 in th<br>n returns to the Test-L<br>o of the ICs can then or<br>s if the observed TDO | in state<br>DR as all 0's<br>le Update-<br>.ogic-Reset<br>ccur. The | <ul> <li>Built-In S</li> <li>Using BIS</li> <li>when tes<br/>an on-chi<br/>to the circ</li> <li>the result</li> </ul> | th mode is selected by the test-select signal,<br>ip test generator applies test patterns<br>cuit under test<br>ting outputs are observed by the response monitor,<br>oduces an error signal if an incorrect output is detected<br>Generic BIST Scheme |    |

| 23/07/2003 UAH-CPE                                                                                                                                                                                                                                                                                                                                                                                                                                     | EE 422/522 ©AM                                                                                                                                                                                                   | 57                                                                  | 23/07/2003                                                                                                            | UAH-CPE/EE 422/522 ©AM                                                                                                                                                                                                                                 | 58 |