# A BINARY INSTRUMENTATION TOOL SUITE FOR CAPTURING AND COMPRESSING TRACES FOR MULTITHREADED SOFTWARE

by

Albert R. Myers

### A THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

HUNTSVILLE, ALABAMA

2014

| 1                                        | fillment of the requirements for a master's de-  |

|------------------------------------------|--------------------------------------------------|

| gree from The University of Alabama i    | in Huntsville, I agree that the Library of this  |

| University shall make it freely availab  | ble for inspection. I further agree that permis- |

| sion for extensive copying for scholarly | purposes may be granted by my advisor or, in     |

| his/her absence, by the Chair of the De  | epartment or the Dean of the School of Gradu-    |

| ate Studies. It is also understood that  | due recognition shall be given to me and to      |

| The University of Alabama in Huntsvi     | ille in any scholarly use which may be made of   |

| any material in this thesis.             |                                                  |

|                                          |                                                  |

|                                          |                                                  |

|                                          |                                                  |

| (student signature)                      | (date)                                           |

|                                          |                                                  |

### THESIS APPROVAL FORM

Submitted by Albert R. Myers in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this thesis. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering.

|        | Committee Chair  |

|--------|------------------|

| (Date) | -                |

|        |                  |

|        | -                |

|        |                  |

|        | -                |

|        |                  |

|        | _                |

|        |                  |

|        | Department Chair |

|        | -                |

|        | _College Dean    |

|        |                  |

|        | Craduata Daar    |

|        | Graduate Dean    |

## ABSTRACT

## The School of Graduate Studies The University of Alabama in Huntsville

| Degree Master of Science in Engineering College/Dept. Engineering/Electrical &                    |

|---------------------------------------------------------------------------------------------------|

| Computer Engineering                                                                              |

| Name of Candidate Albert R. Myers                                                                 |

| Title A Binary Instrumentation Tool Suite For Capturing and Compressing Traces                    |

| For Multithreaded Software                                                                        |

| Program execution traces are widely used in program debugging, workload                           |

| characterization, performance analysis, and trace-driven architecture simulation. A               |

| number of research efforts have been dedicated to tracing in single-threaded soft-                |

| ware. Multi-cores that integrate a number of processor cores on a single chip and                 |

| execute multithreaded software have become the standard in embedded, desktop,                     |

| and server computer systems. In this research we develop and evaluate a suite of                  |

| software tools for capturing and compressing traces for multithreaded software                    |

| called mTrace, which we believe is the first set available. mTrace incorporates the               |

| following tools: (i) $\mathit{mcfTrace}$ that captures and compresses control-flow traces, (ii)   |

| ${\it mlsTrace}$ that captures and compresses memory referencing traces, (iii) ${\it mcfTRapton}$ |

| that captures control-flow traces and compresses them using our TRaptor branch                    |

| prediction mechanism, and (iv) ${\it mlvCFiat}$ that captures load value traces and com-          |

| presses them using our CFiat cache mechanism. The thesis describes the tools' func                |

| tionality and verification and evaluates their effectiveness by considering trace sizes           |

| execution times, and prediction rates of cache and branch prediction structures for a             |

| selected set of benchmarks.                                                                       |

| Abstract Approval: Committee Chair                                                                |

| Department Chair                                                                                  |

Graduate Dean

## TABLE OF CONTENTS

| Page                                           |             |

|------------------------------------------------|-------------|

| OF FIGURESxi                                   | LIST OF FIG |

| OF TABLES xv                                   | LIST OF TAB |

| TER                                            | CHAPTER     |

| BLE OF CONTENTS                                | TABLE O     |

| IAPTER 1                                       | СНАРТЕР     |

| 1.1 Background and Motivation                  | 1.1         |

| 1.2 mTrace Tool Suite                          | 1.2         |

| 1.3 Results                                    | 1.3         |

| 1.4 Contributions                              | 1.4         |

| 1.5 Outline                                    | 1.5         |

| IAPTER 2                                       | СНАРТЕР     |

| 2.1 Control Flow Traces                        | 2.1         |

| 2.2 Memory Reference Traces                    | 2.2         |

| 2.3 Tracing in Embedded and Multi-core Systems | 2.3         |

| 2.4 Challenges and Opportunities               | 2.4         |

| IAPTER 3                                       | СНАРТЕР     |

| 3.1 Software Trace Compression                 | 3.1         |

| 3.2 Hardware Trace Compression16               | 3.2         |

| CF | HAPTER |                          |

|----|--------|--------------------------|

|    | 4.1    | mcfTrace                 |

|    | 4.1.1  | Functional Description   |

|    | 4.1.2  | Implementation Details   |

|    | 4.1.3  | Verification/Test39      |

|    | 4.2    | mlsTrace                 |

|    | 4.2.1  | Functional Description   |

|    | 4.2.2  | Implementation Details   |

|    | 4.2.3  | Verification/Test54      |

|    | 4.3    | mcfTRaptor60             |

|    | 4.3.1  | Functional Description61 |

|    | 4.3.2  | Implementation Details68 |

|    | 4.3.3  | Verification/Test        |

|    | 4.4    | mlvCFiat86               |

|    | 4.4.1  | Functional Description86 |

|    | 4.4.2  | Implementation Details   |

|    | 4.4.3  | Verification/Test        |

| CF | HAPTER | 2 5                      |

|    | 5.1    | Environment              |

|    | 5.2    | Metrics                  |

|    | 5.3    | Benchmarks               |

| 5.4    | Running Experiments | 116 |

|--------|---------------------|-----|

| СНАРТЕ | R 6                 | 119 |

| 6.1    | mcfTrace            | 119 |

| 6.2    | mlsTrace            | 122 |

| 6.3    | mcfTRaptor          | 125 |

| 6.4    | mlvCFiat            | 134 |

| СНАРТЕ | R 7                 | 145 |

| СНАРТЕ | ₹ 8                 | 147 |

## LIST OF FIGURES

| gure Pa                                                                      | age |

|------------------------------------------------------------------------------|-----|

| Figure 3.1 TRaptor Operation for One Thread (Private/Shared)                 | .19 |

| Figure 3.2 mcfTRaptor with Private Predictor Structures                      | .20 |

| Figure 3.3 mcfTRaptor with Shared Predictor Structures                       | .21 |

| Figure 3.4 CFiat Operation for One Thread (Private/Shared)                   | .23 |

| Figure 3.5 mlvCFiat with Private Cache Structures                            | .24 |

| Figure 3.6 mlvCFiat with Shared Cache Structures                             | .25 |

| Figure 4.1 mcfTrace organization                                             | .27 |

| Figure 4.2 mcfTrace Descriptor Formats: Binary (top) and ASCII (bottom).     | 31  |

| Figure 4.3 mcfTrace Example Output                                           | .32 |

| Figure 4.4 $\it mcfTrace$ Instrumentation Implementation from mcfTrace.cpp . | .35 |

| Figure 4.5 Analysis Routine from <i>mcfTrace</i>                             | .36 |

| Figure 4.6 mcfTrace Write Routine                                            | .39 |

| Figure 4.7 Selection from BranchEnumeration.s                                | .40 |

| Figure 4.8 mcfTrace output for BranchEnumeration.s selection                 | .40 |

| Figure 4.9 Unconditional branches from BranchEnumeration.s                   | .41 |

| Figure 4.10 mcfTrace output for BranchEnumeration.s section                  | .41 |

| Figure 4.11 Selection from BranchTest.s and mcfTrace output                  | .42 |

| Figure 4.12 Selection from BranchTest.s and mcfTrace output                  | .43 |

| Figure 4.13 $mlsTrace$ descriptor formats: binary (top) and ASCII (bottom).  | .46 |

| Figure 4.14 <i>mlsTrace</i> example output                                   | .48 |

| Figure 4.15 <i>mlsTrace</i> instrumentation from mlsTrace.cpp                | .51 |

| Figure 4.16 mlsTrace analysis example from mlsTrace h                        | 53  |

| Figure 4.17 Example 1 from mlsTest.c                                             | 54    |

|----------------------------------------------------------------------------------|-------|

| Figure 4.18 mlsTest.c output and $mlsTrace$ descriptors for Example 1            | 56    |

| Figure 4.19 Example 2 from mlsTest.c                                             | 57    |

| Figure 4.20 mlsTest.c output and $mlsTrace$ descriptors for Example 2            | 59    |

| Figure 4.21 $mlsTrace$ descriptors for SIMD instructions in Example 2            | 60    |

| Figure $4.22\ mcfTRaptor$ descriptor formats: binary (top) and ASCII (both       | ttom) |

|                                                                                  | 65    |

| Figure 4.23 mcfTRaptor example output                                            | 67    |

| Figure 4.24 mcfTRaptor instrumentation                                           | 69    |

| Figure 4.25 mcfTRaptor – indirect call analysis code                             | 71    |

| Figure $4.26\ mcfTRaptor-iBTB\ index$                                            | 72    |

| Figure $4.27\ mcfTRaptor-iBTB\ lookup$                                           | 73    |

| Figure 4.28 mcfTRaptor – conditional branch analysis                             | 75    |

| Figure 4.29 mcfTRaptor – gshsare index and update                                | 76    |

| Figure 4.30 gshare Example                                                       | 77    |

| Figure 4.31 gshare Entries Test Output                                           | 79    |

| Figure 4.32 Return Address Stack Example                                         | 81    |

| Figure 4.33 Return Address Stack Example Results                                 | 82    |

| Figure 4.34 iBTB Example                                                         | 83    |

| Figure 4.35 iBTB Results                                                         | 86    |

| Figure 4.36 mlvCFiat Descriptor Format                                           | 89    |

| mlvCFiat ASCII descriptors also include Thread ID, First Access Hit Co           | ount, |

| and Value. In Figure 4.36, the ASCII descriptor states thread zero had two first | st    |

| access flag hits before <i>mlvCFiat</i> had a first access flag miss for a four byte load |   |

|-------------------------------------------------------------------------------------------|---|

| operand with a value of 0x00000004.                                                       | 0 |

| Figure 4.37 mlvCFiat Example9                                                             | 2 |

| Figure 4.38 mlvCFiat Instrumentation9                                                     | 5 |

| Figure 4.39 <i>mlvCFiat</i> Multiline Cache Load Analysis9                                | 6 |

| Figure 4.40 Multiline Cache Load Operation                                                | 9 |

| Figure 4.41 Evict.s10                                                                     | 0 |

| Figure 4.42 evict.s Results                                                               | 3 |

| Figure 4.43 multiblock.s                                                                  | 4 |

| Figure 4.44 multiblock.s Results                                                          | 7 |

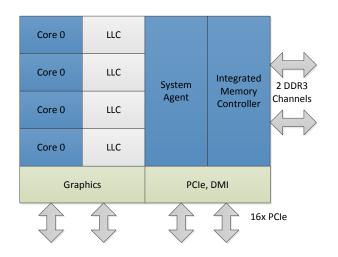

| Figure 5.1 Block Diagram of the Xeon E3-1240 v2 processor10                               | 9 |

| Figure 5.2 An Excerpt of a Script File that Runs $mcfTrace$ on the fft                    |   |

| Benchmark11                                                                               | 9 |

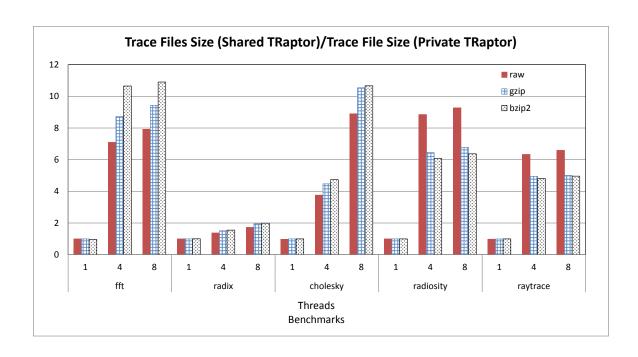

| Figure 6.1 Ratio of Trace File Sizes for Shared and Private TRaptor13                     | 3 |

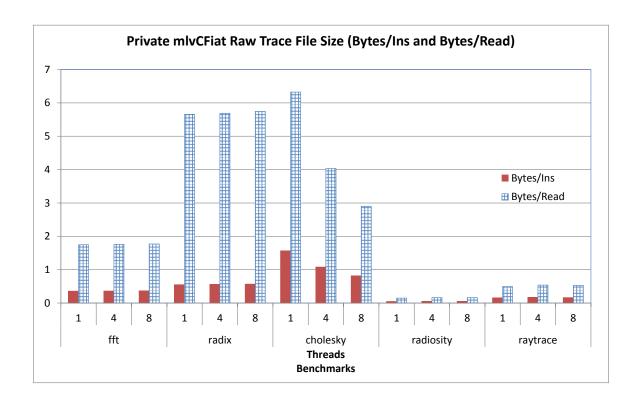

| Figure 6.2 Trace File Size in Bytes/Ins and Byte/Read for Private $mlvCFiat$              |   |

| 13                                                                                        | 8 |

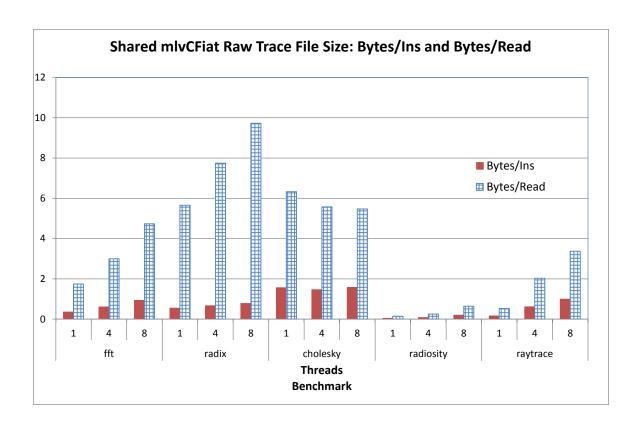

| Figure 6.3 Trace File Sizes in Bytes/Ins and Bytes/Read for Shared mlvCFian               | t |

|                                                                                           | 3 |

## LIST OF TABLES

| Table  | Page                                                                       |

|--------|----------------------------------------------------------------------------|

| Г      | Cable 4.1 mcfTrace Parameters   29                                         |

| Г      | Cable 4.2 Intel 64 and IA-32 Control Transfer Instruction Classification33 |

| Т      | Cable 4.3 mlsTrace Parameters                                              |

| Т      | Cable 4.4 mlsTrace Data Types49                                            |

| Т      | Cable 4.5 mcfTRaptor parameters62                                          |

| Т      | Cable 4.6 mlvCFiat parameters88                                            |

| Т      | Cable 5.1 Benchmark Characterization for Control-flow Instructions113      |

| Т      | Cable 5.2 Benchmark Characterization for Memory Reads and Writes114        |

| Т      | Cable 5.3 Benchmark Characterization of Memory Reads115                    |

| Т      | Cable 5.4 Benchmark Characterization of Memory Writes116                   |

| Г      | Cable 5.5 Trace Collection Runs                                            |

| Г      | Cable 6.1 mcfTrace Output Trace Files Sizes and Compression Ratio120       |

| Т      | Cable 6.2 mcfTrace Running Times and Slowdown Due to Compression122        |

| Г      | Cable 6.3 mlsTrace Output Trace Files Sizes and Compression Ratio123       |

| Т      | Table 6.4 mlsTrace Execution Times and Compression Slowdowns124            |

| Г      | Cable 6.5. Private TRaptor Misprediction Rates                             |

| Т      | Cable 6.6. Private TRaptor Trace File Sizes                                |

| Г      | Cable 6.7 Private <i>mcfTRaptor</i> Execution Times and Slowdown Due to    |

| Compre | ssion                                                                      |

| Т      | Cable 6.8. Shared TRaptor Misprediction Rates                              |

| Т      | Table 6.9. Shared TRantor Trace File Sizes 132                             |

|       | Table 6.10 Shared <i>mcfTRaptor</i> Execution Times and Slowdown Due to         |     |

|-------|---------------------------------------------------------------------------------|-----|

| Compr | ression                                                                         | 134 |

|       | Table 6.11. Private <i>mlvCFiat</i> Cache and First Access Hit Rates            | 136 |

|       | Table 6.12. Private mlvCFiat Trace File Sizes                                   | 137 |

|       | Table 6.13 Private $\mathit{mlvCFiat}$ Running Times and Compression Slowdown . | 139 |

|       | Table 6.14. Shared <i>mlvCFiat</i> Cache and First Access Hit Rates             | 141 |

|       | Table 6.15. Shared <i>mlvCFiat</i> Trace File Sizes                             | 142 |

|       | Table 6.16 Shared <i>mlvCFiat</i> Running Times and Compression Slowdown.       | 144 |

### CHAPTER 1

#### INTRODUCTION

This chapter is organized as follows. Section 1.1 gives background and motivation for this thesis. Section 1.2 gives a short overview of the mTrace tool suite developed to enable capturing and storing of program execution traces in multithreaded software. Section 1.3 describes main results of the experimental evaluation of the mTrace tool suite. Section Section 1.4 lists the main contributions of the thesis and Section 1.5 gives an outline of the thesis.

## 1.1 Background and Motivation

Increasing software complexity and time-to-market contraints have created challenges for system testing and verification. According to the National Institute of Standards and Technology [1], between \$22.2 and \$59.5 billion are spent nationally because of inadequate software testing infrastructure. One half of the costs are incurred by end users of software through error avoidance and error mitigation activities, and the other half is incured by software developers, reflecting the resources consumed due to inadequate testing methods and tools. The same study found that developers spend an increasing portion of time in software testing and debugging between 50% and 75% of total development time. Given the ever-increasing sophistication and complexity of software and a market shift toward mutli-core systems, the cost of testing and debugging of software is likely to increase further. These trends

underscore a need for better better debugging tools to aide in the software engineering process.

Traditional software debugging is inadequate for real-time systems in avionics, autmotive, or military applications because software instrumentation imposes contraints on the timing requirements of the system. Software bugs that manifest in real-time systems are not easily reproducible, and softare instrumentation itself may affect the dynamic properties of the sofware being analyzed. Multithreaded software can also create difficult to debug race conditions, where execution is nondeterministic. Hardware based debugging techniques do not suffer from these problems, and allow developers to debug software without the need to modify source code or rebuild the executable. Hardware debugging usually traces out the relevant information from the processor chip to a remote system using a software interface. Hardware debugging, or tracing, often requires large on chip buffers and wide trace ports to effectively trace out large quantites of data in real-time. These hardware requirements are the motivation of this research, which seeks to reduce traces to a minimal size while still allowing full program replaybility, and similarly reduce trace port bandwidth. IEEE provides a standard that defines different classes of hardware debugging for embedded systems [2]. This standard, Nexus 5001, specifies four classes of debugging, with each subsequent class requiring more hardware complexity. Class 1 provides basic run-control, including break points and a mechanism for reading register and memory values. Class 2 includes unobtrusive collection of execution traces in real-time, which provides enough information to recreate the entire execution path of the program. Class 3 includes, in addition to the execution traces of class 2, the collection of memory referencing traces to provide complete replayability of the values and addresses written to and read from memory. Class 4

allows the remote system interrogating the processor core to emulate memory accesses.

This research seeks to create a software tool suite for capturing and compressing program execution traces (classes 2 and 3 of Nexus 5001) for multithreaded software. Whereas a number of software tools exist for capturing program execution traces for single-threaded software, no such tools are readily available for multithreaded software. The main goal of this research is the development and verification of a tool suite to support capturing traces in multithreaded programs.

#### 1.2 mTrace Tool Suite

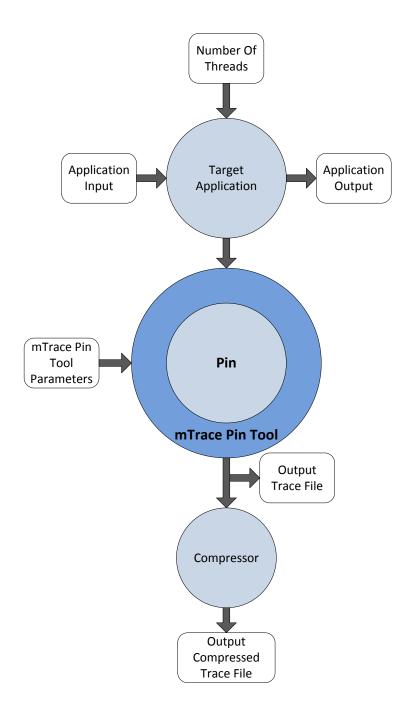

The mTrace tool suite is a collection of Intel Pin tools that provide a means for collecting execution traces (also called control-flow traces) and memory referencing traces with varying degrees of flexibility. The following four Pin tools are included in mTrace:

- mcfTrace Collects and reports control flow traces consisting of branch instruction trace descriptors for multithreaded software. The address of the branch instruction, target address, and type of branch instruction are reported each time a thread retires a branch instruction.

- mlsTrace Collects and reports memory reference traces for multithreaded software. Each trace descriptor includes the load/store instruction's address, operand address, operand size, and operand value.

- mcfTRaptor Collects and reports a minimal control flow trace for multithreaded software using the TRaptor [3] branch prediction structure.

Trace descritpors are collected for incorrectly predicted branch instruc-

tions, reducing the total trace size needed for complete program replayability.

mlvCFiat – Collects and reports a minimal load value trace for multithreaded software by utilizing the CFiat [4] cache access mechanism to reduce the total trace size needed for program replayability. Trace descriptors are collected whenever a cache block is evicted or an operand in a cache block is referenced for the first time.

Each of these four tools uses a variety of parameters that modify the scope of the trace, how tracing occurs, and how the trace is saved. The first two tools, mcfTrace and mlsTrace, were motivated by a need to inspect general properties of control-flow and memory reference traces for multithreaded software, while the last two, mcfTRaptor and mlvCFiat, were motivated by the need for hardware tracing techniques to reduce trace sizes and trace port bandwidths. Each tool generates a trace file for a target binary (and any shared libraries it uses), and a statistics file that characterizes the trace execution.

#### 1.3 Results

The mTrace tools are fully tested and verified on a standard set of parallel benchmark programs. We evaluate the effectiveness of the mTrace tools by considering trace file size and the time needed to capture and store traces as a function of the number of software threads. Each trace tool supports an optional general-purpose compression of captured traces before they are written to the secondary storage. To evaluate compressability of individual traces, we measure compression ratio achieved by general-purpose compressors.

For mcfTRaptor and mlvCFiat tools, we analyze the effectiveness of predictor and cache structures employed by measuring misprediction and cache miss rates. In addition, we analyze two different organizations of TRaptor and CFiat structures: private in which each software thread owns a prediction structure and shared in which multiple software threads share one structure. Our experimental evaluation indicates that a private organization of branch prediction and cache structures results in smaller control-flow and load value traces when compared to the she shared organization.

#### 1.4 Contributions

This thesis makes the following contributions to the field of software binary instrumentation and tools for trace capture and compression:

- Developed and tested tools for capturing and storing program execution traces of multithreaded software, specifically:

- o *mcfTrace*: a tool for capturing and compressing control-flow traces;

- o *mlsTrace*: a tool for capturing and compressing data traces;

- mcfTRaptor: a tool for capturing and compressing control-flow traces using our TRaptor mechanism;

- mlvCFiat: a tool for capturing and compressing data traces using our CFiat mechanism.

- Performed experimental evaluation of the mTrace tools using SPLASH-2

benchmark suite while varying the number of threads.

- Created a public repository of the mTRace tools and traces available at:

<a href="http://lacasa.uah.edu/portal/index.php/software-data/32-mtrace-tools-and-traces">http://lacasa.uah.edu/portal/index.php/software-data/32-mtrace-tools-and-traces</a>.

## 1.5 Outline

The outline of this thesis is as follows: Chapter 2 introduces software tracing, tracing techniques, and future challanges and opportunities. Chapter 3 summarizes the related work and the current state-of-the-art in the field of software and hardware tracing. Chapter 4 describes the mTrace tool suite, summarizes their implementation, and lists the steps taken to verify their behavior. Chapter 5 explains the experimental methodology used to evalute the mTrace tools for a set of benchmarks. Chapter 6 gives the results of the experimental evaluation and Chapter 7 gives concluding remarks.

#### CHAPTER 2

#### BACKGROUND

Software tracing provides software developers with detailed information on the dynamic run-time behavior of software at the image, sub-routine, basic block, or instruction level. Because tracing occurs at a lower level of abstraction and can generate billions of records per second, tracing imposes performance constraints during collection and requires large amounts of storage. This chapter covers the background of several aspects of this research. Sections 2.1 and 2.2 describe control flow and memory reference traces and their applications, respectively. Section 2.3 relates the problems of debugging embedded and real-time systems to tracing. Lastly, Section 2.4 explores the challenges faced in this research and opportunities to pursue in the future.

#### 2.1 Control Flow Traces

Control-flow traces are widely used in software debugging, trace-driven architectural simulation (e.g., branch predictor studies), performance optimization and tunning, and workload characterization [5]. Control flow traces of a program running on a processor are created by recording the addresses of the instructions in the order they are executed. Each instruction executed results in a single record in the control-flow trace. Modern processors may execute billions of instructions per second, generating a vast amount of information that needs to be captured, communicated, and stored. In modern multi-cores, that include a dozen processor cores, the amount of information captured in control-flow traces is even larger. The perfor-

mance and storage overheads associated with trace capture make such tracing feasible only on small program segments and impractical and cost-prohibitive for the entire program.

Depending on the intended trace use, control flow traces can be modified to include fewer but sufficient number of records. For example, in software debugging the goal is to faithfully replay a program's execution offline in software debugger. By analyzing the actual control-flow captured on a host machine and comparing it with the expected one, software developers can quickly locate sources of software bugs. However, to recreate a program's flow, one does not need to record the address of every single instruction executed. Providing that the software debugger has access to program's executable, we need to record only changes in the program flow. These changes are caused by either control-flow instructions or exceptions. When a change in the program flow occurs, we need to record the program counter (PC) of the currently executing instruction and the branch target address (BTA) in the case of a control-flow instruction or the exception-handler target address (ETA) in the case of an exception. The format of trace records can be further modified to require fewer bits for encoding. For example, the number of instructions executed in dynamic basic blocks may replace the program counters, or the target addresses of direct branches can be omitted from the trace because they can be inferred by the software debugger from the program executable.

Other types of control-flow traces may require more trace records or fewer trace records. For example, control-flow traces intended to be used in branch predictor studies require one trace record per control-flow instruction, regardless of its outcome. In multithreaded software, we may need to include additional information

such as thread identification that further qualifies each trace record. In some cases, the time stamp or the processor core identification may be included in the trace.

## 2.2 Memory Reference Traces

Memory reference or data traces contain information recorded from instructions that read from memory or write to memory in the order in which they occur during program execution. Typically, one trace record contains relevant information on a single memory-referencing instruction, such as the program counter and information about memory operands. For each memory operand, we may record (i) the type of memory operation (read or write), (ii) operand address in memory, (iii) size of the operand in bytes, and (iv) a data value read from memory or written to memory. Other information may be included as well, including thread identification in case of multithreaded software, timestamps for the read or write operation, or processor core identification. The format of trace records depends on trace uses and they may contain all or a subset of the fields described above. Regardless of the exact format of trace records, capturing memory reference traces incurs very high performance and storage overheads.

Similar to control flow traces, memory reference traces can be used for software debugging, performance optimization and tunning, workload characterization, and architectural simulations targeting memory subsystem and cache hierarchies. For example, load value traces, traces that contain data values read from memory, can be used in software debugging. Whereas control-flow traces support reconstruction of the program's control flow only, load value traces enable under certain conditions a complete replay of the executed program. These conditions assume that the software debugger includes an instruction set simulator, has access to the program

binary, can access the control-flow traces containing exception records, and can access to the load value traces [4]. Data address traces captured in real-time are of special interest in multi-core systems as they offer valuable information about shared memory access patterns and possible data race conditions.

## 2.3 Tracing in Embedded and Multi-core Systems

Software developers for server and desktop applications often rely on binary instrumentation tools, software development environments, and software debuggers to debug and trace program execution. For example, software developers may set breakpoints, examine the content of registers and memory at breakpoints, or step through the program one instruction at a time. Setting breakpoints and examining the processor state to locate difficult and intermittent bugs in large software projects is demanding and time-consuming. Alternatively, developers can collect program execution traces that are analyzed to diagnose program segments where bugs arise faster. These software development environments may require minimal or no hardware support. However, common to all these methods are that they are obtrusive — the program execution in the debug mode differs from the "native" program execution when no debugging is involved. Whereas this interference may not pose challenges during software development for desktop and server applications, it is often signicficant problem in embedded systems, especially real-time systems.

Embedded software developers face a unique set of challenges. These challenges are driven by both technology and market forces and include: (i) a growing level of sophistication of embedded software with multi-layered software stacks, (ii) increased levels of on-chip integration that limit the visibility of internal modules, (iii) high operating frequencies, (iv) limited input/output bandwidths to and from

systems-on-a-chip, and (v) shrinking time-to-markets. Setting a breakpoint is often not practical in debugging real-time embedded systems; e.g., it may be harmful for hard drives or engine controllers. In addition, debugging through breakpoints interferes with program execution. The order of events during debugging may deviate from the order native execution; this deviation can cause original bugs to disappear in the debug run.

To meet these challenges and get reliable and high-performance products to market on time, embedded software developers increasingly rely upon on-chip resources for debugging and program tracing. However, even limited hardware support for debugging and tracing is associated with extra cost in chip area for capturing and buffering traces, for integrating these modules into the rest of the system, and for sending out the information through dedicated trace ports. These costs often make system-on-a-chip (SOC) designers reluctant to invest in additional chip area solely devoted to debugging and tracing.

The IEEE's Industry Standard and Technology Organization has proposed a standard for a global embedded processor debug interface (Nexus 5001) [2]. This standard specifies four classes of operation – higher numbered classes progressively support more complex debug operations but require more on-chip resources. Class 1 provides basic debug features for run-control debugging, including single-stepping, breakpoints, and access to processor registers and memory while the processor is not running. Class 1 is traditionally implemented through a JTAG interface. However, this approach is time-consuming and obtrusive; it interferes with the dynamic runtime behavior of the program and can cause original bugs to disappear. More importantly, it is not applicable to debugging real-time embedded systems where setting breakpoints is simply not an option. Class 2 provides debug support for nearly

unobtrusive capturing and tracing program execution (control-flow) in real-time.

Class 3 provides support for memory and I/O read/write tracing in real-time, while

Class 4 provides resources for direct processor control through the trace port.

Many embedded processor vendors have developed modules with advanced tracing and debugging capabilities and integrated them into their embedded platforms, e.g., ARM's Embedded Trace Macrocell [6], MIPS's PDTrace [7], and OCDS from Infineon [8]. The trace and debug infrastructure on a chip typically includes logic that captures address, data, and control signals, logic to filter and compress the trace information, buffers to store the traces, and logic that emits the content of the trace buffer through a trace port to an external trace unit or host machine. In this paper we focus on data traces (Class 3 operation in Nexus).

Existing commercially available trace modules rely either on hefty on-chip buffers to store execution traces of sufficiently large program segments, or on wide trace ports that can transfer a large amount of trace data in real-time. However, large trace buffers and/or wide trace ports significantly increase the system complexity and cost. Moreover, the number and speed of I/O pins dedicated to tracing cannot keep pace with the increase in the speed and the number of processor cores and their speed. These challenges are even more important in multi-core systems.

The mTrace project [9] involves developing the next generation of trace compression methods and infrastructure to make continuous, real-time, unobtrusive, and cost-effective program, data, and bus tracing possible in embedded systems. The approach relies on on-chip hardware to record the processor state and corresponding software modules in the debugger.

The goal of this thesis is to develop of a set of tools for collecting execution traces (also called control-flow traces) and memory referencing traces with varying

degrees of flexibility and enable further research in the next generation of hardwaresupporting tracing and debugging in embedded systems.

## 2.4 Challenges and Opportunities

Descriptor orderings in a trace file may differ from run to run for multithreaded programs because the order in which trace descriptors are serialized to a

trace file is not enforced. Each control-flow or memory reference trace collected by an

mTrace tool can be used to reconstruct a thread's execution path. However, the relative timing between each thread is not recorded, and a reconstruction of the execution path from the trace does not accurately describe the order of execution between

each thread. Certain aspects of dynamic program behavior may change for a singlethread program as well. The operating system may choose different virtual addresses for the stack, heap, and code sections of a program. A shared library may be loaded into a different address and operating system signals may not occur at the same

point between execution runs. Furthermore, the behavior of a system call is often a

function of the operating systems current state, which can vary. mTrace does not

guarantee that control trace and memory reference descriptor orderings will reflect

the actual execution and memory reference orderings that occurred at run time.

PinPlay [10] is a set of Pin tools that track thread execution and saves execution instances for *deterministic record-replay*, where the dynamic run time behavior of a program is exactly reproduced in subsequent executions. PinPlay is composed of a logger which records execution of a program to a file called a *pinball*, and a replayer that uses the *pinball* to repeat the captured execution. Other Pin tools can be integrated with PinPlay to correctly capture the dynamic program behavior of multithreaded software. PinPlay could be integrated with the mTrace tool suite to enforce

correct descriptor orderings for multithreaded programs. PinPlay can also solve a performance issue in mTrace. Currently, instructions that write to memory must be protected with a lock, as the act of executing the store instruction and inspecting the memory address that it wrote to is not atomic – a different thread could write to that address before it is inspected. PinPlay removes the need for this lock by redirecting the store value before the instruction is executed.

#### CHAPTER 3

#### RELATED WORK

This chapter describes related work in the area of unobtrusive program tracing schemes and software-based trace compression (Sections 3.1) and hardware-based trace compression (Section 3.2).

### 3.1 Software Trace Compression

A number of software-based trace compression algorithms have been proposed, including PDATS [11] [12], WPP [13], N-tuple [14], and more recently VPC [15], and SBC [5]. The VPC trace compression algorithms [15] are a set of value prediction based algorithms. Each algorithm builds on the success of the previous alogorithm, with VPC1 compressing raw traces with value predictors and VPC2 adding a second compression stage. Most VPC algorithms use value predictors to convert traces into more compressable streams. VPC3 converts raw traces into streams, allowing for a higher compression ratio and faster compression time. VPC4 is the result of optimizations performed on VPC3's predictor table replacement policy and hash function. VPC4 compresses 36 times better, and compresses 53 times faster than bzip2.

A single-pass stream-based compression (SBC) technique [5] was designed and shown to have a compression ratio between 18 and 308 for a subset of the CPU2000 benchmark suite. SBC maintains a relation between instruction addresses and unique instruction streams to they they belong. An instruction stream is a block of consecutively executing instructions, and the compressed instruction trace con-

tains a list of indentifiers for each of these streams. Data traces are captured by recording the data address and number of accesses in each stream. SBC can be implemented in hardware for minor resource and compression ratio trade off.

TCgen [16] is a tool that generates high-performance trace compressors. The user provides a description of the trace format and TCgen translates the specification to an optimized compressor using a selection of value predictors. TCgen is able to use last-value predictors, finite-context-method predictors, and differential-finite-context-method predictors. In addition to a value predictor configuration, TCgen requires a description of the program traces in extended Backus-Naur form. TCgen was tested on a subset of the SPECcpu2000 benchmark suite and was found to outperform VPC3 between 6% to 13%.

### 3.2 Hardware Trace Compression

Hardware trace compression methods usually include architectural extension to the CPU to filter out redundant or unnecessary trace descriptors, before emitting the trace descriptors to a remote system for debugging and replayability. A similar extension is usually maintained in software to keep the state of the debugger consistent with the hardware enhancements. In this section, we summarize proposed hardware techniques for compressing program traces.

Program stream caches and last stream predictors [17] have been proposed as hardware enhancements to filter trace descritpors by exploiting program characteristics. Each basic block is uniquely identified by its starting address (SA) and starting length (SL). In this case a trace descriptor is the pair (SA, SL). A stream detector interrogates the processor's control signals to check when a new program stream is encountered or an exception occurs. A stream descriptor buffer then serial-

izes access to a stream descriptor cache (SDC), which is indexed by the XOR of the stream address and string length. In the event of a cache hit, the set index and way index for the descriptor are sent to the last stream predictor (LSP), which is a simple last event predictor. In the event of a miss a block is evicted in accordance with the replacement policy and the entry is updated. In the event that the LSP makes an incorrect prediction, the set and way indexes are sent to an encoder, which emits a descriptor to the remote debugger. The MiBench [18] benchmark was the target of performance analysis and showed that for a 32 entry SDC, the bits per instruction can vary between .001 (adpcm\_c) and 1.377 (ghostscript).

The Double-Move-To-Front method (DMTF) [19] is a hardware method that uses basic block properties (such as basic block length) to reduce trace sizes. As the name suggests, DMTF makes use of two Move-To-Front [20] transformations, which is used in the popular compression software bzip2. DMTF is designed with two history tables containing basic block length and sizes. When a stream is encountered the first table, mtf1, is searched for a matching stream address and length. If it is not found, the entries are shifted up, the basic block address and length are inserted into the last entry, and a descriptor is traced out. When a basic block is found in the first table the second table is searched in a similar manner. When a miss occurs in this second table, mtf2, the table entry number that the basic block resides in mtf1 is traced out and saved to mtf2. When the correct index is found in mtf2, the mtf2 index is traced out. Decompression is a reversed compression process and occurs in software. Performance analysis for the DMTF method on the MiBench [18] benchmark showed that compression ratios were between 45 (fft) and 1738 ( $adpcm_c$ ) for a 128 entry mtf1 and a 4 entry mtf2. In addition, a last value predictor was used for

the upper 12 bits of the address and a zero hit counter for *mtf2* hit events to decrease descriptor lengths.

TRaptor [3] is a hardware mechanism that reduces the number of trace records required for program replayability through a remote software debugger. TRaptor reduces the number of traces collected a sufficient amount by utilizing a branch outcome predictor, gshare, and a branch target predictor implemented with an indirect branch target buffer and a return address stack. The gshare outcome predictor is organized as an array of two bit adaptive predictors, where each entry is accessed using a function of the branch instruction address and a path information register (PIR) which records the outcomes of previous branches. The return address stack stores the return target address for instructions that return from a subprocedure. The indirect branch target buffer saves the target address for branch instructions whose target address is not inferrable from the branch instruction. Instead of emitting a control flow descriptor for each branch instruction, TRaptor records the number of correctly predicted branchs with the parameter bCnt, and emits a control flow trace descriptor only for incorrectly predicted branches or exceptions. Exceptions require a separate parameter, iCnt, which is incremented for each instruction and is reset if an exception or a branch misprediction occurs. The TRaptor structure is organized to incercept the instruction type, branch instruction address, and branch target address from the target CPU and encode control flow descriptors, when necessary, and send them to a remote host, where an equivalent TRaptor structure in software enables debugging of the target binary. Figure 3.1 contains the algorithm used by TRaptor when presented with a branch instruction. iCnt is incremented for every instruction (line 2) and bCnt is incremented for all branches (line 3). If a prediction is incorrect, a trace descriptor is emitted (lines 6-7), and both iCnt and bCnt are reset. If an exception occurs, a trace is emitted (line 13-14) and both parameters are reset. For multithreaded software, a TRaptor structure can be allocated privately to each thread or shared globally amongst all threads.

```

1. // For each committed instruction in Thread with index i

2. i.iCnt++; // increment iCnt

3. if ((i.iType==IndBr) || (i.iType==DirCB)) {

i.bCnt++; // increment bCnt

if (TRaptor mispredicts) {

Encode mispredicton event;

7.

Place record into the Trace Buffer;

i.iCnt = 0;

9.

i.bCnt = 0;

10. }

11. }

12. if (Exception event) {

13. Encode an exception event;

14. Place record into the Trace Buffer;

15. i.iCnt = 0;

i.bCnt = 0;

17. }

```

Figure 3.1 TRaptor Operation for One Thread (Private/Shared)

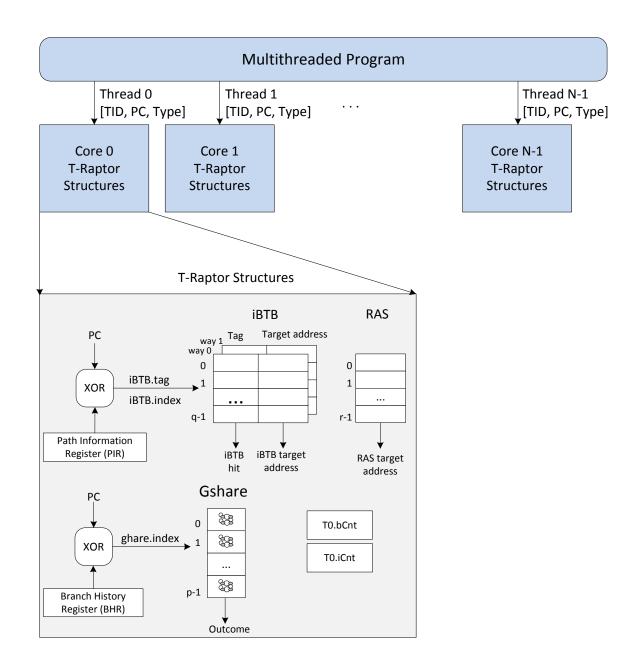

While originally not concerned with multithreaded software, Figure 3.2 depicts how TRaptor strutures can be allocated to each thread privately. Each thread accesses its TRaptor mechanism through its thread ID and presents, depending on the branch type, the instruction address and branch target address. Each thread can access a private gshare, return address stack, and indirect branch target buffer. The bCnt and iCnt parameters are also private to each thread.

Figure 3.2 mcfTRaptor with Private Predictor Structures

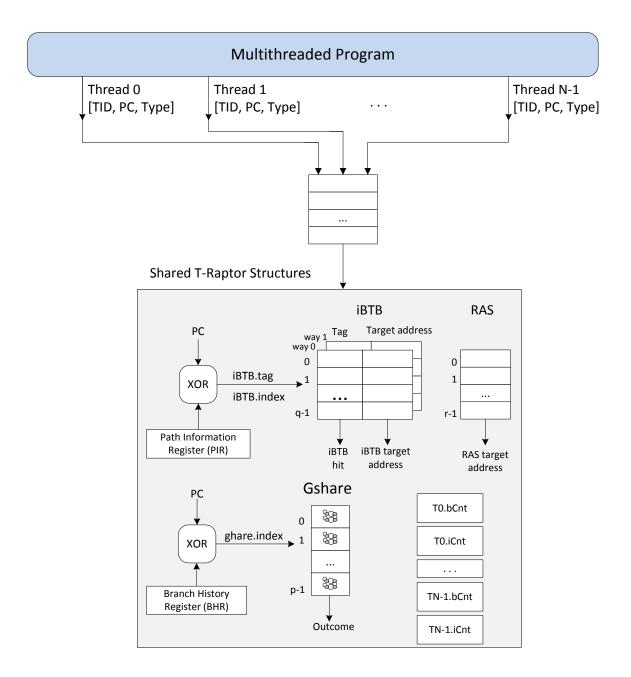

Figure 3.3 depicts TRaptor saring among threads in a multithreaded program. Each access is sequential, with each thread sending the instruction address and branch target to the shared TRaptor structure. The *gshare*, return address

stack, and indirect branch target buffer are shared among all threads, but the bCnt and iCnt parameters are private to each thread, allowing off-line program replayability for each thread.

Figure 3.3 mcfTRaptor with Shared Predictor Structures

CFiat [4] is a hardware-based mechanism that reduces load value traces by collecting a minimal set of load value trace descriptors through the use of a cache first access mechanism. The CFiat, or cache first access, mechanism emits load value descriptors on the first hit or the eviction of a cache block. The CFiat mechanism extends an already existing data cache with first access flags that protect the operands in each cache block. An operand's first access flag is set to one whenever a trace descriptor is emitted for the operand or when the operand is written to memory. Whenever a cache block is evicted, all flags associated with that cache block are set to zero. Whenever a cache hit occurs and the flags associated with the operand are found to be set to one, the *fahCnt* parameter is incremented. This parameter allows for accurate replaying of traces in an off-line debugger. The size of the operand that a flag can protect is referred to as the flag granularity and is a design parameter.

Figure 3.4 lists the cache first access algorithm. Each operand passes through the cache first access mechanism, and if it results in a cache hit, the flags associated with the operand are checked (line 3). If the flags are set, fahCnt is incremented. If the flags are not set, a trace descriptor is eimitted, the flags corresponding to that operand are set, and fahCnt is reset. In the event of a cache miss (line 10), all of the flags associated with cache block are reset, a trace descriptor is emitted, the flags associated just with that operand in the newly retrieved cache block are set, and fahCnt is reset.

```

1. // For each retired load that reads n bytes in thread i

2. if (CacheHit) {

if (corresponding n FA flags are set)

i.fahCnt++;

5.

else {

Emit trace record into Trace Buffer (tid, fahCnt, loadValue);

7.

Set corresponding n FA flags;

8.

i.fahCnt = 0;

10. } else { // cache miss event

Clear FA bits for newly fetched cache block;

12.

Perform steps 5-7;

13. }

14.

15. // For each retired store that writes n bytes

16. Set corresponding n FA bits;

17.

18. // For external invalidation/update request

19. Clear FA bits for entire cache block

```

Figure 3.4 CFiat Operation for One Thread (Private/Shared)

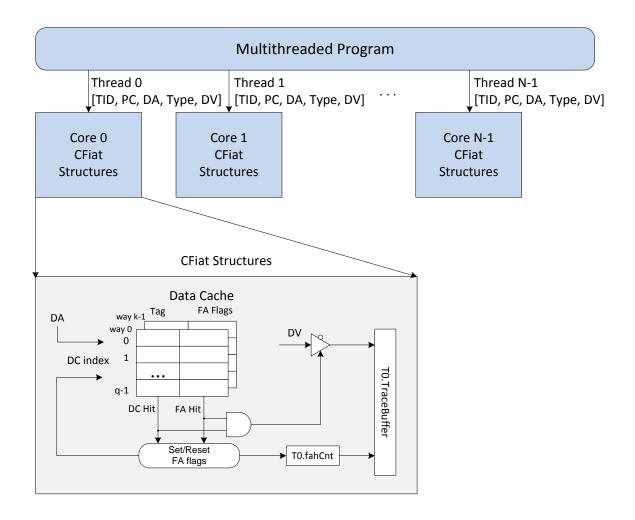

Much like TRaptor, CFiat is organized as a hardware extension, in this case to a data cache. The mechanism emits the encoded load value descriptors to on-chip buffers and trace ports were transmitted to trace probe and host machine, where a software copy of the CFiat mechanism is located. This host machine can replay the program of the target binary. Figure 3.5 depicts the organization of the cache mechanism, with each thread allocated with a private data cache and set of first access flags. Each thread accesses its data cache and first access flags independently and emits trace descriptors when the conditions are met. The threads present the memory referencing instruction's address (PC), the operand address (DA), the operand size (DS), type (read or write), and data value (DV).

Figure 3.5 *mlvCFiat* with Private Cache Structures

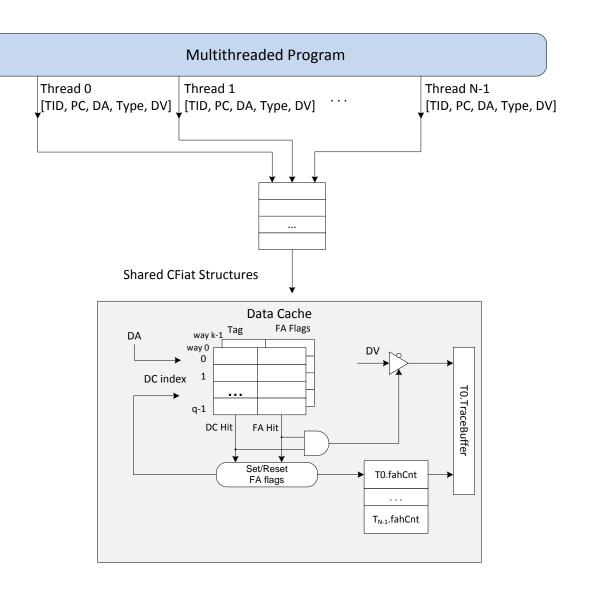

Figure 3.6 depicts sharing of data cache and cache first-access structures among threads in a multithreaded program. Each access is sequential, with each thread sending the instruction address and branch target to the shared data cache. The data cache and first-access bits are shared among all threads, but the *fahCnt* is private to each thread, allowing offline program replayability for each thread.

Figure 3.6  $\,mlvCFiat$  with Shared Cache Structures

### CHAPTER 4

#### MTRACE TOOL SUITE

This chapter introduces a set of software tools for capturing and compressing program traces of multithreaded programs, including both control flow and data traces. The mTrace tool suite runs on systems that use the Intel-64/x86 instruction set architectures and relies on Intel's Pin binary instrumentation tool to capture traces. The mTrace suite encompasses the following tools

- mcfTrace: a tool for capturing and compressing control-flow traces (Section 4.1);

- mlsTrace: a tool for capturing data traces, specifically memory referencing load and store instructions (Section 4.2);

- *mcfTRaptor*: a tool for capturing control-flow traces and compressing them using our *T-Raptor* mechanism that exploits branch predictor structures (Section 4.3);

- *mlvCFiat*: a tool for capturing load value data traces and compressing them using our *C-fiat* mechanism that relies on caches and first-access bits (Section 4.4).

Figure 4.1 *mcfTrace* organization

Figure 4.1 shows the software organization that is shared by all mTrace tools. Starting from the top, the target application is specified (e.g., a multithreaded Ma-

of threads (e.g., in MatrixMultiply we specify the matrix size and the number of threads). We designed the mTrace tools to support a number of parameters for controlling program tracing (mTrace Pin Tool Parameters). To accommodate a wide range of trace uses, we allow users to specify which segment of the target application to trace. This is achieved by specifying the number of instructions executed by the target application before the tracing is turned on. The length of the traced segment is controlled by specifying the number of instructions to be traced. In addition, the user can select the format of trace descriptors to be either binary or ASCII text. Other optional parameters allow the user to specify whether the trace descriptors are written directly to an output trace file or go to a general-purpose compressor to be compressed before writing into a compressed trace file. The subsections below describe individual trace tools. For each trace tool, we first give its functional description, then describe high-level implementation details, and finally discuss test steps taken to verify the correctness of our implementation.

### 4.1 mcfTrace

mcfTrace is a Pin tool designed to collect and save control-flow traces of multithreaded programs to a file. For each control-flow instruction, mcfTrace captures a trace descriptor that consists of the following: a logical thread ID of the issuing thread, the address of the instruction, the branch target address, the type of the control-flow instruction, and its outcome. The trace descriptors can be saved to a binary file or text file, or piped to a general purpose compressor. Section 4.1.1 gives a functional description of the mcfTrace tool. Section 4.1.2 gives a brief description of tool

implementation, and Section 4.1.3 describes verification process and test programs used.

# 4.1.1 Functional Description

Table 4.1 lists the *mcfTrace* tool parameters that allow a user to control instrumentation and tracing. These parameters are used to control the following: (a) the trace file type (binary or ASCII), (b) the code segment and trace scope at the instruction and sub-procedure level, (c) optional compression (d) the maximum trace size, and (e) others.

Table  $4.1 \ mcfTrace$  Parameters

| Parameter                       | Description                                                            |  |

|---------------------------------|------------------------------------------------------------------------|--|

| -a                              | Saves trace descriptors in an ASCII file (default is binary)           |  |

| -c <compressor></compressor>    | Trace descriptors are piped to a general-purpose compressor            |  |

|                                 | before saving. <compressor> = {bzip2, pbzip2, gzip, pigz}</compressor> |  |

| -d                              | Each descriptor includes a corresponding assembly code                 |  |

| -f                              | Trace file size limit in Megabytes. Instrumentation and trace          |  |

|                                 | collecting stops after reaching this limit (default limit is 50        |  |

|                                 | GBytes).                                                               |  |

| -filter_no_shared_libs          | Traces only target binary, shared libraries are not traced.            |  |

| -filter_rtn <routine></routine> | Tracing only occurs in a specified routine(s).                         |  |

| -[h   help]                     | Displays help message with all parameters and their descrip-           |  |

|                                 | tion.                                                                  |  |

| -l <nist></nist>                | Specifies NIST, the number of instructions that will be instru-        |  |

|                                 | mented in the target.                                                  |  |

| -o <fname></fname>              | Specify trace file name, FNAME.                                        |  |

| -s <nist></nist>                | Specifies NIST, the number of instructions to be skipped before        |  |

|                                 | instrumentation begins.                                                |  |

Figure 4.2 illustrates the format of the descriptors collected by *mcfTrace*. A *mcfTrace* binary trace descriptor includes the following fields:

- *Thread ID* field is 1 byte long and encodes threads from 0 to 255;

- Instruction Address and Target Address fields that are 8 bytes long on 64bit architectures include the instruction address and the branch target address, respectively; and

- Type & Outcome field encodes the type of the control-flow instruction and its outcome (taken or not taken). The Intel-64 ISA supports the following branch types: unconditional indirect (Type & Outcome=0), unconditional direct (Type&Outcome = 1), conditional direct taken (Type&Outcome = 2), and conditional direct not taken branches (Type&Outcome = 3).

Except for address sizes (which depend on the system's address size), binary descriptors do not have any variable fields and a binary file can be easily decoded by applying this descriptor format. For Intel-64 architectures, a *mcfTrace* binary descriptor uses exactly 18 bytes.

mcfTrace ASCII descriptors also include Thread ID, Instruction Address, Target Address, Type&Outcome fields, as well as optional assembly code. Individual fields in a descriptor are separated by a comma and individual descriptors are separated by a new line character. Figure 4.2 gives an example of an ASCII descriptor, which specifies that thread 0 issued an instruction at address 0x0000003f\_83200b03, and that the instruction is an unconditional direct branch (U, D, T) with the target address 0x0000003f\_83201130. In this case we opted to print out the assembly instruction for the descriptor, which is a call instruction.

mcfTrace Descriptor: Binary

**Format**

| Thread ID<br>(1 Byte) | Instruction<br>Address<br>(8 Bytes) | Target Address<br>(8 Bytes) | Type&Outcome<br>(1 Byte) |

|-----------------------|-------------------------------------|-----------------------------|--------------------------|

|-----------------------|-------------------------------------|-----------------------------|--------------------------|

mcfTrace Descriptor: ASCII

**Format**

| Thread ID<br>(up to 4 Bytes) | Instruction<br>Address<br>(20 Bytes) | Target Address<br>(20 Bytes) | Type&Outcome<br>(8 Bytes) | Assembly Code<br>(Variable) |

|------------------------------|--------------------------------------|------------------------------|---------------------------|-----------------------------|

|------------------------------|--------------------------------------|------------------------------|---------------------------|-----------------------------|

Example: 0, 0x0000003f83200b03, 0x0000003f83201130, U, D, T call 0x3f83201130

Figure 4.2 *mcfTrace* Descriptor Formats: Binary (top) and ASCII (bottom).

Figure 4.3 contains an example output from *mcfTrace*. In this example, *mcfTrace* creates the trace file, mcfTrace.out2013\_8\_31\_15.4.1.txt, as well as a text file, mcfTrace.out2013\_8\_31\_15.4.1.Statistics, which contains statistics relating to the branch trace descriptors that are captured. The user can specify an output trace file name or the file name is generated automatically using a time stamp. A selected segment of the output trace file is shown in lines 9-19. The statistics file contains information about the number and types of individual branch instructions as shown in lines 2-8.

```

1. [myersar@EB245-mhealth3 ManualExamples]$ head mcfTrace.out2013 8 31 15.4.1.Statistics

1. mcfTrace: Traced 1000000 instructions

2. mcfTrace: Skipped 3000000 instructions

3. mcfTrace: Recorded 269334 control transfer instructions.

4968 ( %1.84 ) Unconditional Direct

129517 ( %48.09 ) Conditional Direct Taken

6.

131116 ( %48.68 ) Conditional Direct Not Taken

3733 ( %1.39 ) Unconditional Indirect

8. [myersar@EB245-mhealth3 ManualExamples]$ head mcfTrace.out2013 8 31 15.4.1.txt

9. 1, 0x00007f5a40996bbe, 0x00007f5a40996be4, C, D, NT

10. 1, 0x00007f5a40996bc9, 0x00007f5a40996bb8, C, D, T

11. 1, 0x00007f5a40996bbe, 0x00007f5a40996be4, C, D, NT

12. 2, 0x00007f5a40996bc9, 0x00007f5a40996bb8, C, D, T

13. 1, 0x00007f5a40996bc9, 0x00007f5a40996bb8, C, D, T

14. 1, 0x00007f5a40996bbe, 0x00007f5a40996be4, C, D, NT

15. 1, 0x00007f5a40996bc9, 0x00007f5a40996bb8, C, D, T

16. 3, 0x00007f5a40996bc9, 0x00007f5a40996bb8, C, D, T

17. 1, 0x00007f5a40996bbe, 0x00007f5a40996be4, C, D, NT

18. 2, 0x00007f5a40996bbe, 0x00007f5a40996be4, C, D, NT

```

Figure 4.3 *mcfTrace* Example Output

## 4.1.2 Implementation Details

mcfTrace instruments applications at the instruction level by recompiling basic blocks on a just in time basis with analysis routines that are inserted before branch instructions. mcfTrace collects branch instruction data by passing the logical thread ID of the executing thread, the address of the branch instruction, its target (whether static or indirect), the type of branch instruction, and branch outcome as arguments to these analysis routines.

The Intel 64 and IA-32 instruction set [21] control transfer instructions include conditional and unconditional jump instructions, a subroutine call instruction, and a subroutine return instruction. Table 4.2 depicts the three classifications used by *mcfTrace* when collecting descriptors.

Table 4.2 Intel 64 and IA-32 Control Transfer Instruction Classification

|                        | Operand                   | Instruction               |

|------------------------|---------------------------|---------------------------|

|                        |                           | Mnemonics                 |

| Conditional Direct     | Memory                    | jnbe, jnb, jb, jz,, etc.  |

|                        |                           | loop, loope, loopne, etc. |

| Unconditional Direct   | Memory                    | jmp, call,                |

| Unconditional Indirect | Register Indirect, Memory | jmp, call, rtn            |

The j\* and loop\* instructions use labels which reference addresses that are generated by a linker and are considered static since they do not change during runtime. These two groups of instructions are also conditional and use condition codes kept in the status registers. Both the *jump* and *call* instructions can either use labels or registers to specify the target address, thus can be classified as either unconditional direct or unconditional indirect control instructions. The *rtn* instruction uses a target referenced by a stack register and is considered indirect.

Figure 4.4 shows the code segment in mcfTrace.cpp that instruments a target to capture control-flow traces and write trace descriptors to an ASCII file.

mcfTrace.cpp contains routines that instrument the target and perform other housekeeping roles such as initializing Pin and detaching Pin from the target. Similar instrumentation code is used when writing to a binary file. The Pin instruments over basic blocks (line 1) and then iterates over individual instructions within the basic block (line 3). Line 5 of the code inserts the SetFastForwardAndLength analysis procedure that counts the number of instructions executed in the target. This procedure allows us to implement fast forwarding and trace length control functions. If we are fast forwarding, this analysis function simply counts the number

of instructions left to skip until tracing begins. If we are tracing, SetFastForwardAndLength counts the number of instructions executed while tracing. Lines 8-23 use Pin calls to filter the different branch instruction classes as described in Table 4.2. The HasFallThrough Pin function is true for instructions that potentially do not change control flow and can be used to decide between conditional and unconditional branches. IARG\_THREAD\_ID passes the logical ID of calling thread,

IARG\_THREAD\_PTR passes the address of branch instruction,

IARG\_BRANCH\_TARGET\_ADDR passes the target of the branch instruction, and

IARG\_BRANCH\_OUTCOME passes whether or not the branch was taken (only used for conditional branches).

```

1. for(BBL bbl = TRACE BblHead(trace); BBL Valid(bbl); bbl = BBL Next(bbl) )

3.

for(INS ins = BBL_InsHead(bbl); INS_Valid(ins); ins = INS_Next(ins) )

4.

INS InsertCall(ins, IPOINT BEFORE, (AFUNPTR)SetFastForwardAndLength,

5.

IARG THREAD ID, IARG END);

6.

7.

8.

if( INS_IsDirectBranchOrCall(ins) && !INS_HasFallThrough(ins) )

9.

INS_InsertCall(ins, IPOINT_BEFORE,

10.

(AFUNPTR) Emit UnconditionalDirect ASCII,

//Args: Thread ID, Instruction Address, Target Address

IARG THREAD ID, IARG INST PTR, IARG BRANCH TARGET ADDR,

12.

13.

IARG_END);

14.

15.

// Is Conditional and Direct

else if( INS_IsDirectBranchOrCall(ins) && INS_HasFallThrough(ins) )

16.

INS InsertCall(ins, IPOINT BEFORE, (AFUNPTR)Emit ConditionalDirect ASCII,

17.

//Args: Thread ID, Instruction Address, Target Address, Taken?

18.

IARG THREAD ID, IARG INST PTR, IARG BRANCH TARGET ADDR,

19.

IARG BRANCH TAKEN, IARG END);

20.

21.

22.

else if( INS IsIndirectBranchOrCall(ins) || INS IsRet(ins) )

23.

INS InsertCall(ins, IPOINT BEFORE,

(AFUPTR) Emit UnconditionalIndirect ASCII,

24.

25.

//Args: Thread ID, Instruction Address, Target Address

26.

IARG THREAD ID, IARG INST PTR, IARG BRANCH TARGET ADDR,

27.

IARG END);

28. }

```

Figure 4.4 mcfTrace Instrumentation Implementation from mcfTrace.cpp

Figure 4.5 contains an example of an analysis routine found in mcfTrace.h, which only contains analysis routines injected with mcfTrace.cpp. This routine passes es pertinent branch instruction data to a buffer which is later written to a binary file. The CanEmit (line 4) function returns early if tracing is not enabled and will detach mcfTrace from the target process if the tracing is finished or the file size limit is reached. Lines 6-21 create the binary trace descriptor from the information passed

during instrumentation, and lines 24-28 push the descriptor on an STL container which will be written to file at a later point. The STL container is shared between the target's threads and must be protected with a lock.

```

1. VOID Emit_ConditionalDirect_Bin(const THREADID threadid, const ADDRINT address,

2.

const ADDRINT target, const BOOL taken)

3.

if( !CanEmit(threadid) ) return;

5.

6.

//setup descriptor

7.

BinaryDescriptorTableEntry binDescriptor;

binDescriptor.tid = *static cast<UINT8*>(Pin GetThreadData(tls key, threadid));

9.

binDescriptor.branchAddress = address;

10.

binDescriptor.targetAddress = target;

//If taken paramater will be non-zero

12.

if(taken == 0)

13.

14.

IncrementBranchStatistics(ConditionalDirectNotTaken);

binDescriptor.branchType = ConditionalDirectNotTaken;

16.

}

17.

else

18.

19.

IncrementBranchStatistics(ConditionalDirectTaken);

20.

binDescriptor.branchType = ConditionalDirectTaken;

21.

22.

23.

//critical section

GetLock(&table_lock, threadid+1);

24.

25.

binDescriptorTable.push back(binDescriptor);

//increment file counter

27.

IncrementFileCount(BinDescriptorTableEntrySize);

ReleaseLock(&table_lock);

29.}

```

Figure 4.5 Analysis Routine from *mcfTrace*

Figure 4.6 includes the section of mcfTrace that writes trace descriptors to file. Because mcfTrace can create arbitrarily large control-flow traces, it creates a

thread to empty the STL container whenever possible. ThreadWriteBin is this thread's function and is launched before the target is instrumented. Lines 12-22 and 32-42 write the descriptor to file or pipe it to a compressor. The Pin\_IsProcessExiting (Lines 10 and 30) call is used to kill the thread whenever mcfTrace detaches from the target process. ThreadWriteBin is used in every mTrace tool.

```

VOID ThreadWriteBin(VOID *arg)

2. {

3.

THREADID threadid = Pin_ThreadId();

4.

if(usingCompression)

5.

{

while(1)

6.

7.

8.

//if process is closing (entered fini()) kill thread

9.

if( Pin_IsProcessExiting() )

Pin ExitThread(1);

10.

11.

12.

GetLock(&table lock, threadid+1);

13.

while( !binDescriptorTable.empty() )

14.

15.

BinaryDescriptorTableEntry temp = binDescriptorTable.front();

fwrite(&temp.tid, sizeof(temp.tid), 1,outPipe);

16.

fwrite(&temp.branchAddress, sizeof(temp.branchAddress), 1, outPipe);

17.

fwrite(&temp.targetAddress, sizeof(temp.targetAddress), 1, outPipe);

18.

fwrite(&temp.branchType, sizeof(temp.branchType), 1, outPipe);

19.

binDescriptorTable.pop front();

20.

21.

}

ReleaseLock(&table lock);

23.

24.

25.

else

26.

27.

while(1)

28.

29.

if( Pin_IsProcessExiting() )

30.

Pin_ExitThread(1);

31.

32.

GetLock(&table lock, threadid+1);

while( !binDescriptorTable.empty() )

33.

34.

35.

BinaryDescriptorTableEntry temp = binDescriptorTable.front();

36.

OutFile.write((char *)&temp.tid, sizeof(temp.tid));

OutFile.write((char *)&temp.branchAddress, sizeof(temp.branchAddress));

37.

38.

OutFile.write((char *)&temp.targetAddress, sizeof(temp.targetAddress));

OutFile.write((char *)&temp.branchType, sizeof(temp.branchType));

39.

40.

binDescriptorTable.pop_front();

41.

ReleaseLock(&table lock);

43.

44.

45.}

```

Figure 4.6 mcfTrace Write Routine

#### 4.1.3 Verification/Test

mcfTrace was tested using two assembly code programs, BranchEnumeration.s and BranchTest.s. BranchEnumeration contains all of the x86\_64 branch instructions to ensure that mcfTrace collects the correct branch instruction information for each branch. The Intel-64 and x86 instruction sets [21] list branch instructions not shown in BranchEnumeration.s, but they are really mnemonics for the instructions already provided, e.g. the ja instruction is really a jnbe instruction.

Figure 4.7 contains a small selection of conditional branch instructions from BranchEnumeration.s. Part one of this test program lists branch instructions belonging to the j\* conditional jump family and part two contains conditional branch instructions belonging to the loop\* branch family. These four branches are not taken and will be reported consecutively by mcfTrace. Figure 4.8 contains the branch descriptors from mcfTrace for this section of code. All four branch instruction descriptors are shown correctly as conditional direct branches that are not taken. Figure 4.9 contains a section of unconditional branches from BranchEnumeration.s. In this case, the jmp and call instructions are unconditional direct branches, while the rtn instruction is an unconditional indirect branch.

```

1. #Part 1

2. #unsigned conditional direct branches

3. #all branches will not be taken

4. #branch if strictly above

5. #Taken when CF and ZF are both zero

rax, 1

mov

7. cmp

rax, 2

8. jnbe exit1

9. #branch if above or equal

10. # Taken when CF is 0

11. jnb

exit1

12. #Part 2

13. #More conditional branch instructions

14. #Loop family

15. mov rcx, 1

16. loop1:

17. loop loop1

18. mov rcx, 1

19. loop2:

20. loope loop2

21. mov rcx, 1

```

Figure 4.7 Selection from BranchEnumeration.s

```

mcfTrace ASCII Output, with disassembly:

0, 0x00000000004004d3, 0x00000000040059e, C, D, NT jnbe 0x40059e

0, 0x00000000004004d9, 0x00000000040059e, C, D, NT jnb 0x40059e

0, 0x0000000000400572, 0x000000000400572, C, D, NT loop 0x400572

0, 0x000000000040057b, 0x00000000040057b, C, D, NT loope 0x40057b

```

Figure 4.8 mcfTrace output for BranchEnumeration.s selection

```

1. #Unconditional Direct jump

qmp

Label1

3. #Not Executed

test rax, rax

5.

6. Label1:

7. #setup puts

mov edi, OFFSET FLAT:.LC0

9. #unconditional direct branch - call

10.

call

puts

11. exit1:

12.

leave

13.

.cfi_def_cfa 7, 8

14.

Ret

```

Figure 4.9 Unconditional branches from BranchEnumeration.s

Figure 4.10 contains the relevant *mcfTrace* output for this section of BranchEnumeration.s. The targets for the *jmp* and *call* instructions match the addresses shown in their assembly mnemonic. The *ret* instruction is indirect and the target shown in the descriptor was taken from the stack.

Next, *mcfTrace* was tested with BranchTest.s, which creates more sophisticated branch contexts. Figure 4.12 contains a sample of BranchTest.s. In Lines 1-12 we take several successful branches before falling through to an indirect call instruction at line 22.

```

mcfTrace ASCII Output, with disassembly:

0, 0x0000000000040058f, 0x000000000400594, U, D, T jmp 0x400594

0, 0x0000000000400599, 0x0000000004003b8, U, D, T call 0x4003b8

0, 0x0000000000040059f, 0x00007f688ca5ce5d, U, I, T ret

```

Figure 4.10 mcfTrace output for BranchEnumeration.s section

```

1. Label1:

mov

rax, 2

3.

cmp

rax, 1

jnbe Label2

5.

test rax, rax

6. Label2:

7.

cmp rax, 2

jz Label3

8.

9. Label3:

10.

mov rcx, 5

11. Label4:

12.

loop Label4

13.

14.

#setup puts

15.

mov edi, OFFSET FLAT:.LC0

16.

17.

#unconditional direct branch - call

18.

call

puts

19.

20.

#unconditional indirect branch - call

21.

rax, OFFSET FLAT:test

22.

call rax

23.

leave

.cfi def cfa 7,8

25.

26.

27.

#indirect taken branch

28.

29.

.cfi_endproc

```

Figure 4.11 Selection from BranchTest.s and *mcfTrace* output

Figure 4.12 lists the correct descriptors for the code shown in Figure 4.11. The first six descriptors map to the branches taken in lines 1-12 in Figure 4.11. The seventh descriptor is a branch that exits the loop in lines 11-12 and the last descriptor is an indirect call shown that is set up and executed in lines 21 and 22.

```

1. 0, 0x00000000004004ec, 0x0000000004004f1 C, D, T

jnbe 0x4004f1

0, 0x0000000004004f5, 0x0000000004004f7 C, D, T

jz 0x4004f7

3. 0, 0x0000000004004fe, 0x0000000004004fe C, D, T

loop 0x4004fe

0, 0x00000000004004fe, 0x0000000004004fe C, D, T

loop 0x4004fe

0, 0x00000000004004fe, 0x0000000004004fe C, D, T

loop 0x4004fe

0, 0x00000000004004fe, 0x0000000004004fe C, D, T

loop 0x4004fe

0, 0x0000000004004fe, 0x0000000004004fe C, D, NT

loop 0x4004fe

0, 0x000000000400511, 0x0000000004004c4 U, I, T

call rax

```

Figure 4.12 Selection from BranchTest.s and mcfTrace output

#### 4.2 mlsTrace