## ALGORITHMS AND HARDWARE STRUCTURES FOR REAL-TIME COMPRESSION OF PROGRAM TRACES

by

### **VLADIMIR UZELAC**

### **A DISSERTATION**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

**HUNTSVILLE, ALABAMA**

2010

| In presenting this dissertation in partial fulfillment of the requirements for a doctoral     |

|-----------------------------------------------------------------------------------------------|

| degree from The University of Alabama in Huntsville, I agree that the Library of this         |

| University shall make it freely available for inspection. I further agree that permission for |

| extensive copying for scholarly purposes may be granted by my advisor or, in his/her          |

| absence, by the Chair of the Department or the Dean of the School of Graduate Studies. It     |

| is also understood that due recognition shall be given to me and to The University of         |

| Alabama in Huntsville in any scholarly use which may be made of any material in this          |

| dissertation.                                                                                 |

|                                                                                               |

|                                                                                               |

|                                                                                               |

| (student signature) | (date) |  |

|---------------------|--------|--|

### DISSERTATION APPROVAL FORM

Submitted by Vladimir Uzelac in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this dissertation. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering.

| (Da | Committee Chair (ate) |

|-----|-----------------------|

|     |                       |

|     |                       |

|     |                       |

|     |                       |

|     |                       |

|     |                       |

|     |                       |

|     |                       |

|     | Department Chair      |

|     | Callaga Daan          |

|     | College Dean          |

|     | Graduate Dean         |

# **ABSTRACT**

### The School of Graduate Studies The University of Alabama in Huntsville

| Degree <u>Doctor of I</u>  | <u>Philosophy</u>                      | College/Dept. Engineering/Electrical and                 |

|----------------------------|----------------------------------------|----------------------------------------------------------|

|                            |                                        | Computer Engineering                                     |

| Nama of Candidata          | VIa dimin I Imala a                    |                                                          |

|                            | Vladimir Uzelac<br>s and Hardware Stru | ctures for Real-Time                                     |

|                            | on of Program Trace                    |                                                          |

| -                          | -                                      |                                                          |

| Rising complexity          | of both hardware ar                    | nd software of modern embedded systems-on-a-chip         |

| makes software develo      | pment and system vo                    | erification the most critical step in a system           |

| development. To expe       | edite system verificat                 | ion and program debugging chip manufacturers             |

| increasingly pay attent    | ion to hardware infra                  | astructure for program debugging and tracing. The        |

| program tracing infras     | tructure includes log                  | ic to capture program execution traces, buffers to store |

| traces on the chip and     | a trace port through                   | which the trace is read by the debug tools. In order to  |

| cope with the size and     | bandwidth requirem                     | ents for the real-time tracing, hardware compression of  |

| traces is required. In the | his dissertation, we p                 | present and analyze methods for on-the-fly               |

| compression of three c     | omponents of the pro                   | ogram (software) trace: addresses of executed            |

| instructions, addresses    | of memory reference                    | ing instructions and results of memory load              |

| instructions – the data    | brought to the syster                  | n. We introduce a number of new algorithms for           |

| compression of individ     | lual trace component                   | s and explore their design space. We demonstrate that    |

| the proposed hardware      | trace compressors e                    | nable unobtrusive program tracing in real-time at the    |

| minimal additional har     | dware cost.                            |                                                          |

| Abstract Approval:         | Committee Chair                        |                                                          |

|                            | Department Chair                       |                                                          |

|                            | Graduate Dean                          |                                                          |

#### **ACKNOWLEDGMENTS**

I would like to express my deepest gratitude to my advisor, Dr. Aleksandar Milenković, for his excellent guidance, care and patience from the very first day of my graduate studies. He was a great advisor in my professional and private life, and he helped me easily overcome all the hurdles and challenges during the four years of my studies. He guided me on how to write conference and journal papers and he spent countless hours proofreading my research papers and discussing the results of my research.

Also, I would like to thank Dr. Emil Jovanov and Dr. Reza Adhami, for their financial help and support I received from the very first day of my graduate studies. While working as a teaching assistant for Dr. Jovanov, I had an opportunity to learn many valuable skills in embedded system design. I would like to thank Dr. Jeffrey Kulick who showed great interest in my education and research and helped me with his expertise and advice. During my studies at The University at Alabama in Huntsville, I have had contacts with many students, faculty and staff. Their friendly and supportive attitude was of great help, and I thank all of them.

In the past four years my wife was responsible for managing all other aspects of our life, enduring with me through the bad and good. Her patience and emotional stability made my commitment to this research possible. Thank you Tijana for all your support and love.

# **TABLE OF CONTENTS**

|                                            | Page |

|--------------------------------------------|------|

| LIST OF FIGURES                            | x    |

| LIST OF TABLES                             | xii  |

| CHAPTER                                    |      |

| 1 INTRODUCTION                             | 1    |

| 1.1 Software Debugging Challenges          | 2    |

| 1.2 The Case for Hardware Tracing          | 4    |

| 1.3 The Case for Trace Compression         | 6    |

| 1.4 Contributions                          | 7    |

| 1.5 Outline                                | 8    |

| 2 PROGRAM TRACING: BACKGROUND              | 10   |

| 2.1 Types of Tracing                       | 11   |

| 2.1.1 Software Tracing                     | 11   |

| 2.1.2 Hardware Tracing                     | 12   |

| 2.2 Hardware Supported Unobtrusive Tracing | 14   |

| 2.2.1 CPU Trace Signals                    | 15   |

| 2.2.2 Trace Module Details                 | 16   |

| 2.2.3 Tracing and Debugging Protocols      | 18   |

| 2.3 Hardware Trace Infrastructure Examples | 22   |

| 2.3.1   | OCP-IP Debug                                                      | . 22 |

|---------|-------------------------------------------------------------------|------|

| 2.3.2   | Hardware/Software (Hybrid) Tracing                                | . 25 |

| 2.3.3   | Hardware Based Debugging Infrastructure                           | . 26 |

| 3 TRACE | COMPRESSION ALGORITHMS                                            | . 29 |

| 3.1     | General-Purpose Compression Algorithms                            | . 30 |

| 3.1.1   | gzip                                                              | . 30 |

| 3.1.2   | bzip2                                                             | . 31 |

| 3.1.3   | Sequitur                                                          | . 32 |

| 3.2     | Specialized Algorithms for Instruction and Data Trace Compression | . 32 |

| 3.2.1   | Instruction Address Trace Compression.                            | . 33 |

| 3.2.2   | Data Address Compression                                          | . 34 |

| 3.2.3   | Data Value Prediction                                             | . 37 |

| 3.3     | Compression Algorithms in Hardware                                | . 39 |

| 3.3.1   | Architectural Support for Trace Compression                       | . 41 |

| 4 COMPR | ESSION OF PROGRAM EXECUTION TRACES                                | . 43 |

| 4.1     | System View of the Proposed Tracing Mechanism                     | . 43 |

| 4.2     | Characterization of Control Flow Changes                          | . 46 |

| 4.3 I   | Oouble Move-To-Front Method                                       | . 49 |

| 4.3.1   | Move-to-Front Transformation                                      | . 50 |

| 4.3.2   | DMTF Method                                                       | . 53 |

| 4.3.3   | Enhanced DMTF Method                                              | . 58 |

| 4.3.4   | Trace Port Bandwidth Analysis                                     | . 62 |

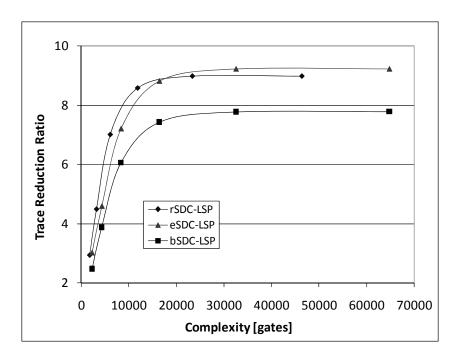

| 4.3.5   | Hardware Implementation and Complexity                            | . 64 |

| 4.4    | Stream Descriptor Cache and Last Stream Predictor            | 65  |

|--------|--------------------------------------------------------------|-----|

| 4.4.   | 1 Compressor Organization                                    | 66  |

| 4.4.   | 2 Design Space Exploration                                   | 73  |

| 4.4.   | 3 Enhancements for Base SDC-LSP Scheme                       | 78  |

| 4.4.   | 4 Trace Port Bandwidth Analysis                              | 83  |

| 4.4.   | 5 Hardware Implementation and Complexity                     | 86  |

| 4.5    | Program Execution Tracing using Branch Predictors            | 88  |

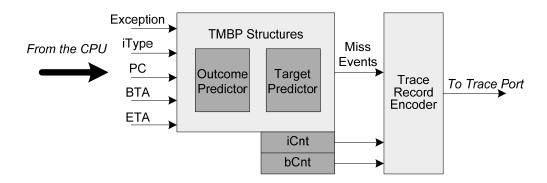

| 4.5.   | 1 Trace Module Branch Predictor                              | 89  |

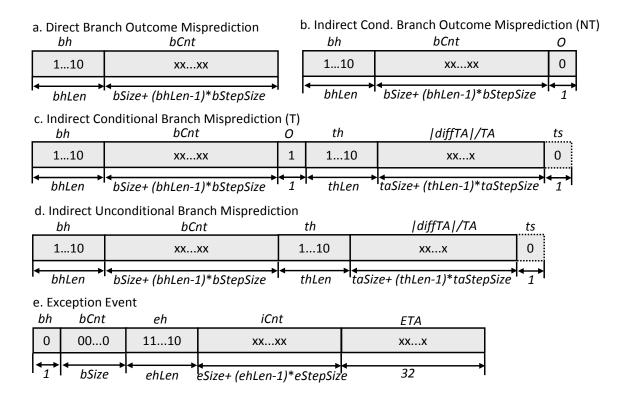

| 4.5.   | 2 Trace Record Encoding                                      | 95  |

| 4.5.   | 3 Trace Port Bandwidth Analysis                              | 99  |

| 4.5.   | 4 Hardware Implementation and Complexity                     | 101 |

| 4.6    | Comparative Analysis                                         | 102 |

| 5 COMP | RESSION OF DATA ADDRESSES                                    | 107 |

| 5.1    | Data Address Filtering                                       | 108 |

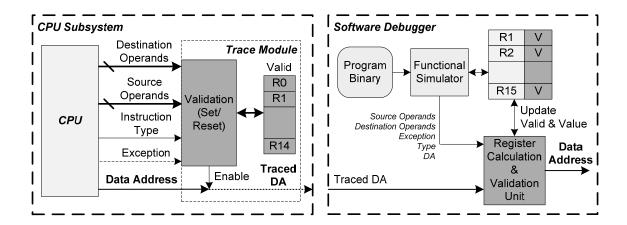

| 5.1.   | 1 Data Address Filtering Details                             | 109 |

| 5.1.   | 2 Addressing Modes and Register Validation                   | 114 |

| 5.1.   | 3 Experimental Evaluation                                    | 117 |

| 5.2    | Adaptive Data Address Cache                                  | 123 |

| 5.2.   | 1 Variability of High-Order Data Address Bits                | 126 |

| 5.2.   | 2 Adaptive Data Address Cache                                | 130 |

| 5.2.   | 3 Design Space Exploration and Trace Port Bandwidth Analysis | 133 |

| 5.3    | Comparative Analysis                                         | 137 |

| SLOAD  | VALUES COMPRESSION                                           | 140 |

| 6.1 D    | Oata Values Compressibility                          | 142 |

|----------|------------------------------------------------------|-----|

| 6.1.1    | Entropy of Load Values                               | 142 |

| 6.1.2    | Variability of High-order Bits                       | 145 |

| 6.1.3    | Compression of Small Load Values Only                | 147 |

| 6.2 C    | Compression Using First-Access Cache Track Mechanism | 149 |

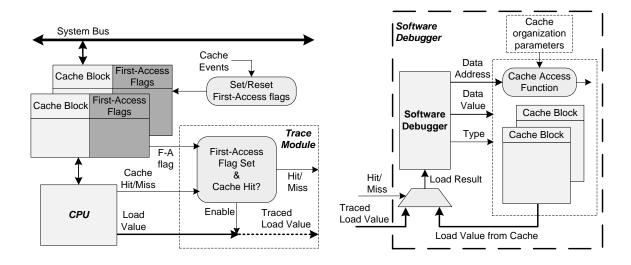

| 6.2.1    | First-Access Track Mechanism Details                 | 151 |

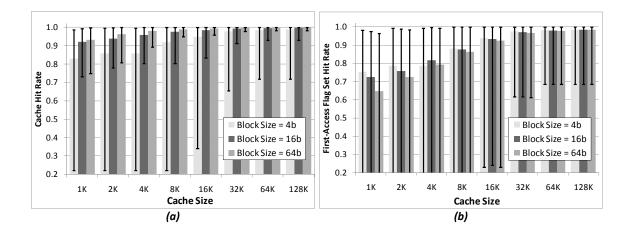

| 6.2.2    | Results and Analysis                                 | 154 |

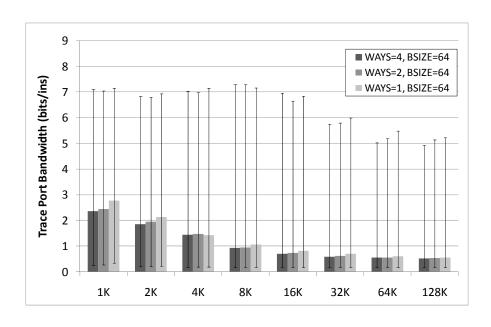

| 6.2.3    | Dedicated First-Access Tracking Scheme               | 156 |

| 6.3 P    | utting It All Together                               | 158 |

| 7 CONCLU | JSIONS AND FUTURE WORK                               | 161 |

| REFEREN  | CES                                                  | 165 |

# LIST OF FIGURES

| Figu | ire                                                                        | Page |

|------|----------------------------------------------------------------------------|------|

| 1.1  | System-on-Chip Observability                                               | 3    |

| 1.2  | Observability of SoC operation using different types of traces             | 6    |

| 2.1  | System view of the hardware support for unobtrusive program tracing        | 13   |

| 2.2  | Nexus system level organization                                            | 22   |

| 2.3  | System view of BugNet architecture                                         | 26   |

| 2.4  | System view of ARM's CoreSight architecture.                               | 28   |

| 4.1  | System view of the proposed program tracing and replay mechanism           | 45   |

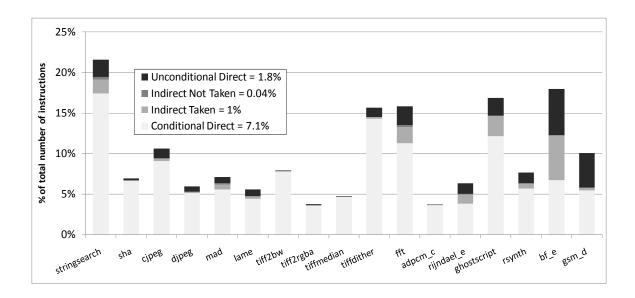

| 4.2  | MiBench branch related statistics                                          | 47   |

| 4.3  | Stream Detector operation                                                  | 48   |

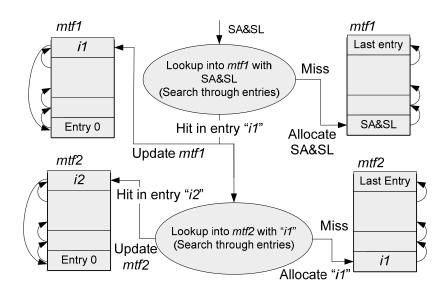

| 4.4  | DMTF operation                                                             | 54   |

| 4.5  | DMTF compression (a) and decompression (b) flow examples                   | 57   |

| 4.6  | An enhanced DMTF trace format                                              | 61   |

| 4.7  | Trace port bandwidth as a function of the <i>mtf1</i> size                 | 62   |

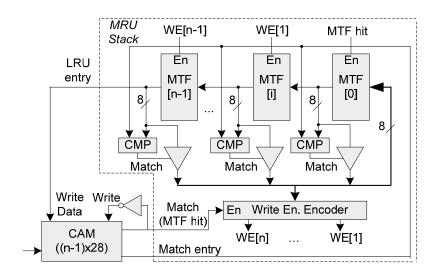

| 4.8  | MTF hardware implementation                                                | 65   |

| 4.9  | System view of Stream Cache with Last Stream Predictor compressor          | 66   |

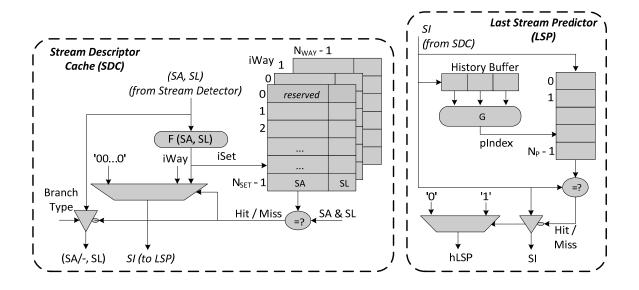

| 4.10 | Trace module structures: Stream Descriptor Cache and Last Stream Predictor | 67   |

| 4.11 | Stream Descriptor Cache operation                                          | 68   |

| 4.12 Last Stream Predictor operation                                                     | 69  |

|------------------------------------------------------------------------------------------|-----|

| 4.13 A compression/decompression example                                                 | 72  |

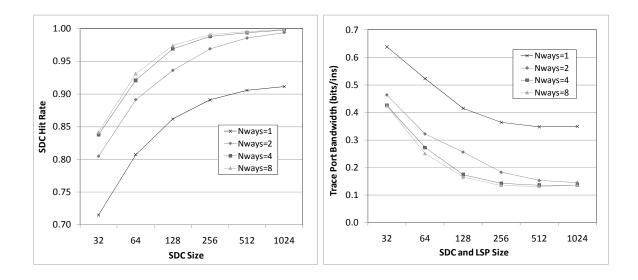

| 4.14 SDC hit rate and trace port bandwidth as functions of its size and organization     | 75  |

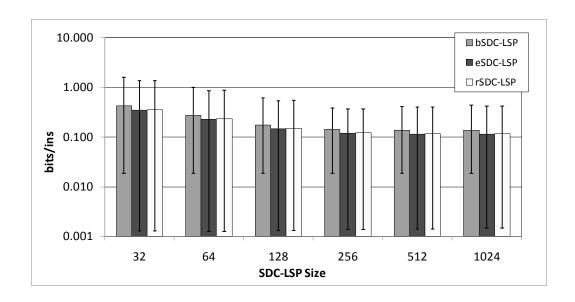

| 4.15 Trace port bandwidth of all proposed schemes.                                       | 85  |

| 4.16 Trace reduction ratio vs. complexity for the three proposed schemes                 | 87  |

| 4.17 Trace module: a system view                                                         | 90  |

| 4.18 Trace module operation                                                              | 91  |

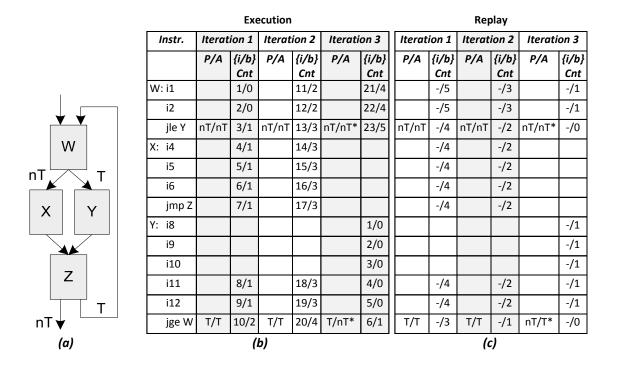

| 4.19 Program execution replay in software debugger                                       | 93  |

| 4.20 Tracing and replaying program execution example                                     | 95  |

| 4.21 Trace record formats for branch misprediction events and exceptions                 | 97  |

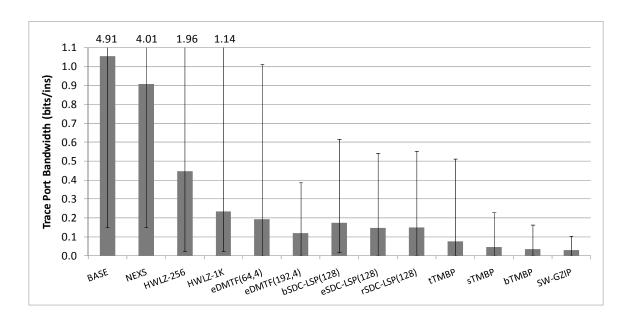

| 4.22 Trace port bandwidth evaluation for proposed and related mechanisms                 | 104 |

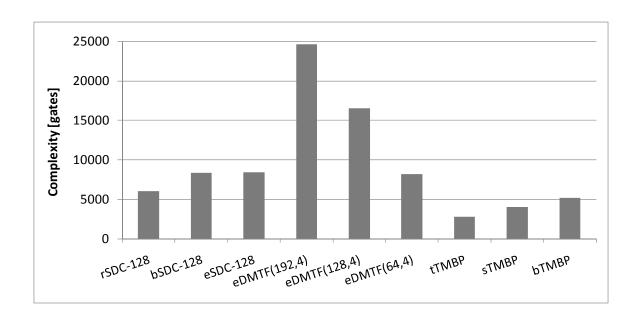

| 4.23 Implementation complexity of proposed tracing mechanisms                            | 105 |

| 5.1 Data address trace filtering: A system view                                          | 114 |

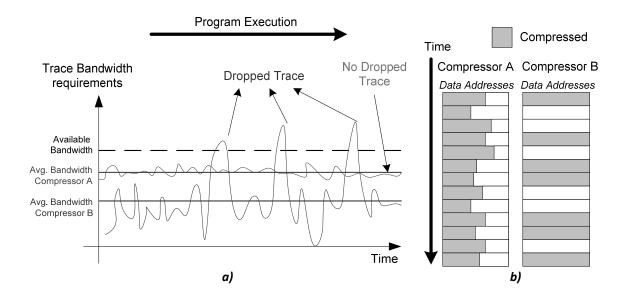

| 5.2 Trace bandwidth requirements (a) and compressor effectiveness (b)                    | 125 |

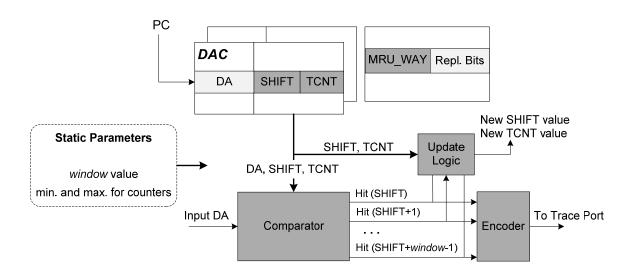

| 5.3 Adaptive Data Address Cache organization                                             | 130 |

| 5.4 Adaptive Data Address Cache operation                                                | 132 |

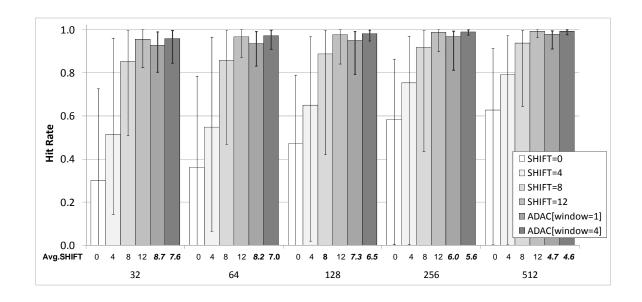

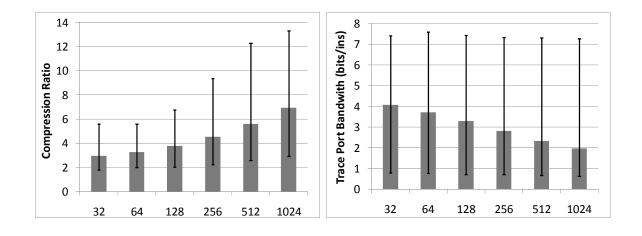

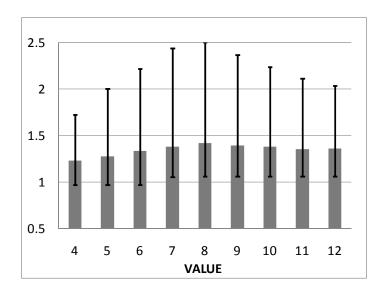

| 5.5 Average hit rates for different DAC-based compressors                                | 136 |

| 5.6 Average compression ratio and trace port bandwidth for ADAC                          | 136 |

| 6.1 Compression ratio when using optimal length for load values encoding                 | 149 |

| 6.2 System view of the first-load track mechanism                                        | 152 |

| 6.3 Cache Hit rate (a) and first-access flag set hit rate (b) for the first-access track |     |

| mechanism                                                                                | 154 |

| 6.4 Trace port bandwidth for dedicated first-load track mechanism                        | 157 |

# LIST OF TABLES

| Table                                                                        | Page          |

|------------------------------------------------------------------------------|---------------|

| 4.1 MiBench benchmark characteristics                                        | 49            |

| 4.2 Move-to-Front transformation effect on program streams in MiBench        | 52            |

| 4.3 Trace bandwidth for DMTF(128,X), X= 4-16 (a), distribution of the indiv  | vidual trace  |

| components (b)                                                               | 58            |

| 4.4 Compression ratios for xDMTF (x=b,h,e)                                   | 63            |

| 4.5 Trace records encoding                                                   | 70            |

| 4.6 SDC hit rate as functions of its size and organization                   | 76            |

| 4.7 LSP hit rates (a), and LSP trace port bandwidth (b), for the bSDC-LSP sc | heme 77       |

| 4.8 Distributions of individual trace components for two trace module config | urations . 79 |

| 4.9 Fraction of the original miss trace component using LVSA                 | 81            |

| 4.10 Trace port bandwidth of the <i>eSDC-LSP</i> scheme                      | 84            |

| 4.11 Trace port bandwidth of the <i>rSDC-LSP</i> scheme                      | 85            |

| 4.12 Trace module branch pred. events and trace records                      | 92            |

| 4.13 Trace port bandwidth for different TMBP organizations                   | 100           |

| 4.14 Trace port bandwidth evaluation: A comparative analysis                 | 103           |

| 5.1 Partial software replay filtering example                                | 112           |

| 5.2 Distribution of load instruction types                                   | 118           |

| 5.3 Data address filtering rates for load instructions                       | 119           |

| 5.4  | Distribution of types of store instructions                                        | 121  |

|------|------------------------------------------------------------------------------------|------|

| 5.5  | Filtering results for store instructions                                           | 121  |

| 5.6  | Filtering results and trace port bandwidth for all memory referencing instructions | 123  |

| 5.7  | Hit rate in a data address history table                                           | 127  |

| 5.8  | Hit rate in a data address cache                                                   | 128  |

| 5.9  | Data address trace record encoding for ADAC compressor                             | 133  |

| 5.10 | Data address trace compression                                                     | 138  |

| 6.1  | Markov 0 <sup>th</sup> order entropy for MiBench tests                             | 144  |

| 6.2  | Compression ratio achieved by measuring Markov $0^{\mathrm{th}}$ order entropy     | 145  |

| 6.3  | Entropy of high-order load value bits.                                             | 146  |

| 6.4  | The fraction of load values that fit in SIZE bits                                  | 148  |

| 6.5  | First-access mechanism operation: L1 cache (a), trace module (b), software debug   | gger |

| (c). |                                                                                    | 153  |

| 6.6  | First-access set hit rate for cache with 64-byte block                             | 155  |

| 6.7  | Trace port bandwidth for first-load track mechanism.                               | 156  |

| 6.8  | Load values compression rate comparison                                            | 160  |

#### **CHAPTER 1**

#### INTRODUCTION

Embedded computing drives important aspects of our life including the modern communications, transportation, medicine and entertainment. The number of embedded processors by far surpasses the number of processors used for desktop and server computing. For example, a 2009 smartphone typically includes several processor cores [1] and a modern luxury car may have over 70 different processors and microcontrollers [2]. With emergence of ubiquitous computing and wireless sensor networks, we expect further diversification of embedded processors and their applications.

Current technology and economic trends pose unique challenges to the design and the operation of embedded computer systems. Semiconductor technology continues to provide cheaper, smaller, and faster transistors with each new technology generation, and we can integrate more and more transistors on a single chip. However, more aggressive technologies suffer from lower component reliability. Next, increased sophistication of hardware blocks and an increased level of integration limit the observability of internal signals. In result, the time spent in post-silicon debug and verification has grown steadily

as we move from one technology generation to the next [3]. On the other side, software designer's challenges are also on the rise: increased hardware complexity enables more sophisticated applications. The software stack includes many layers, from hardware bring-up, low-level software, OS/RTOS porting, application developing, system integration and performance tuning & optimization, production tests, in-field maintenance, and failure analysis. Growing software complexity often leads to project failures or lost revenue if very tight time-to-market goals are not met. According to a study published by the National Institutes of Standards, software developers typically spend 50%-70% of their development time in program debugging [4]. This time is likely to continue growing with a shift from single- to multi-threaded applications -- developing parallel programs is known to be a more challenging task than developing sequential programs. Hence, debugging and testing becomes one of the most critical steps in the design and operation of modern embedded computer systems.

## 1.1 Software Debugging Challenges

Ideally, system designers and software developers would like to be able to answer the simple question "What is my system doing?" at any point in the design and test cycle. However, achieving complete visibility of all signals in real time in modern embedded platforms is not feasible due to limited I/O bandwidth and high internal complexity.

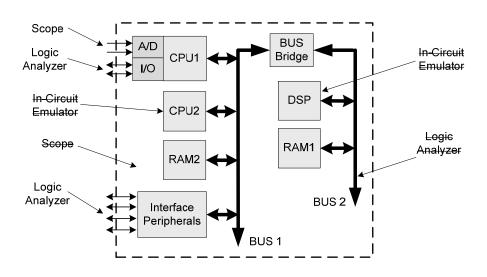

Modern embedded computer systems are built as Systems-On-a-Chip (SOCs) as illustrated in Figure 1.1. SOCs now replace traditional designs that consist of multiple integrated circuits connected on a printed circuit board (PCB). This transition from systems-on-a-board to systems-on-a-chip prevents system designers from observing and controlling internal signals. One approach to addressing this problem is the development

of a dedicated In-Circuit-Emulator (ICE) with additional support for debugging. However, this approach is cost-prohibitive. Furthermore, the ICE's physical characteristics such as chip floorplan, pin layout, and timing characteristics, differ from the targeted SoC. An alternative approach is to incorporate a trace module on the chip—a dedicated hardware resource solely devoted to debugging. The trace module captures, buffers, and sends out a hardware trace—a recorded sequence of events related to program execution, including program execution trace, data trace, and interconnect signals.

Figure 1.1 System-on-Chip Observability

(Strikethroughs represent a change in observability when the identical system is built on a printed circuit board)

Debugging and testing of embedded processors is traditionally done through a JTAG port that supports two basic functions: stopping the processor at any instruction or data access and examining the system state or changing it from outside. The problem with this approach is that it is obtrusive – the order of events during debugging may

deviate from the order of events during "native" program execution when no interference from debugging operations is present. These deviations can cause the original problem to disappear in the debug run. For example, debugging operations may interfere with program execution in such a way that the data races we are trying to locate disappear. Moreover, stepping through the program is time-consuming for programmers and is simply not an option for debugging real-time embedded systems. For example, setting a breakpoint may be impossible or harmful in real-time systems such as a hard drive or a vehicle engine controller. A number of even more challenging issues arise in multi-core systems. They may have multiple clock and power domains, and we must be able to support debugging of each core, regardless of what the other cores are doing. Debugging through a JTAG port is not well suited to meet these challenges.

### 1.2 The Case for Hardware Tracing

Recognizing debugging challenges and issues, many vendors have developed modules with tracing capabilities and integrated them into their embedded platforms, e.g., ARM's Embedded Trace Macrocell [5], MIPS's PDTrace [6] and OCDS from Infineon [7] with a corresponding trace module from Freescale [8]. The IEEE's Industry Standard and Technology Organization has proposed a standard for a global embedded processor debug interface (Nexus 5001) [9]. The trace and debug infrastructure on a chip typically includes logic that captures address, data, and control signals, logic to filter and compress the trace information, buffers to store the traces, and logic that emits the content of the trace buffer through a trace port to an external trace unit or host machine.

Beside resolving debugging challenges and issues in single-core system, tracing is essential in debugging of multi-core systems; various interdependencies and interactions

cannot be observed with the simple snapshot of the system state, but continual tracing is needed in order to find bugs and other unwanted situations.

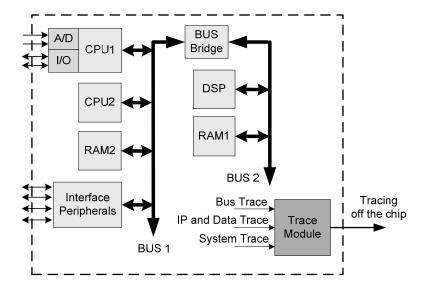

Hardware traces can be classified into three categories depending on the type of information they contain: program (or instruction) traces, data traces (from the memory bus) and system traces (various signals of interest in debugging the implemented hardware or observing the inter-cores dependencies and so on). Figure 1.2 illustrates how the tracing helps us to regain the observably into the system-on chip-behavior; real-time traces from different subsystems can be analyzed offline in order to debug and develop the system and compensate for the lack of observability through logic-scopes.

In this dissertation we focus on program traces which consist of instruction address (program execution) traces, data address traces (addresses of memory referencing instructions) and data value traces (data brought to the CPU using load instructions). These traces are widely used for both hardware and software debugging as well as for program optimization and tuning. While data value traces are sufficient to replay the program offline and analyze its behavior, this type of tracing is often not favored due to its high bandwidth requirements. On contrary, program execution traces have much lower bandwidth requirements while allowing for simple debugging tasks which are sufficient for many testing, debugging and verification purposes.

Tracing requires huge amount of data to be sent out of a chip. For example, a processor running at 1GHz produces gigabytes of trace information for just one second of execution time. Thus, the tracing process must rely on very large on-chip buffers to store the traces of large program segments and/or on relatively wide trace ports that can transfer a large amount of trace data in real-time.

Figure 1.2 Observability of SoC operation using different types of traces

### 1.3 The Case for Trace Compression

Many existing trace modules employ program trace compression and buffering to achieve a bandwidth of about one bit/instruction/CPU on the trace port at the cost of roughly 7,000 gates (for instruction addresses only) [10]. These modules often use very rudimentary compression, such as differential encoding of consecutive instruction and data addresses. However, they still rely on large on-chip buffers that can capture the program trace in real-time for a relatively short program segment and wide trace ports to read out trace information. If we want to capture program traces of larger program segments, we will need larger trace buffers and/or wider trace ports. However, large trace buffers and wide trace ports significantly increase the system complexity and cost. Moreover, they do not scale well, which is a significant problem in the era of multi-core chips, especially considering the rising need for data tracing, which has much larger bandwidth requirements than the program execution traces. For example, the number of

package pins does not increase linearly with the increase of processor speed, or the number of transistors on the chip, as we move from one generation to the next-one.

In this dissertation we argue that tracing can be significantly improved and the debugging costs decreased by using cost-effective hardware structures that compress program traces. The existing trace modules cannot guarantee unobtrusive tracing, rather they strive to provide minimally obtrusive program tracing often providing incomplete traces. However, this limits applicability of the trace modules in debugging real-time embedded systems where interference from debugging operations often cannot be tolerated. The proposed trace compression algorithms and hardware structures are designed to reduce the cost of debugging infrastructure through reducing requirements for large on-chip trace buffers and wide trace ports. In addition, the proposed trace compressors allow for unobtrusive tracing in real-time.

#### 1.4 Contributions

In this dissertation we introduce a number of cost-effective hardware-based and real-time trace compression techniques. We characterize program and data traces of embedded processors that run typical benchmark programs. Based on these characteristics we develop several novel algorithms and trace compression structures that can be used in trace modules of future embedded systems. We explore the design space including trace port bandwidth requirements and implementation complexity and find the optimal design strategies that guarantee unobtrusive tracing in real-time at minimal hardware cost. More specifically, our contributions are as follows.

• We have performed characterization of program execution traces in order to draw conclusions about the best approach for compression of these types of traces.

- We have developed a Double Move-To-Front method for compression of program execution traces.

- We have developed a Stream Cache and Last Stream Predictor method for compression of program execution traces.

- We have developed a Branch Predictor based method for compression of program execution traces.

- We have developed a cost-effective filtering technique for reducing the size of data address traces. The technique relies on reuse of register values to re-generate data addresses in a software debugger.

- We have developed a technique for compression of high order data address bits.

The compression of higher-order bits requires a simple compressor while the compressed traces have low variation in required bandwidth, eliminating the possibility of dropping traces when the available bandwidth is saturated.

- We have characterized the behavior of data values in typical embedded systems applications to gain insight into the compressibility of these types of traces.

- We modified and improved an existing scheme that relies on reusing data values already residing in the processor's cache to re-generate register file values during the program execution in a software debugger.

#### 1.5 Outline

The remainder of this dissertation is organized as follows. In Chapter 2 we discuss the existing approaches and standards for software debugging and tracing in embedded systems. In Chapter 3 we survey general-purpose compression algorithms as well as a number of software-based and hardware-based trace-specific compression

algorithms. In Chapter 4 we describe the proposed mechanism for capturing and compression of program execution traces. We introduce three methods for compression of program execution traces, namely, (a) Double Move-To-Front (b) Stream Descriptor Cache and Last Value Predictor, and (c) Branch Predictor Method. For each method we describe algorithms and compressor structures and perform a detailed design space exploration including trace port bandwidth and design complexity. In Chapter 5 we introduce and explore the effectiveness of two methods for capturing and compressing data address traces, namely, (a) Data Address Trace Filtering through a partial replay of the register file, and (b) Data Address Trace Compression through exploiting low variability of higher address bits. In Chapter 6 we analyze typical load value traces and explore their amiability to compression. We propose several low-complexity approaches to the compression of load value traces and explore their effectiveness. Finally, in Chapter 7 we give concluding remarks.

#### **CHAPTER 2**

### PROGRAM TRACING: BACKGROUND

Program traces encompass recorded sequences of instruction addresses, data addresses, and data values captured during program execution. Program execution or instruction traces are instrumental for software debugging and are also used in profiling for tuning and optimization. However, some software bugs require a complete recreation of memory values. In such cases collection of data address and data value traces is needed.

In Section 2.1 we discuss types of program tracing depending on how traces are collected: software traces (Section 2.1.1) and hardware traces (Section 2.1.2). In Section 2.2 we focus on hardware supported tracing and debug infrastructure needed to support it because it is crucial in debugging embedded systems. Section 2.3 describes several representative examples of commercial trace modules.

10

### 2.1 Types of Tracing

#### 2.1.1 Software Tracing

The most common form of program traces are software traces. Software traces are traditionally created using a trace collector process that runs on the same platform as the traced program. Exception handlers with different granularity (e.g., single-step, step-on-branch) are typically used to capture relevant trace data. The traces are then stored to dedicated trace buffers in system memory. A separate process is responsible for emptying the buffers to an external storage (e.g., hard disk) using available communication channels. A software debugger then reads and analyzes the collected trace. Software tracing has a relatively low implementation cost and offers flexibility in selecting the type of events that are captured during tracing. The main drawback is its obtrusiveness – the trace collector and trace transfer processes consume the CPU time, system memory, and communication channel bandwidth. Thus, software tracing often slows down the program execution by an order of magnitude or more.

A number of software tools for trace collection and analysis have been developed. The best known tools are Shade [11] for instrumentation of SPARC and MIPS architectures; Performance Inspector [12] for x86, x86\_64 and PowerPC64 architectures; and PIN [13, 14] for x86 and ARM architectures. Microsoft has developed a tool for instruction level tracing [15] that also includes a compressor to reduce the trace storage requirements. Here we will briefly discuss the PIN tool.

The PIN tool [13] performs run-time binary instrumentation of Linux and Windows applications through a just-in-time compiler (JIT). PIN starts by intercepting the execution of the first instruction of the executable and generating ("compiling") new

code for the straight-line code sequence starting at the current instruction. It then transfers control to the generated sequence. The generated code sequence is almost identical to the original one, but PIN ensures that it regains control when a branch exits the sequence. After regaining control, PIN generates more code for the branch target and continues execution. Every time the JIT compiler fetches a code segment, a PIN analysis tool (called *Pintool*) has the opportunity to instrument it before it is translated for execution.

PIN implements different optimizations to reduce the number of handshaking operations between the JIT and actual program executable, resulting in reduced tracing overhead. For example, a branch predictor for indirect branches in a JIT compiler allows for less frequent switching to the original code and obtaining the target from there [14]. In spite of these optimizations it imposes a significant slowdown (4 to 12 times just for a simple counting of the number of executed instructions). This slowdown is acceptable for tracing of different general-purpose applications but is not feasible for tracing of real-time embedded systems.

#### 2.1.2 Hardware Tracing

Hardware program traces are collected using dedicated on-chip logic that can capture and store address, data, and control signals. The implementation cost of debug infrastructure for hardware tracing varies depending on trace types that are being collected and the level of obtrusiveness. With obtrusive hardware tracing, on-chip resources are used to perform tracing, compression and qualification of traces, but ultimately, the traces are transferred to system memory using system buses (thus interfering with system operation). With minimally obtrusive or completely unobtrusive

tracing, dedicated on-chip buffers are used to store traces and a separate trace port is used to transfer the collected traces off-chip.

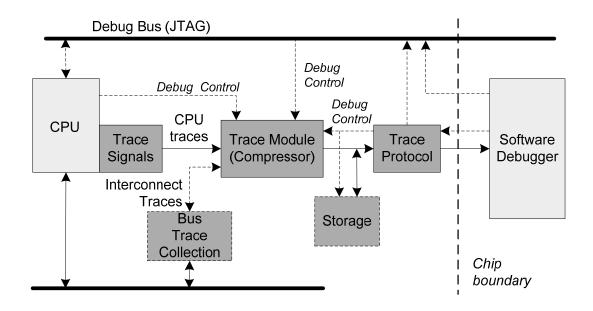

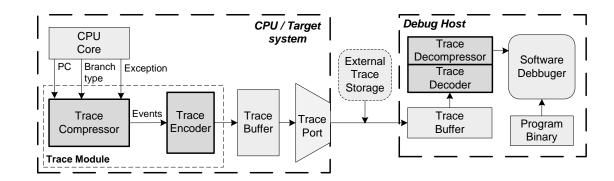

Figure 2.1 gives a system view of a typical on-chip debug infrastructure for unobtrusive hardware tracing. A target processor provides necessary internal signals to the trace module (*Trace Signals* block). The trace module then selects what signals are of interest in the current trace cycle based on debug control and configuration commands received from the software debugger, it starts and stops tracing based on specified external or internal triggers. The trace module optionally performs compression of traces. Finally, traces are output through a trace port to the external trace storage memory, using a trace communication protocol (*Trace Protocol* block). The trace protocol block is used not only for tracing data off the chip, but it also serves as an access point to the on-chip trace related resources from the software debugger side.

Figure 2.1 System view of the hardware support for unobtrusive program tracing

The trace module is controlled by *Debug Control* signals. *Debug Control* signals can come from the trace protocol subsystem if the protocol implements control features besides tracing the data only. *Debug Control* signals can also come from the CPU side. For example, software interrupt routines can be used to setup the trace module operation. The control signals can come from the system level access protocol, JTAG or *Debug Bus* as shown in Figure 2.1, which allows for more flexible control of the trace module operation (the unified system level debug bus accepts control signals from different processors on the chip or from the software debugger). When reading out already stored traces, the same set of *Debug Control* signals instruments the storage memory to output traces out of the chip.

A *Bus Trace Collection* block serves as an additional source of traces for the trace module. For example, in a multi-core system, traces collected directly from the shared bus give better insight into inter-processor dependencies and allow for better correlation of different processors' execution.

## 2.2 Hardware Supported Unobtrusive Tracing

In this section we give more details on the debug infrastructure that supports minimally obtrusive or unobtrusive hardware tracing as illustrated in Figure 2.1.

Section 2.2.1 gives examples of the existing implementations of the *Trace Signals* block. Section 2.2.2 discusses typical operations of trace modules. Section 2.2.3 discusses protocols used to access trace and debug resources on the chip from the software debugger side, most notably the one specified by the IEEE-ISTO 5001 (Nexus) standard.

#### 2.2.1 CPU Trace Signals

A processor's trace signals reflect the processor's internal state. They typically include signals that carry information about the currently executing instruction (e.g., instruction word and address) and values on the memory buses (data addresses and data values). In addition, various pipeline and system state information may be available.

For example, the Tensilica LX2 processor family implements a configurable trace port with different number of trace signals [16]. The simplest processor trace port is 72-bit wide and includes a 32-bit program counter, 8-bit debug status field, and a 32-bit debug data field. The debug status field contains information about the validity of the current instruction and its type and size. Together with the debug data field, various events can be encoded, for example, causes of pipeline bubbles (e.g., read-after-write dependency, structural hazard, I-cache or D-cache miss), pipeline dependency information, and stall information. Next, the debug status and data fields can signal whether an instruction is not executed using the CPU but from the on-chip debugger hardware (instrumented from software). If the data tracing option is enabled, a processor's port width ranges from 140 to 400 bits. Additional bits include the load/store units address, data values, and status signals. Load/store data field size depends on the memory bus width; Load/store status specifies the type of a memory or cache access and the size of the memory referencing request. If the CPU implements two load/store units, the load/store trace signals exist for each unit.

Similarly to the Tensilica's processor trace port, the corresponding trace ports for MIPS and Freescale include status signals that inform the trace module about what type of data is presented on the unified trace port. The MIPS trace port [6] supports tracing of

out-of-order load and store instructions by sending out a signal which contains the information of the load's actual position in the load store queue (e.g., received load value corresponds to the N<sup>th</sup> oldest load instruction). In addition to memory addresses and data, the Freescale MPC565 [8] trace port includes the ownership information (which device on the bus issued a memory referencing instruction).

The Xilinx Microblaze processor [17] implements a trace port with approximately 200 signals [18]. In addition to detailed information on instruction traces and data traces from different memory modules, it includes information about the executing process, unmasked interrupt occurrences, pipeline halted information, exception type, information of pipeline advance for each pipeline stage, debug mode operation, etc.

#### 2.2.2 Trace Module Details

Trace modules today offer various features. The most important ones are related to the qualification of traced data. Trace qualification assumes control on what to trace and when to trace (implemented using various triggers). Other features include a certain level of automatic processing of traces to reduce the amount of unnecessary data presented to the user, compression of traces, and overall a tracing mechanism implementation which allows for correlation of traces in a multi-core system (this may also include timestamping of traces).

The minimum set of tracing triggers allows starting and stopping tracing when certain instruction addresses occur. More advanced triggers may come from conditioning other signals coming from the processor. Finally, the most advanced triggers may come from the other processors or components on the chip (this is often referred to as cross-

triggering). The cross-triggering often requires additional considerations on synchronization of traces coming from different processers and their correlation in time.

For example, Tensilica offers TRAX [16], a tracing module which connects to the Tensilica CPU's trace port and outputs the traced data to the embedded trace memory according to Nexus format. Traced data can be read out through the JTAG. The current TRAX version implements instruction tracing only. This indicates the importance of the program execution tracing only, due to its small bandwidth and storage requirements while enabling basic debugging tasks. In addition, TRAX implements cross-triggering for stopping and starting tracing initiated from other cores in the system.

Xilinx offers the MDM and XTRACE debugging tracing modules [17-19]. The XTRACE module encodes and multiplexes signals from the Microblaze trace port into 22 signals, which are output off the chip, or the trace session can be saved to the on-chip trace memory. Internal cross-trigger functionality is used to setup the trace sessions. The MDM module is used to control the XTRACE module. It is accessible through the JTAG port. For basic debugging purposes, MDM can output information through the UART and it also has access to the Microblaze fast main bus fabric (FSL).

Freescale offers READI [8], a trace and debug module which provides real-time tracing capabilities for different Freescale processors. The module implements a Nexus Class 3 interface which allows for instruction and data tracing and also allows the control of various processor registers and on-chip memories from an external software debugger.

The Embedded Trace Macrocell (ETM) module provides debug and trace facilities for ARM processors [5]. They allow information on the processor's state to be

captured both before and after a specific event, unobtrusive to the processor execution. The ETM can be configured in software to capture only select trace information and only after a specific sequence of conditions. A trace port and FIFO, both configurable, allow the compressed trace data to be read from the chip by an external trace port analyzer, again unobtrusive to the processor execution. The trace port can be configured from a 1 to 32-bit data bus, with a trace clock independent to the core clock.

The functionality of any of the ETMs can be extended by the addition of an Embedded Trace Buffer (ETB) [20]. The ETB, an on-chip memory, stores the captured traces so that later they can be read out at a reduced clock rate. This can be done through the JTAG port of the device without using expensive trace port pins.

#### 2.2.3 Tracing and Debugging Protocols

The most widely used protocol to access on-chip resources is JTAG. JTAG connects on-chip registers into a scan chain which allows the software debugger to modify their values, which in turn, drive the logic internal signals according to predefined test patterns. Each device within a chip has registers already included into the device's scan chain. In a system-on-a-chip with multiple logic devices all individual scan chains are connected together allowing the software debugger to access any device on the chip. Because of long scan chains and a serialized operation, JTAG is suitable only for run/stop based debugging, where the software debugger halts the processor, or the whole system, and then reads out registers in the scan chain to obtain information about the system state. JTAG has been improved over time to offer more debugging capabilities. The IEEE 1149.7 standard [21] was introduced to improve JTAG debug by implementing a system level bypass which allows for quicker accesses to a selected device using much shorter

scan chains. The IEEE P1687 (IJTAG) standard focuses on standardizing the way an external system communicates with any form of internal design debug and test logic via the JTAG port. IJTAG offers a standard way of connecting, accessing, analyzing, and describing embedded instrumentation hardware. Instrumentation hardware includes not only debug and test logic but any circuitry used for device characterization, monitoring, configuration or functional use. The IJTAG infrastructure resides at the deeper level than the JTAG and is accessible through JTAG. The standard defines access mechanisms to the instruments and also defines their hardware and software description. This way, the actual instrument details are hidden from the user allowing for better portability of instruments across different systems and their use with different testing tools.

MIPI Test & Debug. A Mobile Industry Processor Interface Test and Debug working group adds the high bandwidth unidirectional trace interface to the IEEE P1149.7 interface for use in smart phones and other network devices [22, 23]. The tracing is implemented through a System Trace Module (STM), which collects software and debug data from internal buses, encodes the data and sends it out of the chip through a Parallel Trace Interface (PTI). The PTI is an external port of configurable width. A protocol, System Trace Protocol (STP) is used for encoding trace information. MIPI aims to offer a single debug and trace port for multi-core systems; thus, it allows tracing from up to 256 sources (either OS processes or hardware sources, e.g., different processors), offers automatic timestamping and has a configurable PTI width to conform various tracing requirements.

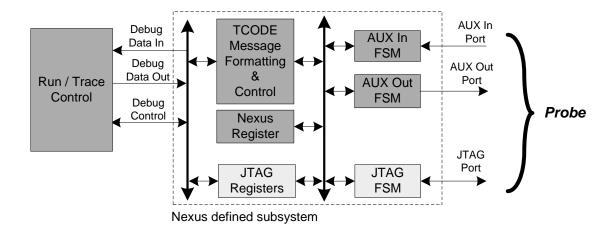

**IEEE 5001 (Nexus).** The Nexus standard defines trace and debug interface, including associated protocols and infrastructure that can serve tracing and controlling of

multiple cores on a chip from the software debugger. Communication between the Nexus internal logic and a software debugger can be achieved through either a JTAG port already included on-chip or through the dedicated and extensible AUX port. An AUX output interface is typically used for tracing data out of chip. The Nexus employs a packet-based messaging tracing scheme with packet headers providing information about data source and destination and type of payload. An AUX input interface allows for bypassing the JTAG control sequences, thus achieving faster response when configuring and calibrating the system. Trace collection mechanisms are not addressed by the Nexus.

Nexus allows vendors to adopt the standard at four levels or classes of operation.

Higher classes include support for more complex debug operations, but in turn require more on-chip resources:

- Class1: Basic Run Control. System implements read/write to user registers and memories, single step debug through break-/watch- points and access to registers and memory locations when the execution is halted.

- Class2: Instruction Trace. In addition to class 1, the system includes support for capturing processor execution trace. Also, it allows for monitoring of process ownership which is useful to correlate simultaneously executed threads in time.

- Class 3: Data Trace. In addition to class 2, the system includes support for monitoring and read/write to data and memory locations, including the I/O reads and writes. This mainly relates to implementation of full tracing capabilities.

- Class 4: Remote processor control and advanced trace. In addition to class 3, the system includes support for direct processor control using memory substitution. Memory substitution allows the processor to execute instructions

from the trace port rather than from the memory. Memory substitution is implemented using address remapping for the I/O space (where the trace port is located) and for the memory (where the original executing program resides). An advanced trace includes tracing of parameters that are not only used to determine program execution but also performance parameters and trace of interconnect signals.

The Nexus packet-based messaging tracing scheme includes different types of messages which follow different implementation classes. There are five main types of messages:

- **Status**. Indicate status information messages from the target.

- General register read/write. Memory mapped reads and writes between software tools and Nexus registers. These messages can be used for run control and configuration of watchpoint/breakpoint operations.

- **Program Trace**. Trace of instruction addresses reduced to trace of branches only (or other program discontinuities).

- **Data Trace**. Trace of data addresses and values. Nexus also supports data acquisition instructions for streaming export of larger amounts of system information (data from an on-chip trace buffer).

- **Memory Access.** Non-intrusive access to internal memory blocks.

Figure 2.2 shows the system level organization of the Nexus infrastructure. It includes various FSM's to access internal registers, registers to control the Nexus operation and the TCODE formatting logic, which performs type-based packaging of trace messages coming from the underlying system using TCODE header.

Figure 2.2 Nexus system level organization

## 2.3 Hardware Trace Infrastructure Examples

In this section we focus on infrastructures that allow for collection of traces inside of a chip and transferring the traces out of the chip. The examples do not necessarily follow the unobtrusive tracing system description from Figure 2.1, but they describe different important intricacies of trace collection and storage in real systems. For example, the OCP-IP Debug in Section 2.3.1 focuses on collection of traces from the main system bus in a multi-core system. The BugNet system in Section 2.3.2 is an obtrusive mechanism which explains different mechanisms when tracing the shared memory and presents some solutions to reduce the size of trace information carried out. Finally, Section 2.3.3 describes the CoreSight infrastructure, a complete unobtrusive system for real-time tracing of all cores in a multi-core environment.

#### 2.3.1 OCP-IP Debug

Open Core Protocol (OCP) is a widely used standard IP core interface [24, 25].

OCP facilitates an IP cores plug-and- play approach by decoupling the cores from other

parts of the chip using a clearly specified core interface protocol. In an OCP system, any proprietary component (e.g., processors, memory modules, and I/O devices) can become OCP compliant by using a wrapper which implements the OCP interface. The wrapper works as a socket, allowing any component to be easily attached and detached to/from an existing port on the OCP interconnect. The socket-based approach also speeds up the verification and optimization of a design.

Part of the OCP standard related to the debug has been developed by the OCP Debug Working Group [26]. This group aims to provide a socket based debug standard for OCP compliant SoC. OCP debug efforts focus on defining the set of debug signals, at the OCP fabric level, which can be used by the external software tools for debugging, testing and other verification purposes. The OCP debug socket is attached to the OCP bus and thus, resides at the deepest level of the debugging infrastructure, and the standard does not addresses how the debug data is traced out of the system (MIPI, Nexus or other protocols can be used for that purpose). The OCP debug socket actual implementation can be adapted to different debugging needs: software centric debugging requires basic run control for cores and program and data tracing. Hardware centric debugging exposes hardware logic signals used for hardware verification purposes. System centric debugging allows for observation of interactions of different components on the chip, such as comparative debugging of any two cores on the chip and operates independently of implemented hardware in order to capture pre-reset and post-crash events and to perform. A multi-core system debug greatly benefits from using the OCP bus and an OCP debug socket. A debug socket, attached to the OCP fabric, has predefined functionalities, such as monitoring of all transactions and responses on the bus in a cycleaccurate manner and it also implements automatic trace qualification and performance analysis. Various levels of support for debug are defined through basic and extended debug signals:

#### **Basic:**

- Debug and run control for cores (run/stop/halt, watch/break- points...) as seen in JTAG only debug solutions.

- Cross-triggering between multiple cores and events to allow global and distributed event recognition across the multi-core system.

- Synchronized run control supports clock synchronized program execution of two cores that run asynchronously in the normal case, allowing for time alignment of their instruction streams in order to study interdependencies.

- Basic bus traffic observation through system trace with control of trace start/stop using triggers. Tracing includes filtering based on OCP operations (e.g., Initiator, thread, address range, DMA).

#### **Extended:**

- Performance Counters (single and multi-core enable observation of selected parameters through summary only, which reduces the output bandwidth.

- Time-stamping allows for correlation of events in a distributed system or events coming from asynchronous parts of system.

- Power Management Monitoring includes observation of gated clock domains and voltage domains in aware architectures, where a debugging process must be performed across all IPs even those that are disconnected at the time.

Security monitoring requires selective enabling debug of sensitive locations at different times and with different levels of authorization.

### 2.3.2 Hardware/Software (Hybrid) Tracing

Hybrid techniques rely on hardware structures to perform compression and reduction of traces, but ultimately, they require the use of system memory as trace storage. This also has an impact on processor execution due to the sharing of memory resources and on-chip buses. One such technique is BugNet [27] which uses the main memory to store traces.

BugNet specifically addresses inter-core dependencies by attaching a modest hardware to a shared cache coherence protocol. By recording the outcomes of all memory races, a debugger is supplied with sufficient information to correlate different processes in time. BugNet additionally reduces the amount of data coming from this coherence monitor by introducing a hardware algorithm that filters out the memory race outcomes that can be inferred from other races that are already traced [28].

BugNet aims to reduce the amount of traced data needed for a debugger to find the bug by recording only the last one second of program execution before the failure. This is because usually program failure is often due to a bug just a few million instructions away from the failure. To support this, BugNet uses *Checkpoints* – a snapshot of system state – at each second and tracing of the system within last second.

Regular data traces from/to each of the processors are compressed using a simple dictionary based compressor. Additionally, data traces are reduced by logging only the first load into the cache; a load accessing a memory location needs to be logged only if it is the first access to that memory location. The values of other loads can be re-generated

during replay in a software debugger that models caches and memories. To implement this optimization, hardware extensions to L1 and L2 caches are necessary.

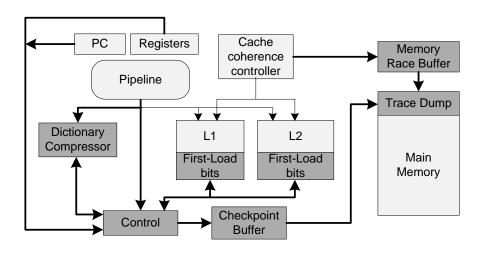

The basic architecture of BugNet is shown in Figure 2.3. Shaded parts of the system are part of BugNet. BugNet attaches a logger to each shared cache to record memory races outcomes and saves the traces to the Memory Race Buffer. The Checkpoint buffer records system state. Both buffers are dumped to main memory on error detection. BugNet limitations are the need for integration with the operational system, detection of only the bugs that lead to the system failure and obtrusive tracing due to usage of main memory.

Figure 2.3 System view of BugNet architecture

# 2.3.3 Hardware Based Debugging Infrastructure

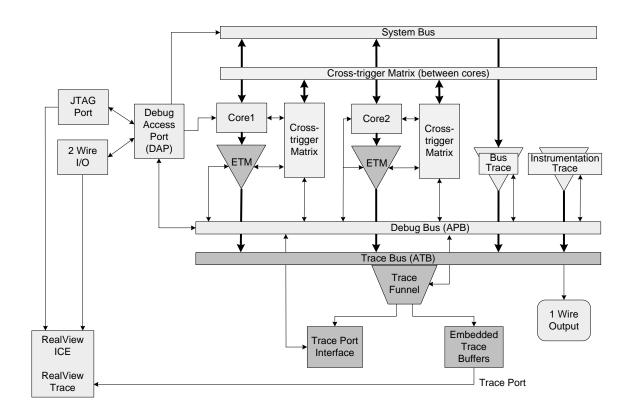

CoreSight [29] provides a SoC architecture which enables a software engineer to fully debug and trace an entire SoC in real-time (Figure 2.4). CoreSight specifically

targets multiprocessor systems where two or more cores have to be halted simultaneously and tracing is required to be cycle accurate. The cross trigger matrix, similar to other triggering mechanisms, enables simultaneous triggering of multiple cores including breakpoints and interrupts. As a result, when a single core is halted (or triggered), all connected cores and peripherals are halted (or triggered), thus providing the user with both control and observability of the system state. To provide the user with correctly correlated traces from different processors, a trace funnel puts data coming from different ETMs in order to the AMBA Trace Bus (ATB). From here, data can be saved to the Embedded Trace Buffers or can be driven directly to the output port. Together with the RealView software analysis tool, ARM aims to provide users with full support for correlations and synchronization of multi-processor executions.

CoreSight hardware is accessible through the Debug access port (DAP), which can be also connected to the standard JTAG port. DAP accesses the AMBA APB bus, which can communicate with all the debugging and tracing devices within the system (ETM, Cross-triggering, directly with the CPUs). CoreSight also includes an Instrumentation block, which is a simple hardware support for software based tracing (e.g., *printf* style debugging, tracing of OS and application events and emitting diagnostic system information).

While offering complete infrastructure for debugging complex systems on a chip, CoreSight does not address the compression of trace data. With a growing number of cores on a single chip, it's a question how CoreSight can scale in a multi-core environment due to the huge bandwidth requirements for tracing.

Figure 2.4 System view of ARM's CoreSight architecture

## **CHAPTER 3**

## TRACE COMPRESSION ALGORITHMS

Trace compression algorithms are designed to exploit redundancies found in program traces. Many of these redundancies can be extracted with general purpose compressors too, but trace-specific compressors can achieve similar or better compression ratios with less compute and storage resources. Hardware implementation of either general purpose or trace specific compressors is a very challenging task. To achieve high compression ratios, the compressors need large buffers, but they tend to be costly. Efficient compression mechanisms with modest hardware resources exploit unique features of program traces. For example, including architectural support for tracing in a processor (e.g., caches, execution units, information on program execution) and instruction set simulator in a software debugger enables significant reduction in the number of required trace records.

The operation and principles behind the most widely used general-purpose software compression applications are described in Section 3.1. Section 3.2 describes specialized techniques and approaches for compression of program traces. In Section 3.3

we discuss hardware implementations of various trace compression techniques and describe several existing compression techniques which can be implemented in hardware, including those that rely on processor architectural state.

# 3.1 General-Purpose Compression Algorithms

In this section we briefly describe the most widely used software compression applications, *gzip*, *bzip2* and *Sequitur*. They are based on distinctly different approaches to the compression of general data sets. *gzip* finds repeating patterns within a data set and replaces them with identifiers which are then efficiently encoded [30]. *bzip2* is based on Burrow-Wheeler transformation [31], and it reorganizes data before compression to reduce the entropy within the individual data sets. Both mechanisms also use different encoding techniques (Huffman coding [32, 33], arithmetic coding [34]) to produce a more compact description of input data set values. We also describe the operation of *Sequitur*, a relatively new mechanism with a novel approach to compression which builds hierarchies of patterns.

## 3.1.1 gzip

gzip is based on a variant of the *lz77* pattern match mechanism [30]. The *lz77* algorithm tries to find repeated patterns in the data set by comparing the incoming, yet to be processed, data with already processed data. Whenever a pattern match occurs, the repeating pattern is replaced with an identifier consisting of two values: *distance*, which indentifies the start position where the previous occurrence of the same pattern starts, and *length*, which indentifies the length of repeated pattern. To reduce the size of (*distance*, *length*) pairs, *gzip* uses two Huffman trees separately for *distance* and *length* in order to

encode more frequent values with less bits. To improve efficiency, adaptive Huffman coding is used, where a new Huffman tree is built for each new block of data. A new block starts when the internal logic determines that the current Huffman tree is no longer the optimal one.

The *gzip* is important in this dissertation as the pattern repetitions are common within instruction and data addresses and a relatively simple pattern matching algorithm can be employed in hardware to compress the traces.

### 3.1.2 bzip2

bzip2 is a complex compression algorithm which uses different concepts from data encoding and the compression field. In its core, bzip2 implements a reversible block-sort algorithm, or Burrow-Wheeler transformation [31]. The transformation does not compress the data but re-organizes it in such a way that it reduces the entropy of data in each separately processed block. For example, if the frequency of the different and most frequent data values, A and B, is approximately the same in one data set, the data set can be reorganized so that A values appear mostly in one part of the program (block 1) while B values appear mostly in other part of the program (block 2). This leads to lower entropy within the data set, when compressing block 1 and block 2 separately. However, an increased compression ratio must be high enough to compensate for the additional storage required to record the information about the reverse transformation. bzip2 uses Move-to-Front (MTF) encoding in the second stage. MTF is a frequency based table, where recent and most frequent data are in the front of the table. MTF does not reduce the size of the input block, but adds additional reordering of data to decrease the entropy even more. Huffman coding is the final stage in the bzip2 algorithm. A

complex scheme implements multiple Huffman tables and dynamically decides on the most optimal one for currently processed data.

bzip is less amiable to hardware implementations because it relies on frequent memory operations to reorganize data and it also works with extremely large data sets (up to 900 KB). However, certain concepts, such as MTF, are used in this dissertation.

# 3.1.3 Sequitur

Sequitur [35] replaces two repeating symbols with a new one. For example, repeating symbols a followed by b can be replaced by a new symbol A. Further on, if the A is followed by symbol c repeatedly, the Ac pattern is replaced by, e.g., symbol D. In this way a hierarchy of patterns is captured into a smaller number of symbols. Sequitur has unique feature in that it preserves the context of original data; an original symbol or a pattern is easily found and reconstructed (e.g., symbol D from the compressed file is simply converted into a, b, c using the grammar file built during execution). Sequitur is highly unsuitable for hardware implementation as the algorithm saves the context information (grammar) for each new symbol built during the execution. Thus, the memory requirements can increase linearly with the processed trace and are in fact unbounded.

# 3.2 Specialized Algorithms for Instruction and Data Trace Compression

Various mechanisms exist which try to identify and exploit redundancies typical for instruction and data traces. Several approaches are described here. Many of them use one of the compression principles exploited by general purpose compressors and just adapts them to the expected behavior of data or instruction traces. Others exploit the

correlation between data addresses (or values) with the instruction address in order to achieve greater compression of data traces.

In this dissertation, the most important compressors are those built from value predictors. Value predictors are used in a processor pipeline to improve latencies of memory operations by predicting data addresses and load values of fetched, and not yet processed load instruction.

## 3.2.1 Instruction Address Trace Compression

Instruction address compression techniques work by compressing only the information from control-flow changing instructions. This is possible as a simple decompressor, which has the basic information from program binary, can easily reconstruct all other instructions.

The simplest approach to compression is to replace an address with the offset from the last address, which is employed in Nexus [9]. This approach exploits the locality of instruction addresses, where consecutive branching often changes just lower instruction address bits, and thus, upper ones do not have to be traced.

Several techniques exist which try to replace the execution sequence with its identifier. For example, Whole Program Path (WPP) [36] instruments a program to produce a trace of acyclic paths. Then, a modification of the Sequitur algorithm is used to compress acyclic paths, represented by unique identifiers. WPP successfully finds the most frequent program paths, which is very useful for various types of analysis. However, since the WPP is not a single-pass mechanism, as it requires code instrumentation, its implementation in hardware is very limited. An advanced WPP implementation, time stamped WPP [37], enables fast access to the trace produced by a

particular function. The mechanism separately performs WPP on traces belonging to different functions. PDI [38] associates dictionary entries with the most frequent instruction words. N-TUPLE [39] saves a number of control flow change identifiers per dictionary entry. In this way, a whole group of repeated identifiers can be replaced with the pointer to the dictionary entry. N-TUPLE exploits frequent patterns that exist among dynamic basic blocks in common programs.

A more complex approach to compression is through building a control flow graph, which together with information on transitions between graph nodes, describes the control flow changes. One such a technique is QPT [40]. QPT records only information about significant events and only transitions between basic blocks where a program chooses between alternative paths and only those transitions that are not part of a maximum spanning tree of a control flow graph. The actual instruction addresses can be regenerated using the control flow graph.

## 3.2.2 Data Address Compression

The Nexus standard [9] uses the same offset based encoding for both instruction addresses and data addresses. The compression benefits from spatial and temporal locality of memory references where the consecutive memory addresses differ by only a small value. Mache [41] replaces a data address with the offset from the last address of the same type. Types are instruction reference, data read and data write. PDATS [38] adds more complexity by introducing the variable length encoding of the offset field and includes an optional repetition counter.

Data addresses can be compressed by linking them to the program loops. Various mechanisms [42] [43] require two-pass mechanisms where first program loops are

detected either using the control-flow analysis or program instrumentation. In a second pass, many of the data references are easily identified as being always constant per loop or always having the same offset from loop to loop. However, all other data addresses, with so-called chaotic behavior, are not compressed.

A special type of compressors tries to link the data addresses with the instruction block. A technique described in [44] records all possible data offsets and repetitions for a data address which is linked to an instruction block. Also, instruction blocks are compressed by indentifying all instruction blocks' successors and their repetition count. The memory requirements for this mechanism are very high, and the mechanism can be considered as only the first-pass reordering of memory and instruction addresses for an easier compression using a general purpose compressor. Stream Based Compression (SBC) [45] exploits the inherent characteristics of instruction and data address traces. Instruction traces consist of a fairly low number of different streams (streams are dynamic basic blocks described by their descriptor - starting address and the length, in number of instructions). Newly occurred stream descriptors are allocated in a table and the table search is performed upon each new stream occurrence. An index in a table replaces the whole stream descriptor. Data addresses traces have strong spatial/local locality which is exploited through a mechanism aware of frequent constant strides between consecutive memory referencing addresses.

Value predictors for data addresses. Value predictors for data addresses or data address predictors are cache like structures that store recently executed data addresses (last several data addresses per instruction address). Data address predictors are used in the processor's pipeline for data pre-fetching [46] (prediction of future memory

references) and early load address calculation [47] (to enable issuing a load instruction early in the pipeline instead of waiting for the address calculation). Data address predictors can also be used for compression of data addresses. The compression is achieved by replacing a data address with an identifier which points to the cache entry which stores the correctly predicted address.

Data address predictors are usually organized as instruction pointer-indexed (IPindexed) caches or tables, which store different information on data addresses recently issued by the load instruction. For example, last value (or address) predictors [48, 49] store the last several addresses seen by a load instruction (predictors are named LVxwhere x denotes the number of stored addresses). Stride based predictors are frequently used for both load address prediction and hardware pre-fetching due to their modest hardware requirements and the fact that many data addresses appear in strides (both consecutively in program or per instruction). This is particularly true for scientific applications where programs traverse large arrays of data [46, 50]. Context based predictors [51-53] are trying to predict the next data address based on the value of several last addresses. Context based predictors usually employ two caches (tables) where the first one stores the hashed history of the previously seen addresses which is used to access the second cache where the addresses are saved. Hybrid predictors [53, 54] combine last value stride and context predictors and implement a chooser which tries to determine which of the implemented predictors should give the final prediction for a given load.

A special context predictor named correlated predictor [55] tries to predict addresses which are not easily predictable by last value or stride predictors. The

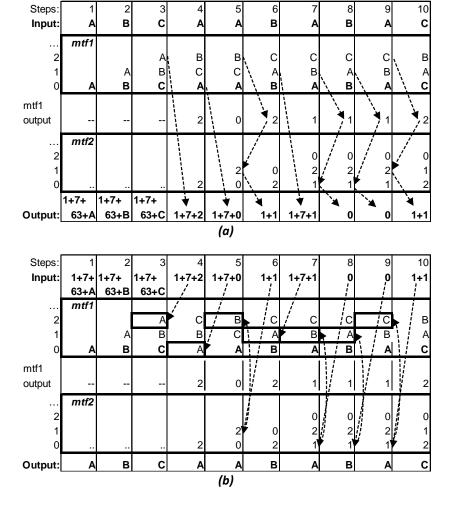

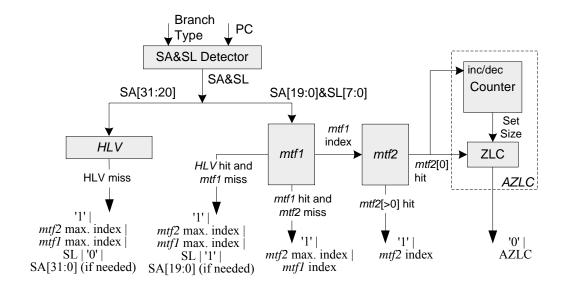

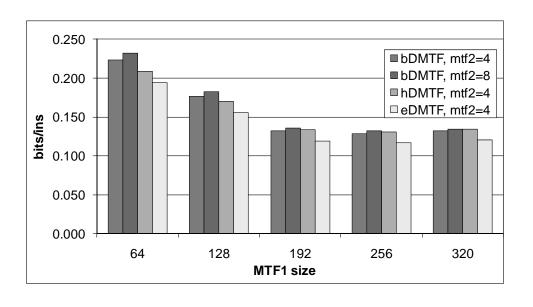

correlated address predictor splits the upper and lower part of each data address. Upper bits are stored in an IP-indexed table (a table of so-called *base* addresses), while the lower bits of several data addresses corresponding to the same *base* address are saved in the second table. A hashed history of data addresses, for each *base* addresses, is used to index into the second table. The lower data address bits change more frequently, and reducing their storage requirements (32 to 8 bits in this case) allows for more information to be added to a cache.