# EXPERIMENTAL EVALUATION OF TECHNIQUES FOR CAPTURING AND COMPRESSING HARDWARE TRACES IN MULTICORES

by

# AMRISH K. TEWAR

#### A THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

HUNTSVILLE, ALABAMA

2015

| In presenting this thesis in partial fulfillr | ment of the requirements for a master's de-  |

|-----------------------------------------------|----------------------------------------------|

| gree from The University of Alabama in I      | Huntsville, I agree that the Library of this |

| University shall make it freely available f   | for inspection. I further agree that permis- |

| sion for extensive copying for scholarly pu   | arposes may be granted by my advisor or, in  |

| his/her absence, by the Chair of the Depa     | rtment or the Dean of the School of Gradu-   |

| ate Studies. It is also understood that due   | e recognition shall be given to me and to    |

| The University of Alabama in Huntsville       | in any scholarly use which may be made of    |

| any material in this thesis.                  |                                              |

|                                               |                                              |

|                                               |                                              |

|                                               |                                              |

| (student signature)                           | (date)                                       |

|                                               |                                              |

# THESIS APPROVAL FORM

Submitted by Amrish K. Tewar in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this thesis. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering.

|     | Committee Chair  |

|-----|------------------|

| (Da | ate)             |

|     |                  |

|     |                  |

|     |                  |

|     |                  |

|     |                  |

|     |                  |

|     | <u>-</u>         |

|     | Department Chair |

|     |                  |

|     | College Dean     |

|     |                  |

|     | Graduate Dean    |

# ABSTRACT

# The School of Graduate Studies The University of Alabama in Huntsville

| Degree Master of Scie   | nce in Engineering          | College/Dept. Engineering/Electrical &      |

|-------------------------|-----------------------------|---------------------------------------------|

|                         |                             | Computer Engineering                        |

| Name of Candidate       | nental Evaluation of        | Techniques for Capturing and Compress-      |

| Modern embed            | ded systems are indi        | spensable in all aspects of modern life.    |

| The increasing comple   | exity of hardware and       | d software stacks and tightening time-to-   |

| market deadlines mak    | xe software developm        | ent and testing the most critical aspects   |

| of system developmen    | t. To help developers       | find software bugs faster, modern em-       |

| bedded systems increa   | asingly rely on on-ch       | ip resources for debugging and tracing.     |

| Unfortunately, captur   | ring and streaming a        | ll hardware events of interest for program  |

| debugging is cost-prol  | nibitive in multicores      | where tens of processor cores work con-     |

| currently at very high  | speeds. This thesis         | focuses on capturing control-flow and data  |

| traces in multicores. I | t introduces two new        | techniques: mcfTRaptor for capturing        |

| control-flow traces an  | d <i>mlvCFiat</i> for captu | ring load data value traces. The effective- |

| ness of the commercia   | l state-of-the-art and      | the proposed techniques are experimen-      |

| tally evaluated by me   | asuring the number          | of bits needed to be streamed off the chip  |

| for both functional an  | d timed traces. The r       | results show that the proposed techniques   |

| are very effective, whi | ile requiring modest        | hardware support.                           |

| Abstract Approval:      | Committee Chair             |                                             |

| 1                       | Department Chair            |                                             |

| (                       | Graduate Dean               |                                             |

This thesis is dedicated to my mother and wife without whose love and support I would not be where I am

#### ACKNOWLEDGMENTS

I am grateful to the Almighty, who has always given me good mentors to achieve big steps throughout my life. This Thesis is one of those big steps which has immensely built me up. On completion of this step, I want to express my gratitude to those who have played an important role, either directly or indirectly.

Foremost, I would like to express my gratitude to my advisor, Dr. Aleksandar Milenković. He is an exceptional and patient teacher, and a great motivator. I have always admired his honest comments regarding my work on each and every problem. His work ethic and continuous counselling has always provided me with inspiration and support. For all his efforts on my behalf, I thank him and wished him continued success in his career.

I would like to thank Dr. Rafael Ubal (Multi2Sim) & Albert Myers (mTrace) for developing the tools which were vital to this research.

I would like to express thanks to Professors Rhonda Gaede and Earl Wells for serving in my thesis committee. I am thankful to all the ECE Department professors who taught me various subjects in Computer Engineering. All the staff members of ECE and COE have helped me in many ways during my time as a Master student.

I would also like to acknowledge several people, on a personal front, who have provided me support and the resources to excel. Foremost, I express my immense gratitude to Mr. S. N. Bhatt, and Mrs. M. S. Bhatt for leading me to the path of engineering. I would like to thank Dr. K. Bhatt, Mrs. J. Rosano, Mr. P. B. Pandya, Mrs. R. H. Bhatt, Mr. H. I. Bhatt, and Mr. S. J. Patel for their support. I would also like to thank Mr. A. M. Tewar, Mrs. V. R. Desai, Mr. M. G. Pandya, Dr. B. B. Patel, Mr. M. P. Gandhi, Mrs. H. C. Desai, Mr. M. Shah, and Mr. K. Thakkar for their guidance and help.

Finally, but most importantly, I would express my gratitude to my family. I want to thank my parents, Harshaben and KiritKumar Tewar, for their love and support. I thank my better half, Ruchi Bhatt, for giving me inspiration for furthering my studies, and for her continuous support.

# TABLE OF CONTENTS

| Content | ts<br>F FIGURES                        | Page |

|---------|----------------------------------------|------|

|         | F TABLES                               |      |

| LIST O. | r TADLES                               | XIII |

| CHAPT   | ER 1                                   | 1    |

| 1.1     | Background and Motivation              | 1    |

| 1.2     | What is this thesis about?             | 4    |

| 1.3     | Main Results                           | 5    |

| 1.4     | Contributions                          | 6    |

| 1.5     | Outline                                | 6    |

| CHAPT   | ER 2                                   | 8    |

| 2.1     | Control Flow Traces                    | 8    |

| 2.2     | Memory Data Traces                     | 11   |

| 2.3     | Tracing in Embedded Multicores         | 13   |

| 2.4     | Related Work                           | 16   |

| CHAPT   | ER 3                                   | 19   |

| 3.1     | mcfTRaptor                             | 19   |

| 3.2     | mlvCFiat                               | 24   |

| CHAPT   | ER 4                                   | 29   |

| 4.1     | Software Trace Generation              | 30   |

| 4.2     | Software to Hardware Trace Translation | 32   |

| 4.2.    | 1 mcfNX_b                              | 33   |

| 4.2.    | 2 mcfTR_b and mcfTR_e                  | 36   |

| 4.2.    | 3 <i>mlvNX_b</i>                       | 38   |

| 4.2.    | 4 mlvCF_b and mlvCF_e                  | 39   |

| 4.3     | Experimental Environment               | 41   |

| 4.3.    | 1 Experimental Setup                   | 41   |

| 4.3.2    | Benchmarks                                           | 42  |

|----------|------------------------------------------------------|-----|

| 4.3.3    | Experiments                                          | 45  |

| 4.3.4    | Variable Encoding                                    | 47  |

| CHAPTER  | 5                                                    | 50  |

| 5.1 Tra  | ace Port Bandwidth for Control-Flow Traces           | 51  |

| 5.1.1    | mcfNX_b                                              | 51  |

| 5.1.2    | mcfTRaptor                                           | 53  |

| 5.2 Tra  | ace Port Bandwidth for Memory Load Data Value Traces | 59  |

| 5.2.1    | $mlvNX\_b$                                           | 59  |

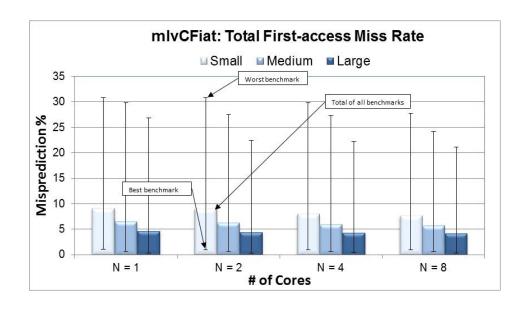

| 5.2.2    | mlvCFiat                                             | 61  |

| CHAPTER  | 6                                                    | 67  |

| 6.1 Sot  | ftware Timed Trace Generation                        | 69  |

| 6.1.1    | Functional Description                               | 69  |

| 6.1.2    | Format of Timed Trace Descriptors                    | 71  |

| 6.1.3    | TmTrace Implementation Details                       | 75  |

| 6.1.4    | Verification Details                                 | 76  |

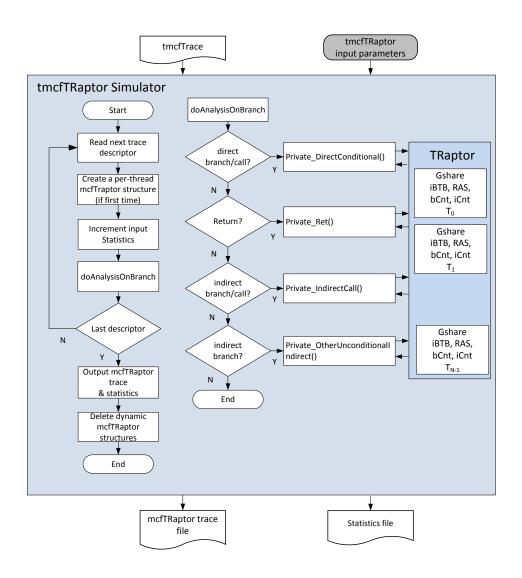

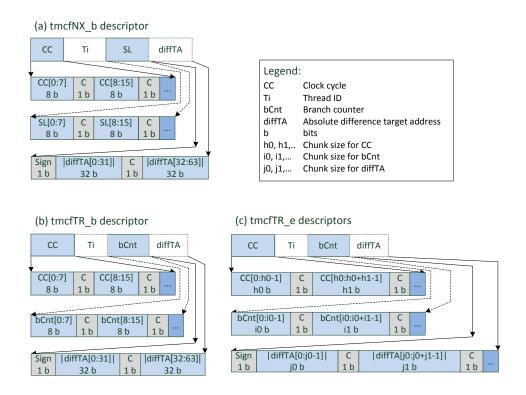

| 6.2 	 tm | cfTRaptor Simulator                                  | 83  |

| 6.2.1    | Functional Description                               | 84  |

| 6.2.2    | Implementation Details                               | 88  |

| 6.2.3    | Verification Details                                 | 90  |

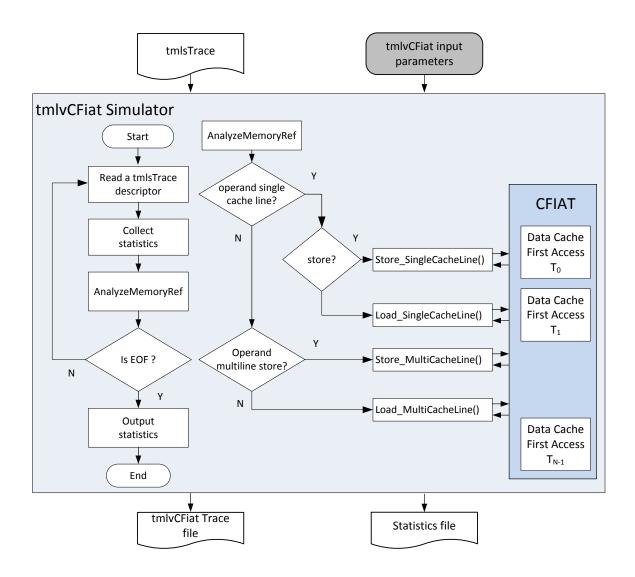

| 6.3 	 tm | lvCFiat Simulator                                    | 94  |

| 6.3.1    | Functional Description                               | 94  |

| 6.3.2    | Implementation Details                               | 96  |

| 6.3.3    | Verification Details                                 | 97  |

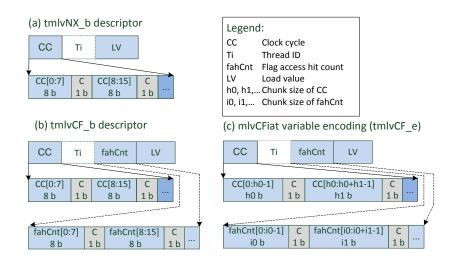

| 6.4 Sof  | ftware to Hardware Trace Translation                 | 101 |

| 6.5 Ex   | perimental Environment                               | 103 |

| 6.5.1    | Experimental Setup                                   | 103 |

| 6.5.2   | Benchmarks                                                 | 104 |

|---------|------------------------------------------------------------|-----|

| 6.5.3   | Experiments                                                | 107 |

| 6.5.4   | Variable Encoding                                          | 109 |

| CHAPTER | 7                                                          | 110 |

| 7.1 Tr  | ace Port Bandwidth for Timed Control-Flow Traces           | 111 |

| 7.1.1   | $tmcfNX\_b$                                                | 111 |

| 7.1.2   | tmcfTRaptor                                                | 113 |

| 7.2 Tr  | ace Port Bandwidth for Timed Memory Load Data Value Traces | 119 |

| 7.2.1   | $tmlvNX\_b$                                                | 119 |

| 7.2.2   | tmlvCFiat                                                  | 121 |

| CHAPTER | 8                                                          | 127 |

| REFEREN | CES                                                        | 130 |

# LIST OF FIGURES

| Figur | e Pa                                                                   | age |

|-------|------------------------------------------------------------------------|-----|

|       | Figure 1.1 Debugging and tracing in embedded multicores: a system view | 3   |

|       | Figure 2.1. Control-flow trace: an example                             | .11 |

|       | Figure 2.2. Memory read trace: an example                              | .12 |

|       | Figure 2.3 Debugging and tracing in multicores: a detailed view        | .15 |

|       | Figure 3.1 A system view of mcfTRaptor                                 | .21 |

|       | Figure 3.2. $mcfTRaptor$ structures for core $i$                       | .21 |

|       | Figure 3.3 $mcfTRaptor$ operation on core $i$                          | .23 |

|       | Figure 3.4 Program replay in software debugger for mcfTRaptor          | .24 |

|       | Figure 3.5 A system view of mlvCFiat                                   | .26 |

|       | Figure 3.6 mlvCFiat structures for core i                              | .26 |

|       | Figure 3.7 $mlvCFiat$ operation on core $i$                            | .27 |

|       | Figure 3.8 mlvCFiat operation in software debugger for core i          | .28 |

|       | Figure 4.1 Experiment flow for determining trace port bandwidth        |     |

|       | requirements using functional traces.                                  | .30 |

|       | Figure 4.2 Functional trace generation using <i>mTrace</i> tool suite  | .31 |

|       | Figure 4.3 Software to hardware trace translation                      | .33 |

|       | Figure 4.4 mcfTrace and mcfNX_b trace descriptors                      | .35 |

|       | Figure 4.5 mcfTRaptor, mcfTR_b, and mcfTR_e trace descriptors          | .38 |

|       | Figure 4.6 mlvTrace and mlvNX_b trace descriptors                      | .39 |

|       | Figure 4.7 mlvTrace, mlvCF_b, and mlvCF_e trace descriptors            | .40 |

|       | Figure 4.8 Block diagram of Intel Xeon E5-2650 v2 processor socket     | .41 |

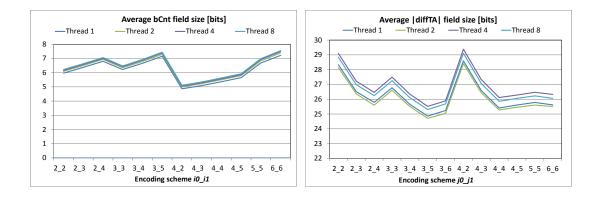

|       | Figure 4.9 CDF of the minimum length for bCnt and  diffTA  fields      | .47 |

| Figure 4.10 Total average bCnt and  diffTA  field sizes as a function of |

|--------------------------------------------------------------------------|

| encoding48                                                               |

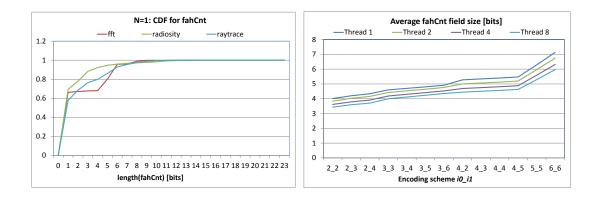

| Figure 4.11 CDF of the minimum length for Ti.fahCnt and the average      |

| Ti.fahCnt for variable encoding                                          |

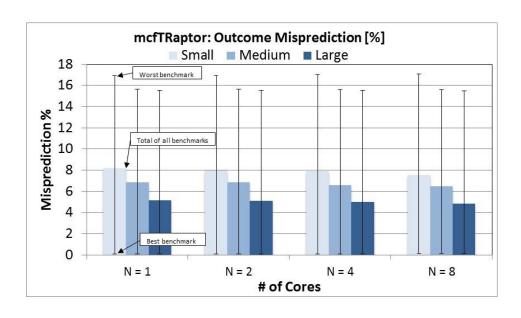

| Figure 5.1 Outcome misprediction rates for Splash2x bechmark54           |

| Figure 5.2 Target address misprediction rates for Splash2x benchmark54   |

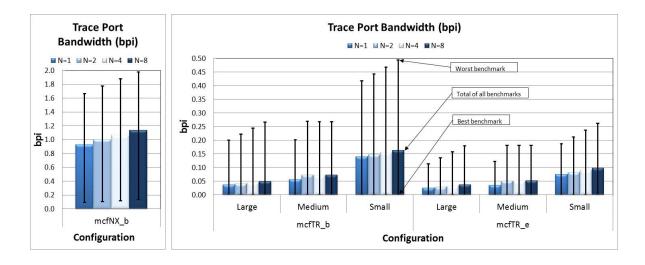

| Figure 5.3 Total trace port bandwidth in bpi for control flow traces56   |

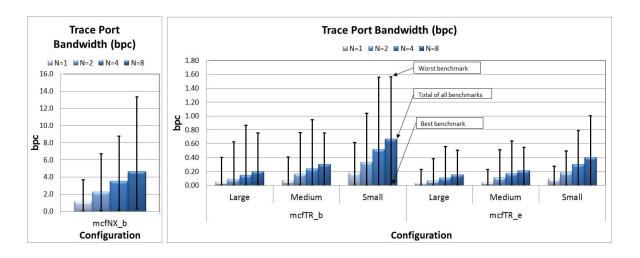

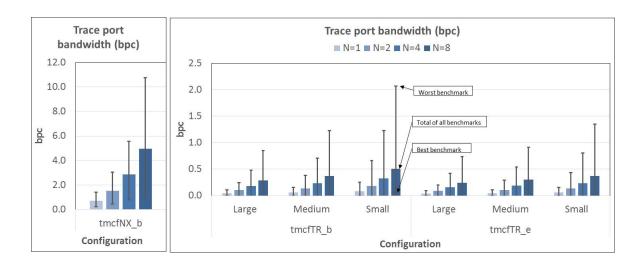

| Figure 5.4 Trace port bandwidth in bpc for control-flow traces59         |

| Figure 5.5 First access miss rate for Splash2x benchmark                 |

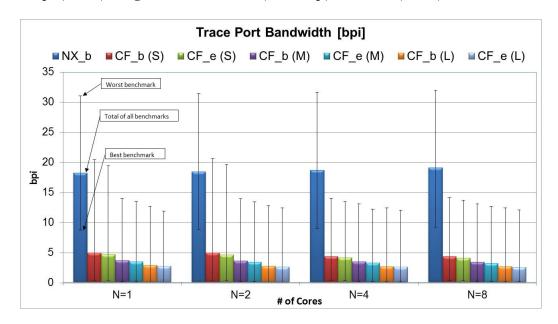

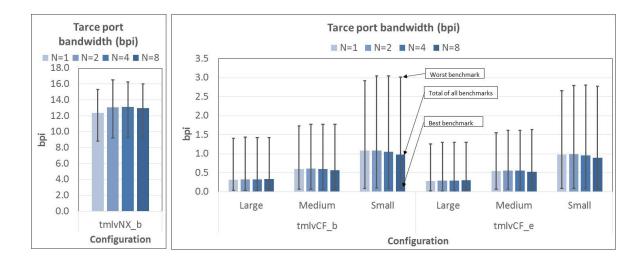

| Figure 5.6 Trace port bandwidth bpi for load data value trace63          |

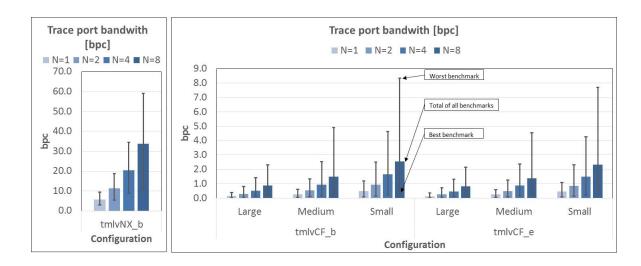

| Figure 5.7 Trace port bandwidth in bpc for load data value trace66       |

| Figure 6.1 Experiment flow for timed traces                              |

| Figure 6.2 Trace descriptor when all committed instructions are traced72 |

| Figure 6.3 Trace descriptor for timed control-flow trace                 |

| Figure 6.4 Trace descriptors generated for memory reads and writes74     |

| Figure 6.5 Capturing timed control flow traces                           |

| Figure 6.6 Capturing timed memory read and write traces                  |

| Figure 6.7 Conditional branches in testControlEnumeration.s              |

| Figure 6.8 Unconditional branches in testControlEnumeration.s79          |

| Figure 6.9 Tracing enabled for a specific code segment                   |

| Figure 6.10 Testing <i>TmTrace</i> load data value traces: an example    |

| Figure 6.11 Testing <i>TmTrace</i> for an extended data type             |

| Figure 6.12 Testing <i>TmTrace</i> for SIMD data types83                 |

| Figure 6.13 tmcfTRaptor trace descriptor formats                         |

| Figure 6.14 tmcfTRantor output files                                     |

| Figure 6.15 <i>tmcfTRaptor</i> simulator organization89                           |

|-----------------------------------------------------------------------------------|

| Figure 6.16 GShare verification example and results91                             |

| .Figure 6.17 Return address stack example                                         |

| Figure 6.18 iBTB test example93                                                   |

| Figure 6.19 <i>tmlvCFiat</i> trace descriptor format95                            |

| Figure 6.20 <i>tmlvCFiat</i> simulator organization97                             |

| Figure 6.21 Testing <i>tmlvCFiat</i> : single cache line access                   |

| Figure 6.22 Testing <i>tmlvCFiat</i> : multi-line cache access                    |

| Figure 6.23 Trace descriptors for $tmcfNX\_b$ , $tmcfTR\_b$ , and $tmcfTR\_e$ 102 |

| Figure 6.24 Trace descriptors for $tmlvNX\_b$ , $tmlvCF\_b$ , and $tmlvCF\_e$ 102 |

| Figure 6.25 Block diagram of a modeled multicore in Mult2Sim104                   |

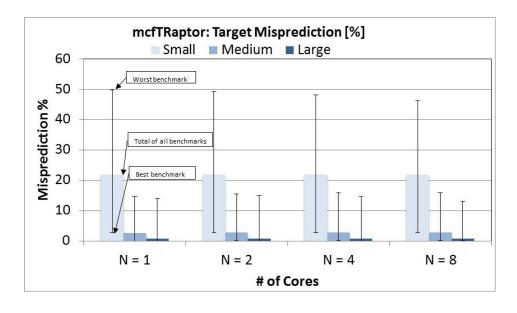

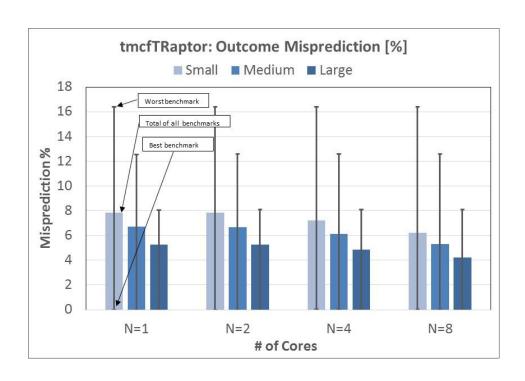

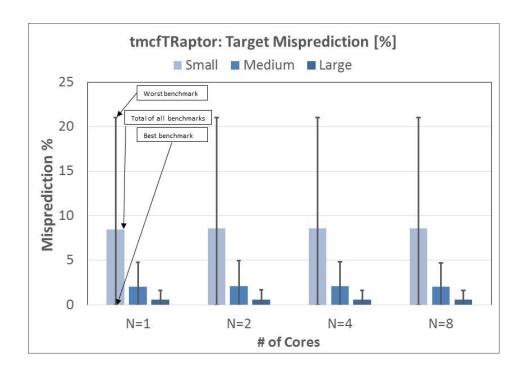

| Figure 7.1 Outcome misprediction rates for Splash2 benchmark114                   |

| Figure 7.2 Target address misprediction rates for Splash2 benchmark114            |

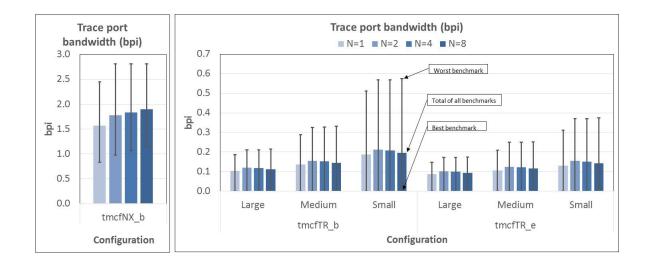

| Figure 7.3 Total trace port bandwidth in bpi for timed control flow traces $116$  |

| Figure 7.4 Trace port bandwidth in bpc for control flow traces                    |

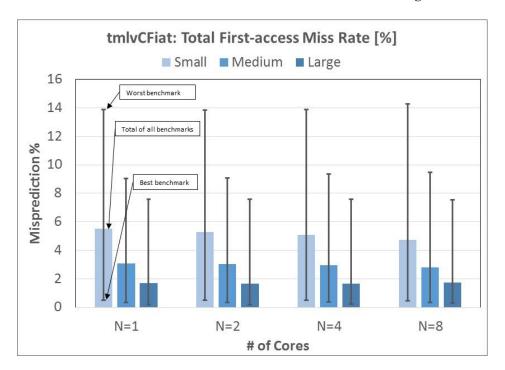

| Figure 7.5 First Access Miss Rate for Splash2 benchmark                           |

| Figure 7.6 Trace port bandwidth bpi for timed load data value trace123            |

| Figure 7.7 Trace port bandwidth in bpc for timed load data value trace126         |

# LIST OF TABLES

| ble Pag                                                                              | ;e |

|--------------------------------------------------------------------------------------|----|

| Table 4.1 mcfTRaptor events and trace descriptor fields                              | 6  |

| Table 4.2 Splash2x benchmark suite control flow characterization4                    | 3  |

| Table 4.3 Splash2x benchmark suite memory read characterization4                     | 4  |

| Table 4.4 Benchmark characterization of memory reads4                                | 5  |

| Table 4.5 Functional trace experiments4                                              | 6  |

| Table 5.1 Trace port bandwidth for $mcfNX\_b$ for Splash2x benchmark5                | 2  |

| Table 5.2 Outcome and target address misprediction rates                             | 3  |

| Table 5.3 Compression ratio for $mcfTR\_b$ relative to $mcfNX\_b$ 5                  | 7  |

| Table 5.4 Compression ratio for $mcfTR\_e$ relative to $mcfNX\_b$ 5                  | 8  |

| Table 5.5 Trace port bandwidth for $mlvNX\_b$ for Splash2x benchmark6                | 1  |

| Table 5.6 TPB for $mlvNX\_b$ , $mlvCF\_b$ , and $mlvCF\_e$ for large configuration 6 | 4  |

| Table 5.7 Compression ratio of $mlvCF\_e$ relative to $mlvNX\_b$ 6                   | 5  |

| Table 6.1 <i>TmTrace</i> custom flags7                                               | 1  |

| Table 6.2 tmcfTRaptor flags8                                                         | 5  |

| Table 6.3 iBTB status and updates for the test example9                              | 4  |

| Table 6.4 tmlvCFiat flags9                                                           | 5  |

| Table 6.5 Splash2 benchmark suite control flow characterization10                    | 5  |

| Table 6.6 Splash2 benchmark suite memory read characterization10                     | 6  |

| Table 6.7 Characterization of memory reads in Splash210                              | 7  |

| Table 6.8 Timed trace experiments10                                                  | 8  |

| Table 6.9 Summary variable encoding parameter for different fields10                 | 9  |

| Table 7.1 Trace port bandwidth for <i>tmcfNX h</i> for Splash2 benchmark 11          | 9  |

| Table 7.2 Total outcome and target address misprediction rates for Splash11    |

|--------------------------------------------------------------------------------|

| Table 7.3 Compression ratio for <i>tmcfTR_b</i> relative to <i>tmcfNX_b</i> 11 |

| Table 7.4 Compression ratio for <i>tmcfTR_e</i> relative to <i>tmcfNX_b</i> 11 |

| Table 7.5 Trace port bandwidth for $tmlvNX\_b$ for Splash2 benchmark12         |

| Table 7.6 Trace port bandwidth for $tmlvNX\_b$ and $tmlvCFiat$                 |

| Table 7.7 Compression ratio of <i>tmlvCF e</i> ralative to <i>tmlvNX b</i>     |

#### CHAPTER 1

# INTRODUCTION

Without efforts you cannot achieve – Do not desire anything free --Rev. Pandurang Shastri Athavale

## 1.1 Background and Motivation

Embedded computer systems are indispensable in modern communications, transportation, manufacturing, medicine, entertainment, and national security. Embedded computer systems are often used as a part of larger physical systems they control or serve by providing computational services. Such systems are often referred to as cyber-physical systems. Faster, cheaper, smaller, more sophisticated, and more power-efficient embedded computer systems spur new applications that require very complex software stacks. The growing software and hardware complexity and tightening time-to-market deadlines make software development and debugging the most critical aspects of embedded system development.

A study by the National Institute of Standard and Technology (NIST, RTI, 2002) [1] found that software developers spend 50 to 75% of their development time debugging programs. Thus, with 800,000 software developers in the U.S. with annual gross salaries of \$120,000, the annual cost of software debugging is \$48 billion. In spite of these efforts, the U.S. still loses approximately \$20-\$60 billion a year due to

software bugs and glitches. The recent shift toward multicore architectures makes software development and debugging even more challenging.

Ideally, software developers would like to have perfect visibility into the system state during program execution. However, achieving complete visibility of all internal signals in real time is not feasible due to limited I/O bandwidth, high internal complexity, and high operating frequencies. To address these challenges, modern embedded processors increasingly include on-chip hardware modules solely devoted to debugging and tracing. These modules encompass logic for stop-control debugging and resources to capture, filter, buffer, and output control-flow and data traces. These traces, coupled with powerful software debuggers, enable a faithful program replay that allows developers to locate and correct software bugs faster.

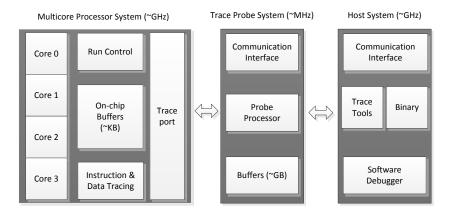

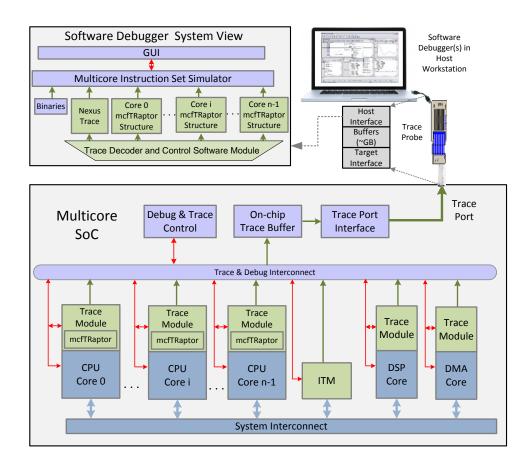

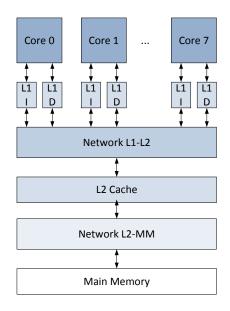

Figure 1.1 shows a typical embedded system-on-a-chip (SoC) with 4 processor cores and its on-chip debugging resources that include run-control logic, logic for capturing program traces, and buffers that serve to temporarily store captured traces before they are streamed out through a trace port to an external trace probe. The external trace probe typically includes large trace buffers on the order of gigabytes and interfaces to the target platform's trace port and to the host workstation. The host workstation runs a software debugger that replays the program execution offline by reading and processing the traces from the external probe and executing the program binary. This way, software developers can faithfully replay the program execution on the target platform and gain insights into behavior of the target system while it is running at full speed.

Figure 1.1 Debugging and tracing in embedded multicores: a system view

The IEEE's Nexus 5001 standard [2] defines functions and interfaces for debugging and tracing in embedded processors for four classes of debugging and tracing operations (Class 1 – Class 4). State-of-the-art trace modules employ filtering and encoding to reduce the number of bits necessary to recreate program execution. Yet, trace port bandwidths are still in the range of 1 to 4 bits per instruction executed per core for control-flow traces [3] and 16 bits per instruction executed per core for data-flow traces [3]. With these trace port bandwidth requirements, a 1 KB onchip trace buffer per processor core may capture control-flow of program segments on the order of 2,000-8,000 instructions or data-flow of program segments of merely 400-800 instructions. Such short program segments are often insufficient for locating software errors in modern systems with more sophisticated software stacks where the distance between a bug's origin and its manifestation may span billions of executed instructions. Increasing the size of the buffers and the number of pins for trace ports is not an attractive alternative to chip manufacturers as it significantly increases the system complexity and cost. This problem is exacerbated in multicore processors where the number of I/O pins dedicated to trace ports cannot keep pace

with the exponential growth of the number of processor cores on a single chip. Yet, debugging and tracing support in multicores is critical because of their increased proliferation in embedded systems and their increased sophistication and complexity.

## 1.2 What is this thesis about?

Developing cost-effective hardware support for debugging and tracing in multicores is of great importance for future embedded systems. On-chip debug and trace infrastructure should be able to unobtrusively capture control-flow and data-flow traces from multiple processor cores at minimal cost (which translates into minimal on-chip trace buffers) and stream them out in real-time through narrow trace ports.

This thesis focuses on capturing and compressing control-flow and load data value hardware traces in multicores. These traces are sufficient to replay programs offline in the software debugger under certain conditions. We first analyze requirements for real-time tracing in multicores as a function of the number of cores by running a set of parallel benchmark programs. We analyze trace port bandwidth requirements for control-flow Nexus-like trace  $(mcfNX_b)$  and load data value traces  $(mlvNX_b)$ . We introduce two new techniques for capturing and compressing hardware traces, namely mcfTRaptor for control-flow traces and mlvCFiat for load data value traces. mcfTRaptor is a multicore implementation of the previously proposed single-core technique called TRaptor [4]. mlvCFiat is a multicore implementation of the previously proposed techniques as a function of the complexity of the proposed hardware predictors and encoding mechanism. Experimental evaluation involves both functional traces collect-

ed using mTrace tools [6] and timed traces collected using a cycle-accurate architectural simulator [7].

#### 1.3 Main Results

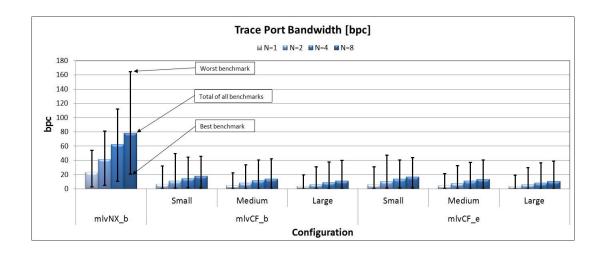

The main results of our experimental evaluation are as follows. The total trace port bandwidth for Nexus-like control-flow hardware traces ( $mcfNX_b$ ) for the Splash2x benchmark suite ranges from 0.93 bits per instruction executed when the number of cores N = 1 to 1.15 bpi when N = 8. The trace port bandwidth in bits per clock cycle is 1.21 when N = 1 and 4.68 when N = 8. The total trace port bandwidth for Nexus-like load data value traces ( $mlvNX_b$ ) ranges from 18.25 bits per instruction when N = 1 to 19.08 when N = 8. The trace port bandwidth in bits per clock cycle is 23.7 when N = 1 and 78.56 when N = 8. These results indicate that capturing control-flow and especially load data value traces on the fly in multicores requires both large trace buffers and wide trace ports.

The proposed mcfTRaptor method dramatically reduces the trace port bandwidth. With mcfTRaptor, the trace port bandwidth ranges from 0.07 when N = 1 to 0.09 bpi when N = 8, a 12-fold improvement relative to the Nexus-like control-flow trace. With a large [Section 4.3.3] configuration the improvement is between 36.5 times when N = 1 and 30.3 times when N = 8. tmcfTRaptor involves streaming out timestamps with each trace message and is also very effective, providing improvements of  $12 \sim 13$  times for a small [Section 4.3.3] configurations and  $18 \sim 20$  times for a large configurations relative to the Nexus-like timed control-flow trace.

The proposed *mlvCFiat* technique offers significant improvements relative to the Nexus-like load data value traces. The trace port bandwidth is reduced 3.9

times when N = 1 and 4.6 when N = 8 for relatively small [Section 4.3.3] data caches. The trace port bandwidth is reduced 6.7 times when N = 1 and for 7.4 times when N = 8 for relatively large [Section 4.3.3] data cache sizes. tmlvCFiat achieves even better results mainly due to relatively smaller data sets used in the Splash benchmarks that serve as the workload for timed traces.

#### 1.4 Contributions

This thesis makes the following contributions to the field of hardware support of on-chip tracing and debugging in multicore processors:

- Introduces mcfTRaptor and mlvCFiat, hardware/software techniques for capturing and compressing hardware control-flow traces (mcfTRaptor) and load data value traces (mlvCFiat) in multicores;

- Develops framework for experimental evaluation of tracing techniques for functional and timed control-flow and load data value traces;

- Evaluates effectiveness of techniques for functional (mcfNX and mcfTRaptor)

and timed control-flow tracing (tmcfNX and tmcfTRaptor);

- Evaluates effectiveness of techniques for functional (mlvNX and mlvCFiat)

and timed load data value tracing (tmlvNX and tmlvCFiat).

### 1.5 Outline

The outline of this thesis is as follows. Chapter 2 gives background, focusing on control-flow trace and memory data traces, tracing and debugging in embedded systems, and commercial and academic state-of-the-art. Chapter 3 introduces the *mcfTRaptor* and *mlvCFiat* techniques for filtering and compressing control-flow and

load data value traces in multicores. Chapter 4 describes our experimental evaluation for functional traces. Chapter 5 describes the results of the experimental evaluation for functional traces. Chapter 6 describes our experimental evaluation of timed traces and Chapter 7 describes the results of the evaluation. Finally, Chapter 8 gives concluding remarks.

## **CHAPTER 2**

#### BACKGROUND AND MOTIVATION

Efforts are never in vain - Do not despair

--Rev. Pandurang Shastri Athavale

This Chapter focuses on types of program execution traces, namely controlflow (Section 2.1) and memory data read and write traces (Section 2.2), that are commonly used in program debugging. Section 2.3 gives a more detailed system view of trace-based debugging in embedded systems and surveys the commercial state-of-the-art. Section 2.4 gives a brief survey of the academic state-of-the-art in the field of capturing and compressing program execution traces.

# 2.1 Control Flow Traces

Control-flow traces are created by the recording memory addresses of all committed instructions in a program. However, such traces include a lot of redundant information that can be inferred by the software debugger with access to the program binary. To recreate the program's control-flow off-line, the debugger needs only information about changes in the program flow caused by control-flow instructions or exceptions. When a change in control-flow occurs, we could record the program counter (PC) and the branch target address (BTA) in case of a control-flow instruction or the exception target address (ETA) in case of an exception. However, such a sequence of (PC, BTA/ETA) pairs still contains redundant information. To

reduce the number of bits to encode lengthy (PC, BTA/ETA) pairs, we can replace PC with the number of sequentially executed instructions in an *instruction stream*, also known as stream length (SL). An instruction stream or dynamic basic block is a sequence of sequentially executed instructions starting at the target of a taken branch and ending with the first taken branch in the sequence [8],[9]. In addition, the target addresses of direct taken branches (BTA) do not need to be recorded as they can be inferred by the software debugger. Therefore, to recreate the program's control-flow in the software debugger, only the following changes in the control-flow need to be reported from the target platform.

- A taken conditional direct branch generates a trace message that contains only the number of sequentially executed instructions in the instruction stream, (SL, -); the target address can be inferred from the program binary.

- An indirect unconditional branch generates a trace message that includes the stream length and the address of the indirect branch, (SL, BTA); and

- An *exception event* generates a trace message that includes the message type (*eType*), the number of instructions executed since the last reported event (*iCnt*), and the exception target address (*ETA*), (*eType*, *iCnt*, *ETA*).

For multicores executing multithreaded programs, control-flow trace messages need to include information about the core on which a particular code segment has been executed. Note: Without loss of generality, we assume that each thread executes on a single core (Ti = Ci). Though threads can migrate between the cores, these migrations can be captured by system software rather than through hardware methods and can be merged with the hardware trace in the software debugger.

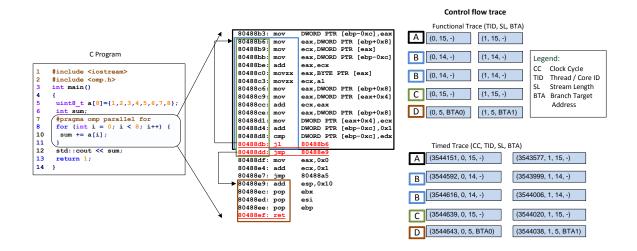

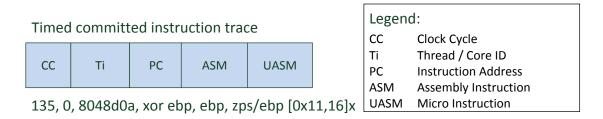

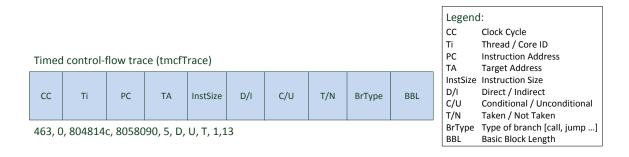

To illustrate capturing control-flow traces of a multithreaded program, consider the OpenMP C program shown in Figure 2.1 that sums up elements of an integer array. An assembly code snippet in the middle shows the instructions executed. We can identify the following instruction streams: the stream A with 15 instructions starting at the address 0x80488b3, the stream B with 14 instructions starting at the address 0x80488b6, the stream C with 15 instruction starting at the address 0x80488b6, and the stream D with 5 instructions starting at the address 0x80488e9. The same code snippet is executed in two threads (Ti = 0 and Ti = 1). Figure 2.1 shows a functional control-flow trace for both threads. Each thread sums up 4 elements of the original array and the sequence of reported instruction streams is as follows: A, B, B, C, D. The stream D ends with an indirect branch (retq instruction), so the last trace message will also include the target address (not known in compile time). The streams A, B, and C end with direct branches with inferable targets, and thus their target addresses are not included (traced out). On the bottom, timed trace messages are shown that include time stamps recording the clock cycle when a particular trace message is captured.

Figure 2.1. Control-flow trace: an example

# 2.2 Memory Data Traces

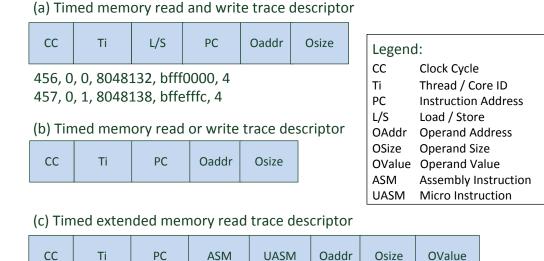

Memory data traces are created by recording relevant information for each memory read or write operation in a program execution. This information typically includes the following: the instruction address (PC), type of memory operation -- read or write (R/W), the operand address (OA), the operand size (OS), and the operand value (OV). In multicores, each trace record should include the thread or core index (Ti). Finally, in the case of timed traces, each record includes a time stamp indicating the clock cycle in which the event has occurred.

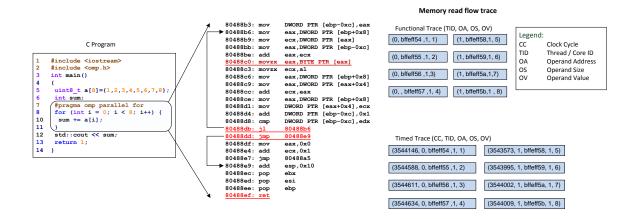

Figure 2.2 shows a memory read trace excerpt for the OpenMP C program shown in Figure 2.1. On the right hand side the flow trace records caused by the move instruction at address 0x80488c0 that reads a byte from the input byte array. Each trace record includes the thread index, the operand address, the operand size, and the operand value. Below are the trace records that in addition to the fields above include time stamps when particular memory reads have completed.

Figure 2.2. Memory read trace: an example

Control-flow traces alone are sufficient to reconstruct the program-flow. However, for certain classes of software bugs (e.g., data races), control-flow traces alone are insufficient and data traces are also required. Data traces are critical in multicore systems, as they offer valuable information about shared memory access patterns and possible data race conditions. Unfortunately, data traces tend to be very large: a 64-bit machine reading an 8-byte operand from memory generates a trace record with more than 24 bytes (8 byte instruction address, 8-byte operand address, 8-byte operand value). Streaming an entire memory data trace through a trace port is thus cost prohibitive. Fortunately, replaying the program offline requires only memory reads and not writes, as that information is infer from software debugger.

The software debugger needs only a portion of the data trace to replay the program. Exception traces and load (memory read) data value traces captured on the target platform and streamed out to a software debugger are necessary to deterministically replay programs offline. Exception traces are created by recording

exceptions that occur in program execution, and load data value traces record only values read from memory and I/O devices. In addition to the traces, the software debugger needs the following to faithfully replay the program offline: (i) an instruction set simulator (ISS) of the target platform, (ii) access to the program's binary, and (iii) the initial state of the general-purpose and special-purpose registers of individual cores. ISS is a simulation model tool to mimic the behavior of processors. In multicores, the exception and data traces need to be either streamed in the order of occurrence or with global timestamps.

# 2.3 Tracing in Embedded Multicores

Trace and debug modules encompass hardware that can support different classes of debugging and tracing operations. The IEEE Nexus 5001 standard [2] defines functions and interfaces for debugging and tracing in embedded processors for four classes of debugging and tracing operations (Class 1 – Class 4). Class 1 supports basic debug operations for run-control debugging such as single-stepping, setting breakpoints, and examining and modifying processor registers and memory locations when the processor is halted. It is traditionally supported through a JTAG interface [10]. The higher classes progressively add more sophisticated operations at the cost of additional on-chip resources (logic, buffers, and interconnects) solely devoted to tracing and debugging. Thus, Class 2 adds support for nearly unobtrusive capturing and streaming out control-flow traces in real-time. Class 3 adds support for capturing and streaming out data-flow trace (memory and I/O read and write data values and addresses). Finally, Class 4 adds resources to support emulated memory and I/O accesses through the trace port.

Class 1 operations are routinely deployed in modern platforms. However,

Class 1 operations are lacking in several important aspects. First, they place a burden on software developers to perform time-consuming and demanding steps such as

setting breakpoints, single-stepping through programs and examining visually the

content of registers and memory locations. Moreover, setting breakpoints is not

practical or feasible in cyber-physical and real-time systems. Finally, since the processor needs to be halted, the debugging operations are obtrusive and may perturb

sequences of events on the target platform and thus cause original bugs to disappear

during debug runs.

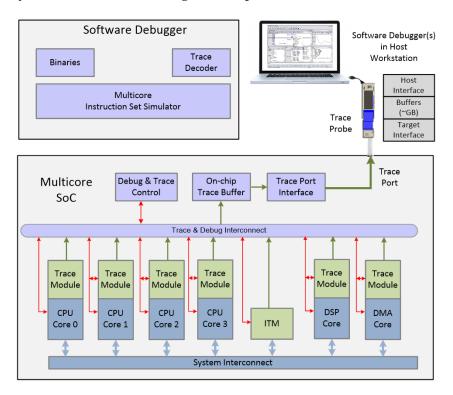

To address these challenges, many chip vendors have recently introduced trace modules with support for Class 2 and less frequently for Class 3 debug and trace operations. Figure 2.3 shows a typical embedded system-on-a-chip (SoC) with multiple processor cores and its debugging and tracing resources. The SoC is connected to a trace probe system through a trace port. The multicore SoC includes various components, such as multiple processor cores (Core0 – Core3), a DSP core, and a DMA core, all connected through a system interconnect. Each component includes its own trace and debug logic (trace modules) that captures program execution traces of interest. Individual trace modules are connected through a trace and debug interconnect to on-chip trace buffers. On-chip buffers store program execution traces temporarily before they are read out through a trace port to an external trace probe. The external trace probe typically includes large trace buffers on the order of gigabytes and interfaces to the target platform's trace port and to the host workstation. The host workstation runs a software debugger that replays the program execution offline by reading and processing the traces from the external probe and

executing the program binary. This way, software developers can faithfully replay the program execution on the target platform and gain insights into the behavior of the target system while it is running at full speed.

Figure 2.3 Debugging and tracing in multicores: a detailed view

Some examples of commercial trace modules include ARM's CoreSight [3], MIPS's PDTrace [11], Infineon's MCDS [12], and Freescale's MPC5500 [13]. State-of-the-art trace modules employ filtering and encoding to reduce the number of bits necessary to recreate program execution. Yet, trace port bandwidths are still in the range of 1 to 4 bits per instruction executed per core for control-flow traces [3] and 8 to 16 bits per instruction executed per core for data-flow traces [3]. With these trace port bandwidth requirements, a 1 KB on-chip buffer per processor core may capture

control-flow of program segments on the order of 2,000-8,000 instructions or dataflow of program segments of merely 400-800 instructions. Such short program segments are often insufficient for locating software errors in modern systems with

more sophisticated software stacks where a distance between a bug's origin and its

manifestation may span billions of executed instructions. Increasing the size of the

buffers and the number of pins for trace ports is not an attractive alternative to chip

manufacturers as it significantly increases the system complexity and cost. This

problem is exacerbated in multicore processors where the number of I/O pins dedicated to trace ports cannot keep pace with the exponential growth of the number of

processor cores on a single chip. Yet, debugging and tracing support in multicores is

critical because of their increased proliferation in embedded systems and their increased sophistication and complexity.

#### 2.4 Related Work

Commercially available trace modules typically implement only rudimentary forms of hardware filtering with a relatively small compression ratio. Irrgang and Spallek analyzed the Nexus and trace port configurations and their impact on achievable compression for instruction traces and found port width of 8bits with history messaging is effective [14]. Several recent research efforts in academia propose trace-specific compression techniques that achieve higher compression ratios. These techniques rely on hardware implementations of general-purpose compressors [15] [16]. For example, Kao et al. [17] introduce an LZ-based compressor specifically tailored to control-flow traces. The compressor encompasses three stages: filtering of branch and target addresses, difference-based encoding, and hardware-based LZ

compression. Novel approach, stream based compression algorithm[18] exploits inherent characteristics program execution traces for compression. A double-move-to-front compressor introduced by Uzelac and Milenkovic [15] encompasses two stages, each featuring a history table performing the move-to-front transformation. Although these techniques significantly reduce the size of the control-flow trace that needs to be streamed out, they have a relatively high complexity (50,000 gates and 24,600 gates, respectively).

A set of recently developed techniques relies on architectural on-chip structures such as stream caches[19], [20], [21] and branch predictors [4] [22] [23] with their software counterparts in software debuggers, as well as effective trace encoding to significantly reduce the size of traces that needs to be streamed out [4], [5],[19],[20]. Uzelac et al. [4] introduced *TRaptor* for control-flow traces that achieves 0.029 bits per instruction on the trace port (~34-fold improvement over the commercial state-of-the-art) at hardware cost of approximately 5,000 gates. For load value traces, Uzelac and Milenkovic [24] [5] introduced cache first-access tracking mechanism (c-fiat) that reduces the trace size between 5.8 to 56 times, depending on the cache size.

However, these techniques have been demonstrated on uniprocessors only. The problem of tracing requirements in multicores running parallel programs is not fully understood. What is the required trace port bandwidth? How does trace port bandwidth scale up with a multiple processor cores? How the existing techniques may be applied to multicores? These are some of the questions that needs to be fully addressed [25]. In this thesis, we want to explore requirements for real-time tracing

in multicores and introduce cost-effective solutions that scale well with a multiple processor cores.

## **CHAPTER 3**

# NEW TECHNIQUES FOR TRACING IN MULTICORES

Continue to make efforts, pray for help, and help is assured – Do not lose faith --Rev. Pandurang Shastri Athavale

This chapter describes *mcfTRaptor* and *mlvCFiat* techniques for capturing and compressing hardware control-flow and load-value data traces in multicore embedded processors.

## $3.1 \quad mcfTRaptor$

In this section, we introduce a technique called multicore control flow tracing branch predictor alias mcfTRaptor. mcfTRaptor is an extension of the existing TRaptor technique for capturing and filtering control-flow traces in single-core processors [4], [24]. Figure 3.1 illustrates a multicore system-on-a-chip with tracing and debugging resources. The multicore connects to a software debugger running on a development workstation via a debug & trace interface. Each core has its own trace module that captures information about committed control-flow instructions. The trace module includes predictor structures in hardware, solely dedicated to capturing and filtering control flow traces. These structures are looked up and updated every time a non-inferable control-flow instruction (a conditional branch or an indirect branch) commits in the corresponding processor core. For a given control-flow instruction, the predictor structures either (a) correctly predict the outcome or target address; (b) incorrectly predict the outcome or target address, or (c) cannot make a

prediction (e.g., due to a predictor miss). In all cases, the predictor structures are updated based on their update policies, similarly to branch predictors in processor pipelines. The key insight that leads to a significant reduction in the number and size of trace messages is that trace messages need be generated only when rare mispredictions occur in the *mcfTRaptor* structures on the target platform. The messages are stored in a trace buffer, streamed out of the platform, and read by the software debugger. The software debugger has access to the program binary, instruction set simulator, and the trace messages captured on the target platform. The debugger maintains software copies of all *mcfTRaptor* structures. These structures are looked up and updated during program replay in the same way their hardware counterparts are looked up and updated on the target platform.

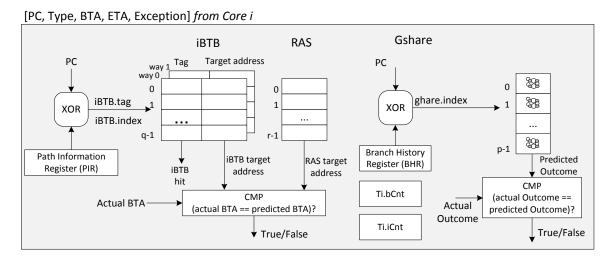

Figure 3.2 shows a block diagram of typical *mcfTRaptor* structures for the core with index *i*. The processor's trace module receives information about committed control flow instructions including, time, program counter (PC), direct/indirect branch type, outcome (taken/not taken), and branch target address (BTA) or exception target address (ETA). *mcfTRaptor* includes structures for predicting (a) target addresses of indirect branches, e.g., an indirect Branch Target Buffer (iBTB) and a Return Address Stack (RAS) [26]; and (b) outcomes of conditional branches, such as an outcome gshare predictor [7]. In addition, *mcfTRaptor* includes two counters: an instruction counter *Ti.iCnt* and a branch counter *Ti.bCnt*. *Ti.iCnt* is incremented upon retirement of each executed instruction, and *Ti.bCnt* is incremented only upon retirement of control-flow instruction that could generate trace messages (e.g., conditional direct and unconditional indirect branches).

Figure 3.1 A system view of mcfTRaptor

Figure 3.2. mcfTRaptor structures for core i

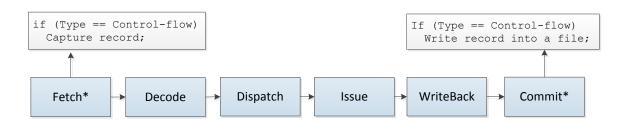

Figure 3.3 describes the operation of a trace module attached to core i when capturing control-flow tracing using mcfTRaptor. The instruction counter is incremented for each control-flow instruction capable of generating a trace message. For indirect unconditional branches, the trace module generates a trace message only if the predicted target address does not match the actual target address. For direct conditional branches, the trace module generates a trace message only if the predicted outcome does not match the actual outcome. When a trace message is generated and placed in a trace buffer for streaming out, the counters Ti.iCnt and Ti.bCnt are cleared. The predictor structures are updated according to an update respective structures. In case of exceptions, a trace message is generated with Ti.bCnt = 0 to indicate a special case, followed by the instruction count (Ti.iCnt) and the exception address (Ti.ETA).

```

1. // For each committed instruction in Thread with index i on core i

2. Ti.iCnt++; // increment iCnt

3. if ((Ti.iType == IndBr) || (Ti.iType == DirCB)) {

Ti.bCnt++; // increment bCnt

5.

// target address misprediction

if ((Ti.iType == IndBr) && (Ti.BTA != p.BTA)) {

6.

7.

Encode&Emit trace message <Ti, Ti.bCnt, Ti.BTA>;

8.

Place trace message into the Trace Buffer;

9.

Ti.iCnt = 0;

10.

Ti.bCnt = 0;

11.

// outcome misprediction

12.

13.

else if ((Ti.iType==DirCB) && (Ti.Outcome != p.Outcome)) {

14.

Encode&Emit trace message <Ti, Ti.bCnt>;

15.

Place trace message into the Trace Buffer;

16.

Ti.iCnt = 0;

17.

Ti.bCnt = 0;

18.

19.

Update predictor structures;

20. }

21. if (Exception event) {

Encode&Emit trace message <Ti, 0, iCnt, ETA>;

22.

23.

Place record into the Trace Buffer;

24.

Ti.iCnt = 0;

25.

Ti.bCnt = 0;

26. }

```

Figure 3.3 mcfTRaptor operation on core i

The software debugger replays the instructions as shown in Figure 3.4. The replay starts by reading trace messages for each thread and initializing the counters. If a non-exception trace message is processed, the software copy of Ti.bCnt is decremented every time a control-flow instruction is executed. For indirect unconditional branches, if the counter reaches zero, the actual target address is retrieved from the current trace message; otherwise if (Ti.bCnt > 0), the target address is retrieved from the mcfTRaptor structures maintained by the software debugger. For direct conditional branches, if the counter reaches zero, the actual outcome is opposite to the one provided by the mcfTRaptor structures maintained by the software debugger; otherwise if (Ti.bCnt > 0), the actual outcome matches the predicted one. When Ti.bCnt reaches zero, the next trace message for that thread is fetched. Handling of exceptions events is described in lines 3-8 in Figure 3.4.

```

// For each instruction on core i

Replay the current instruction (if not trace event generating);

if (Exception message is processed) {

4.

Ti.iCnt--;

if (Ti.iCnt == 0) {

5.

Go to exception handler at Ti.ETA;

6.

7.

Get the next trace message;

8.

9. }

10. if ((Ti.iType == IndBr) || (Ti.iType == DirCB)) {

11.

Ti.bCnt--; // decrement Ti.bCnt

12.

if ((Ti.iType == IndBr) && (Ti.bCnt > 0))

13.

Actual BTA = predicted BTA in software;

14.

else if (Ti.iType == DirCB) && (Ti.bCnt > 0))

Actual outcome = predicted outcome in software;

15.

16.

else if ((Ti.iType == IndBr) && (Ti.bCnt == 0))

17.

Actual BTA = BTA read from the trace message;

18.

else if (Ti.iType == DirCB) && (Ti.bCnt == 0))

19.

Outcome is opposite to predicted outcome;

20.

Update software predictor structures;

if (Ti.bCnt == 0) Get the next trace message;

21.

22. }

```

Figure 3.4 Program replay in software debugger for mcfTRaptor

## 3.2 mlvCFiat

mlvCFiat or multicore load value cache first access tacking is a hardwarebased mechanism that reduces load data value traces by collecting a minimal set of trace messages through the use of a cache first access mechanism. mlvCFiat is an extension of the existing CFiat mechanism for capturing and filtering load data value traces in single-core processors [5], [24].

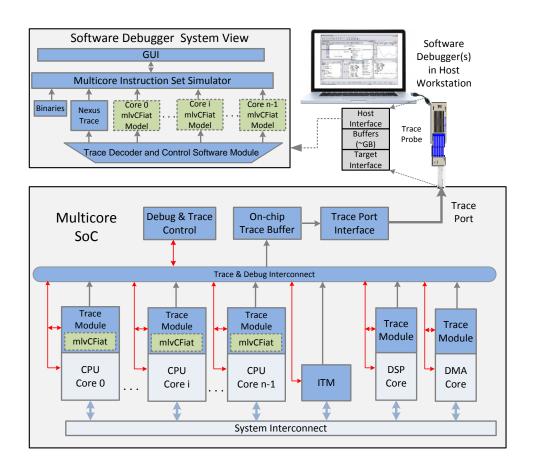

Figure 3.5 shows a block diagram of a multicore SoC with infrastructure for debugging and tracing; green boxes represent additional *mlvCFiat* modules. Each processor core is coupled to its trace module through an interface that carries information about committed memory read and memory write instructions. The trace module includes structures in hardware solely dedicated to capturing and filtering memory read traces. The *mlvCFiat* structure is looked up when instructions that

read from or write to memory commit in the corresponding processor core. The key insight that leads to a significant reduction in the number and size of trace message is that trace messages need to be generated only when misprediction occur in the *mlvCFiat* structures on the target platform. The messages are stored in a trace buffer, streamed out of the platform, and read by the software debugger. The software debugger has access to the program binary, instruction set simulator, and the trace messages captured on the target platform. It maintains software copies of all *mlvCFiat* structures. These structures are updated during program replay in the same way their hardware counterparts are updated on the target platform.

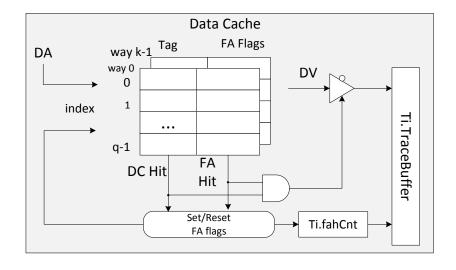

Figure 3.6, shows the *mlvCFiat* structures for core *i*. Each data cache block in each processor core on the target platform is augmented with first access tracking flags. The first access tracking flags keep track of sub-blocks that need to be reported to the software debugger. Let us assume a data cache with 64-byte cache blocks. If a first-access tracking flag protects a 4-byte sub-block, each cache block needs to be augmented with a 16-bit first access flag vector. The previously reported sub-blocks do not have to be reported again as they can be inferred by the software debugger. This way we exploit the temporal and spatial locality of data access to significantly reduce the number of trace events that need to be reported. In addition to the first-access tracking bits, each trace module includes a local first-access counter (*Ti.fahCnt*) that counts the number of consecutive first access hits.

Figure 3.5 A system view of mlvCFiat

Figure 3.6 mlvCFiat structures for core i

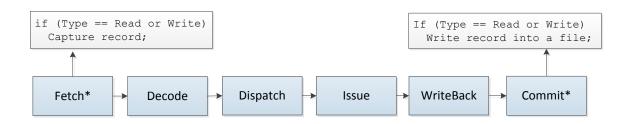

Figure 3.7 describes the operation of the *mlvCFiat* mechanism on core *i*. Each memory read causes a data cache lookup; if the requested data item is found in the data cache (a cache hit event) and the corresponding first-access flags are set (an FA hit event), the data value does not need to be reported to the software debugger and *Ti.fahCnt* is incremented (line 3). In case of an FA miss event, a trace message is streamed out of the chip; it includes the core id (*Ti*), the current value of the *Ti.fahCnt*, and the load data value that is being reported for the first time (line 5). In addition, the corresponding FA flags are set and the counter *Ti.fahCnt* is cleared (line 7 and 8). In case of a data cache miss event, the newly fetched block's FA tracking flags are cleared and then steps 5-8 are carried out. Similarly, external cache block invalidation or update requests clear the corresponding FA flags (line 17). Finally, memory write operations set the corresponding FA tracking flag(s) (line 15).

```

1. // For each instruction that reads n bytes on core i

2. if (CacheHit) {

if (corresponding FA flags are set) Ti.fahCnt++;

else {

5.

Encode&Emit trace message (Ti, Ti.fahCnt, loadValue);

Place trace message into the Trace buffer

7.

Set corresponding FA flags;

8.

Ti.fahCnt = 0;

9.

}

} else { // cache miss event

11.

Clear all FA bits for newly fetched cache block;

12.

Perform steps 5-7;

13. }

14. // For each retired store that writes n bytes

15. Set corresponding FA bits;

16. // For external invalidation/update request

17. Clear FA bits for entire cache block

```

Figure 3.7 mlvCFiat operation on core i

The software debugger carries out steps that mirror actions on the target (Figure 3.8). It maintains software copies of the data caches and the Ti.fahCnt counters; these are updated during program replay using the same policies employed on the target platform. The program replay starts by reading the trace messages received from the target for each core separately. The debugger replays the instructions for each core using ISS. For memory read instructions the debugger performs steps described in lines 1-11. The Ti.fahCnt counter is decremented; if Ti.fahCnt>0, the debugger retrieves the load data value from the software data cache and moves to the next instruction. If Ti.fahCnt = 0 we have a first read miss event; the load value is retrieved from the trace message, the software data cache is updated, and a new trace message for a given core is read from the target.

```

1. // For each load on Core i that reads n bytes

2. Ti.fahCnt --;

3. if (Ti.fahCnt > 0) {

4.

Perform lookup in the SW data cache;

5.

Retrieve data value from SW cache;

6. }

7. else { // FA miss event

Read n bytes from trace record;

Update SW cache;

9.

Get the next trace message (Ti, Ti.fahCnt, LoadValue);

10.

11. }

12. // For each store that writes N bytes

13. Update SW cache;

14. Set corresponding n SW cache FA bits;

```

Figure 3.8 mlvCFiat operation in software debugger for core i

# CHAPTER 4

#### EXPERIMENTAL EVALUATION OF FUNCTIONAL TRACES

Fearlessness is result of faith in one self and faith in God

--Rev. Pandurang Shastri Athavale

Functional program execution traces capture behavioral aspects of running programs. They capture control and data flow information from multithreaded programs, preserving intra-threaded ordering of events, but may not provide accurate inter-thread ordering. We use functional traces (i) to investigate requirements of hardware tracing in multicore platforms and (ii) to evaluate the effectiveness of our techniques and their sensitivity to system parameters. This chapter focuses on our experimental flow based on functional traces.

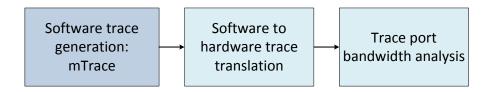

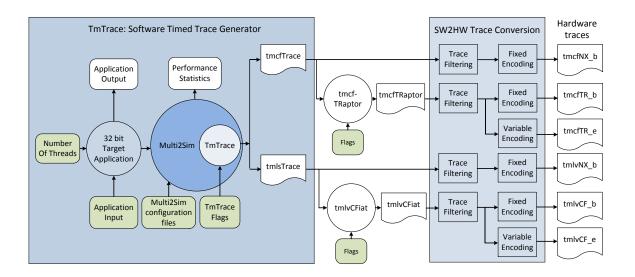

As a measure of effectiveness, we use trace port bandwidth expressed in the number of bits streamed out of the chip per instruction executed (bpi). Figure 4.1 shows the experiment flow for determining trace port bandwidth in case of functional (non-timed) traces. The flow encompasses three steps: (i) software trace generation using the mTrace tool suite [6], (ii) software to hardware trace translation, and (iii) trace port bandwidth analysis. Section 4.1 describes the trace generation step. mTrace is designed to support a range of trace applications, such as Instruction Set Architecture (ISA) profiling, trace-driven simulation, and software trace compression. Thus, mTrace does not include support for analyzing hardware tracing and trace descriptor encoding at the trace port level. In addition, software traces gener-

ated by mTrace often include information that may be inferred by a software debugger. To support the evaluation of trace port bandwidth in the context of hardware tracing on multicore platforms, we develop custom tools that read software traces and produce hardware traces with no redundant information. Section 4.2 describes software to hardware trace translation. Section 4.3 describes the experimental setup, benchmarks used, and the experimental methodology.

Figure 4.1 Experiment flow for determining trace port bandwidth requirements using functional traces

## 4.1 Software Trace Generation

To generate control-flow and data functional traces for multi-threaded software we use the *mTrace* tool suite [6]. Figure 4.2 illustrates a trace generation flow. *mTrace* relies on the Intel's binary instrumentation framework called Pin [27] that works like a just-in-time-compiler and enables custom binary instrumentation through a well-defined application programming interface. The *mTrace* tools are developed as Pin tools and capture functional traces. They take application input parameters, the number of threads, parameters controlling the tracing process, and

configuration parameters for new compression methods as input parameters, and generate raw trace files, optionally, compressed trace files.

The *mTrace* tool suite consists of four different tools:

- *mcfTrace*: a tool for capturing and compressing control-flow traces;

- *mlsTrace*: a tool for capturing and compressing data traces;

- mcfTRaptor: a tool for capturing and compressing control-flow traces using the TRaptor mechanism for multi-threaded programs; and

- mlvCFiat: a tool for capturing and compressing data traces using the CFiat

mechanism for multi-threaded programs.

# Compressed Application Compressor Trace File Output Raw Number Of Target Pin Trace File Threads Application mTrace Tool Suite mTrace Pin Application Tool Input **Parameters**

Trace generation tool - mTrace

Figure 4.2 Functional trace generation using mTrace tool suite

#### 4.2 Software to Hardware Trace Translation

To enable evaluation of trace port bandwidth in the context of hardware tracing on multicore platforms, we develop tools that perform software to hardware trace translation. These tools read raw traces generated by the *mTrace* tools, filter out redundant trace descriptors and redundant trace fields that can be inferred by the software debugger, and perform analysis to determine effective encoding of trace descriptors. The output of the trace analyzer tools is the overall trace port bandwidth measured in bits per instruction executed.

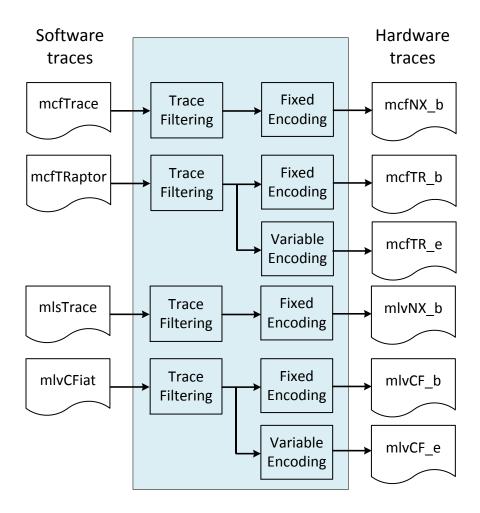

Figure 4.3 shows the flow from input software traces to output hardware traces. Raw control-flow traces generated by the mcfTrace tool are filtered out and encoded to generate Nexus-like hardware control flow traces called  $mcfNX\_b$ . The mcTRaptor control-flow traces generated by the mcfTRaptor tool are also filtered out and then encoded using either a fixed encoding mechanism to generate  $mcfTR\_b$  compressed control-flow hardware traces or using a variable encoding mechanism to generate  $mcfTR\_e$  compressed control-flow hardware traces. This way, we can separately evaluate the effectiveness of the mcfTRaptor filtering mechanism and the effectiveness of encoding mechanisms. Similarly, a memory load data value trace generated by the mlsTrace tool is filtered and encoded to generate a Nexus like hardware load data value trace ( $mlvNx\_b$ ). The mlvCFiat trace is filtered and encoded using a fixed or a variable encoding mechanism to generate compressed memory load data value traces  $mlvCF\_b$  and  $mlvCF\_e$ , respectively. The following subsections shed more light on each of these trace transformations.

Figure 4.3 Software to hardware trace translation

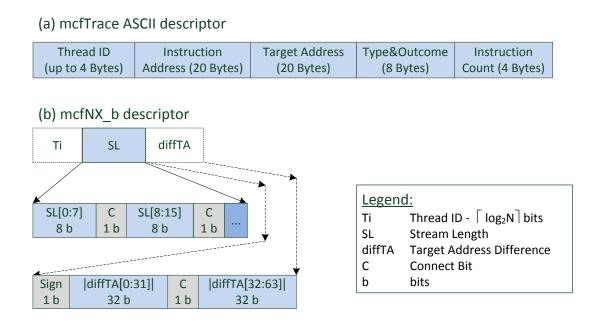

# $4.2.1 \quad mcfNX\_b$

The *mcfTrace* tool captures all control-flow instructions and exceptions. Figure 4.4 (a) shows the format of a trace descriptor generated by *mcfTrace*. A descriptor includes the thread ID, control-flow instruction address (program counter), target address, branch type (direct vs. indirect, conditional vs. unconditional), branch outcome (taken or not taken), and the number of instructions in the basic

block that ends with the control-flow instruction. A descriptor in ASCII format may require up to 58 bytes.

To generate hardware control-flow traces, we filter out information that is not required to replay the program's control-flow offline. To recreate the control-flow, the debugger only needs information about changes in the program flow due to taken conditional branches or exceptions. For each change, we can send the program counter (PC address) and the branch target address (BTA) for branch instructions or exception target address (ETA) for exceptions. Yet, the trace with all (PC, BTA/ETA) pairs still contains redundant information that can be inferred by the debugger providing it has access to the program binary. Instead of sending the program counter we can send the number of instructions executed sequentially from the program starting address or from the target of the last taken branch. The target addresses of direct branches (BTA) can be inferred from the program binary and thus do not need to be streamed out. The target addresses of indirect branches do need to be reported though. However, instead of sending the entire target address, we can send only the absolute difference (|DiffTA|) between the previous indirect branch target address and the current branch target address with sign bit.

Thus, hardware control-flow trace requires tracing descriptors to be emitted as follows:

- for taken direct conditional branches, the trace descriptor should include (Ti, Ti.SL, -), where Ti is the thread ID, Ti.SL is the number of instructions executed in a given thread since the last reported trace descriptor;

- for indirect unconditional branches, the trace descriptor should include (Ti,

Ti.SL, Ti.DiffTA), where Ti.DiffTA is the difference target address; and

• for *exceptions* the trace descriptor should include (Ti, Ti.SL, Ti.ETA).

The resulting format of a trace descriptor for Nexus-like control flow trace is shown in Figure 4.4 (b). To encode the thread index we use 0 bits when N=1, 1 bit for N=2, 2 bits for N=4, and 3 bits for N=8. The number of bits needed to encode the field Ti.SL varies with benchmarks and phases within a benchmark. Instead of using a long field that would encode any possible value of SL, we use Nexus-like encoding with each field divided into multiple chunks. Each chunk is followed by a connect bit that indicates whether it is the terminating chunk (C=0) for the given field or more chunks follow (C=1). For the Nexus-like control-flow trace, we adopt chunk size of 8 bits for the Ti.SL field. Similarly, we encode the absolute value of diffTA into two 32-bit chunks.

Figure 4.4 mcfTrace and mcfNX\_b trace descriptors

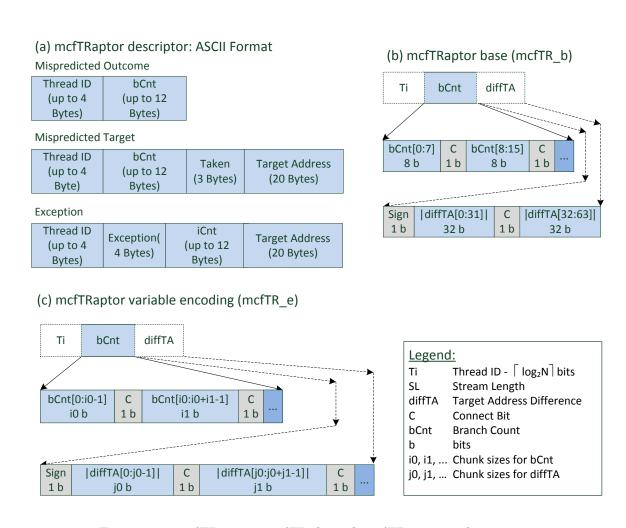

# $4.2.2 \quad mcfTR\_b \text{ and } mcfTR\_e$

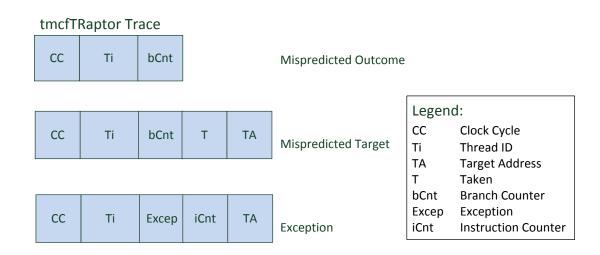

The *mcfTRaptor* tool implementing the *mcfTRapor* trace compression generates *mcfTRaptor* trace descriptors as described in Table 4.1. It emits trace descriptors upon (i) outcome misprediction of conditional branches, (ii) target address misprediction of indirect unconditional branches, and (iii) exceptions. In case of outcome misprediction, a descriptor is emitted that includes information about the thread index, Ti, and the number of branch instructions encountered in a given thread since the last reported event, Ti.bCnt. For indirect unconditional branches, in addition to Ti and Ti.bCnt, the indirect target address, Ti.BTA, is included as well. Finally, in the case of exceptions, the Ti.bCnt is set to a zero, followed by a field with the number of instructions executed since the last reported event (Ti.iCnt), and the exception target address (Ti.ETA). Figure 4.5(a) illustrates the *mcfTRaptor* descriptors in ASCII format that can require from 18 to 46 bytes.

Table 4.1 mcfTRaptor events and trace descriptor fields

| mcfTRaptor Events                                       | Trace Descriptors                    |

|---------------------------------------------------------|--------------------------------------|

| Outcome misprediction for direct conditional branch     | <ti, ti.bcnt=""></ti,>               |

| Target address misprediction for indirect unconditional | <ti, ti.bcnt,="" ti.bta=""></ti,>    |

| branch                                                  |                                      |

| Exception event                                         | <ti, 0,="" td="" ti.icnt,<=""></ti,> |

|                                                         | Ti.ETA>                              |

The *mcfTRaptor* traces are filtered out to replace the target addresses,

Ti.BTA with Ti.diffTA values. The Ti.bCnt and Ti.diffTA fields can take a number of values. Similar to *mcfNX\_b* trace encoding, the branch counter field is divided into

multiple 8-bit chunks. If an 8-bit field is sufficient to encode the counter value, the following connect bit C=0, thus indicating the terminating chunk for Ti.bCnt. Otherwise, C=1, and the following chunk carries the next 8 bits of the branch counter value. The trace descriptors for target address misprediction events carry information about the correct target address. An alternative to reporting the entire address (64-bit in our case) is to encode the difference between subsequent target addresses and thus exploit locality in programs to minimize the size of trace messages. The trace module maintains the previous target address, that is, the target address of the last mispredicted indirect branch (PTA). When a new target misprediction is detected, the trace module calculates the difference target address, diffTA, dif-fTA = TA - PTA and PTA gets the value of current address TA, PTA = TA. The absolute value of diffTA is divided into 32-bit chunks, and the connect bit indicates whether one or two 32-bit fields are needed to encode the message. Figure 4.5 (b) shows the encoding of a generic trace descriptor for mcfTR b.

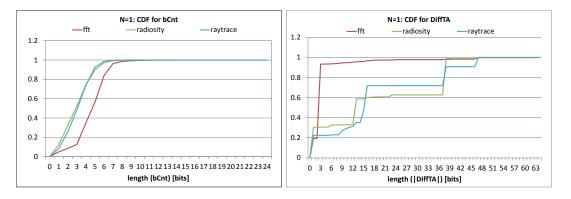

By analyzing profiles of reported counter values (Ti.bCnt and Ti.iCnt) as well as diffTA values, we find that the number of required bits for encoding trace messages can be further minimized by allowing for variable encoding. Instead of using fixed-length chunks for Ti.bCnt, we allow for chunks of variable size, i0, i1, i2, as shown in Figure 4.5 (c). Similarly, we can use variable chunk sizes of lengths, j0, j1, j2, for encoding diffTA. This encoding approach is called  $mcfTR_e$ . The length of individual chunks is a design parameter and can be determined empirically. In determining the length of individual chunks, we need to balance the overhead caused by the connect bits and the number of bits wasted in individual chunks. A detailed analysis to find good chunk sizes is performed and selected parameters are used for

all benchmarks. It should be noted that the variable encoding offers an additional level of flexibility to adjust encoding lengths for individual benchmarks or even inside different phases of a single benchmark. However, dynamic adaptation of the field lengths is left for future work.

Figure 4.5 mcfTRaptor, mcfTR\_b, and mcfTR\_e trace descriptors

## $4.2.3 \quad mlvNX \ b$

The *mlsTrace* tool generates the load or store trace descriptors as shown in Figure 4.6(a). A descriptor contains information about the thread index, the instruc-

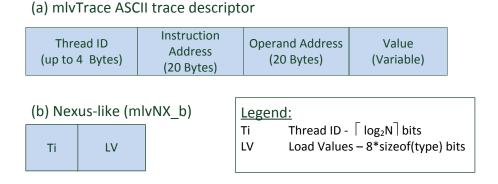

tion address (PC), the operand address, and the operand value. The software debugger needs the following to faithfully replay the program offline: (i) an instruction set simulator (ISS) of the target platform, (ii) access to the program binary, (iii) the initial stage of the general purpose and special purpose registers of the individual cores, and (iv) the load data values read from memory or input/output devices. Thus, the trace generated by the *mlsTrace* tool can be filtered out to remove the load instruction addresses (PC) and the operand address that can be inferred in the ISS. Figure 4.6 (b) shows the trace descriptor for Nexus-like load data value trace. The descriptor contains only the thread index and the load data value. The length of the load value field depends on the size of the operand specified by the instruction, and for the Intel 64 ISA varies between 1 byte and 120 bytes.

Figure 4.6 *mlvTrace* and *mlvNX* b trace descriptors

# $4.2.4 \quad mlvCF\_b \text{ and } mlvCF\_e$

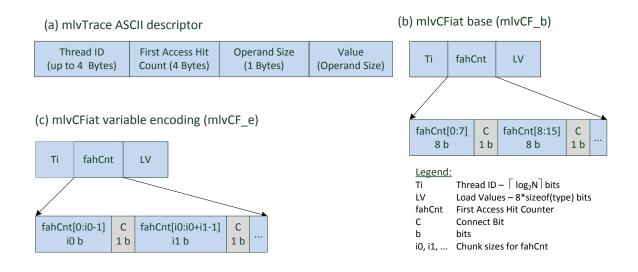

The *mlvCFiat* tool generates trace descriptors as shown in Figure 4.7(a). A descriptor contains information about the thread index, the first access hit counter (fahCnt – number of consecutive first access hit events), the operand size, and the operand value. The operand size can be inferred by the software debugger with an

instruction set simulator and program binary. Figure 4.7 (b) shows trace descriptors for Nexus-like load data value trace ( $mlvCF_b$ ). The descriptor includes the thread index (Ti), the first access hit counter, Ti.fahCnt, and the load value (Ti.LV). The number of bits needed to encode Ti.fahCnt varies as a function of the first-access miss rate. With  $mlvCF_b$  we use at least 8 bits to encode the Ti.fahCnt. The connect bit (C) determines whether more 8-bit chunks are needed to fully encode Ti.fahCnt value (C = 1) or not (C = 0).

Figure 4.7 mlvTrace, mlvCF\_b, and mlvCF\_e trace descriptors

With  $mlvCF_e$ , we allow the length of individual chunks,  $i\theta$  and i1 in Figure 4.7(c), to be between 1 and 8 bits. We evaluate different encoding arrangements to select a pair of good values that minimizes the number of bits needed to encode the counter value.

# 4.3 Experimental Environment

The goal of experimental evaluation is to determine the effectiveness of the newly proposed trace reduction techniques, mcfTRaptor and mlvCFiat, relative to the baseline Nexus-like control-flow,  $mcfNX\_b$ , and load data value traces,  $mlvNX\_b$ . To explore the effectiveness of mcfTRaptor and mlvCFiat, their structure sizes and configurations are varied. As a measure of effectiveness, we use the average number of bits emitted on the trace port per instruction executed. As the workload, we use control flow and load data value traces of 14 benchmarks from the Splash2x benchmark suite [28] collected on a machine executing the Intel 64 ISA. Machine setup is described in Section 4.3.1. The benchmarks are discussed in Section 4.3.2. Section 4.3.3 describes experiments conducted and Section 4.3.4 describes selection of encoding parameters for variable encoding mechanism.

## 4.3.1 Experimental Setup

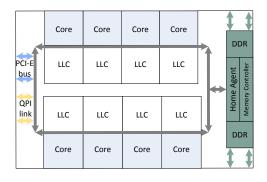

The setup included a Dell PowerEdge T620 server with two octa-core Intel Xeon CPU E5-2650 v2 processors with total of 64 GB physical memory (Figure 4.8). The server runs the Ubuntu 14.04 operating system with 3.13.0-39-generic Linux kernel. The *mTrace* tools used Pin version 2.13.

Figure 4.8 Block diagram of Intel Xeon E5-2650 v2 processor socket

#### 4.3.2 Benchmarks

As a workload we use a full set of SPLASH2x [28] benchmarks. SPLASH2x is a collection of applications and kernels in the area of high performance and parallel computing. Each benchmark was executed with N = 1, 2, 4 and 8 processor cores. Each benchmark has six different input sets as follows: Test and Simdev are used for testing and development; Simsmall, Simmedium and Simlarge are used for simulations; finally, Native is used for the native program execution on actual hardware platforms. We use the *Simsmall* input set.

The trace port bandwidth for control flow traces depends on benchmark characteristics, specifically the frequency and type of control-flow instructions. Similarly the trace port bandwidth for load data value traces depends on the frequency and type of memory reads and data value sizes. Table 4.2 shows the control flow characterization of all 14 benchmarks in the SPLASH2X suite. The suite was compiled for the Intel 64 instruction set architecture with varying number of thread varies (N = 1, 2, 4, and 8). We show the number of executed instructions (instruction count) and the number of instructions executed per clock cycle (IPC). The last four columns show the frequency of control flow instructions for single threaded programs (N = 1), as well as the frequency of conditional direct branches (C, D), unconditional direct branches (U, D), and unconditional indirect branches (U, I). The number of instructions slightly increases with an increase in the number of threads due to overhead and data partitioning. The number of instructions varies between 0.367 (lu\_ncb) ~ 3.2 (water-spatial) billion. The SPLASH2x benchmarks exhibit diverse behavior with respect to control flow instructions; their frequency ranges from as high as ~15% (raytrace, radiosity) to as low as 1.06% (radix). The total frequency of control

flow instructions is relatively low (9.57%). Conditional direct branches are the most frequent type of branches.

Table 4.2 Splash2x benchmark suite control flow characterization

| Benchmark | Instr  | ruction C | ount [x1 | 09]    | Instr | uctior | per ( | Cycle | % branches for Thread=1 |       |      |       |  |

|-----------|--------|-----------|----------|--------|-------|--------|-------|-------|-------------------------|-------|------|-------|--|

| Thread    | 1      | 2         | 4        | 8      | 1     | 2      | 4     | 8     | branch                  | C,D   | U,D  | U,I   |  |