# Microbenchmarks For Determining Branch Predictor Organization

Milena Milenkovic, Aleksandar Milenkovic, Jeffrey Kulick

Electrical and Computer Engineering Department

The University of Alabama in Huntsville

301 Sparkman Drive, Huntsville, AL 35899

E-mail: {milenkm, milenka, kulick}@ece.uah.edu

## Summary

In order to achieve an optimum performance of a given application on a given computer platform, a program developer or compiler must be aware of computer architecture parameters, including those related to branch predictors. Although dynamic branch predictors are designed with the aim to automatically adapt to changes in branch behavior during program execution, code optimizations based on the information about predictor structure can greatly increase overall program performance. Yet, exact predictor implementations are seldom made public, even though processor manuals provide valuable optimization hints.

This paper presents an experiment flow with a series of microbenchmarks that determine the organization and size of a branch predictor using on-chip performance monitoring registers. Such knowledge can be used either for manual code optimization or for design of new, more architecture-aware compilers. Three examples illustrate how insight into exact branch predictor organization can be directly applied to code optimization. The proposed experiment flow is illustrated with microbenchmarks tuned for Intel Pentium III and Pentium 4 processors, although they can easily be adapted for other architectures. The described approach can also be used during

processor design for performance evaluation of various branch predictor organizations and for testing and validation during implementation.

**Keywords:** compiler optimizations, microbenchmarks, branch predictor, performance monitoring

## Introduction

Better performance of today's microprocessors is not only due to the increase in the operating frequency, but also due to the increase in processor complexity in every new generation. Compilers must keep up with new processor features, such as extended instruction set, pipelining, multiple-level cache hierarchy, instruction level parallelism, and branch prediction, exploiting new optimization possibilities. Although compilers for new processors do include some advanced optimization features, for instance the Intel C++ Compiler [1], future compilers must be even more aware of the underlying architecture. Currently, program developers must specifically set compiler switches that notify the compiler for which architecture to optimize the code. The Intel processors also include CPUID—CPU Identification Instruction that provides information about some of the processor features, such as cache and TLB [1]. Another way to extract required information is to perform a series of microbenchmarks that experimentally explore architectural properties. For instance, a program can automatically determine memory hierarchy parameters [2], [3]. This kind of program can be incorporated into future compilers: the compiler would first assess relevant architectural parameters of a processor and then optimize the code according to the obtained parameter values. The information about underlying architecture can also be applied to manual code optimizations, such as a blocking transformation that improves code spatial locality [4].

The successful resolution of conditional branches is a crucial performance issue in modern superscalar processors. When a conditional branch enters the execution pipeline, all instructions following the branch must wait for the branch resolution. A common solution to this problem is speculative execution: the branch outcome and/or its target are dynamically or statically predicted,

so the execution can go on without stalls. If a branch is mispredicted, speculatively executed instructions must be flushed and their results discarded, thus wasting a significant number of processor clock cycles. For example, the Pentium 4 has a misprediction penalty of 20 clock cycles [5], and future processors may have even higher penalties, up to 50 clock cycles [6], since deep pipelines are necessary for achieving very high clock frequencies.

With static branch prediction, a branch outcome is predicted statically at compile time using the branch type, branch direction, and/or profiling information. Although static prediction may work well for some applications, dynamic prediction solves more general cases, since it is able to automatically adapt to changes in branch behavior during program execution. Predictor size and organization may limit its ability to give a correct prediction. If the compiler/developer is aware of the branch predictor intricacies, the code can be optimized to overcome some limitations, and consequently the overall program performance increases.

Modern processors, such as Intel Pentium III (P6 architecture) and Pentium 4 (NetBurst architecture), include some form of dynamic branch prediction mechanisms, but available information about exact predictor organization is rather scarce. On the other hand, almost all modern processors include performance-monitoring registers that can count several branch-related events, and quite powerful tools for easy access to these registers are available [7], [8].

This paper presents an experiment flow that uncovers branch predictor organization using performance-monitoring registers and illustrates how such knowledge can improve code optimization. A set of "spy" microbenchmarks tests the existence and/or value of particular branch predictor parameters: the use of global and/or local branch history, the number of history bits, and the predictor size and organization (http://www.ece.uah.edu/~lacasa/). Another application of the proposed experiment flow is for testing and validation of the branch predictor design during processor implementation. The microbenchmarks can also be used in research looking for better branch predictors.

The proposed experiment flow is illustrated on Pentium III and Pentium 4 processors, though only minor modifications are necessary to adapt the proposed microbenchmarks to other processor architectures. The results indicate that Pentium III has a local branch predictor with 4 branch history bits, and the Pentium 4 uses a global branch predictor with 16 history bits. The experiments also determine the organization of the branch target buffer and the address bits used to access it.

The next section provides an overview of dynamic branch prediction, followed by examples of predictor-aware code optimizations. A description of the experimental environment sets the stage for a detailed explanation of the proposed experiment flow. Finally, the results of the experiments for observed architectures are presented.

# **Dynamic Branch Prediction**

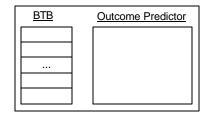

No matter how complex a branch predictor is, it can be described by some variation of the general scheme (Figure 1), consisting of two major parts: a branch target buffer (BTB) for prediction of branch targets, and an outcome predictor for prediction of branch outcomes.

The branch target buffer is a cache structure, where a part of the branch address is used as the cache index, and the cache data is the last target address of that branch. More complex BTBs can hold more than one possible target address and some type of mechanism to choose which target instructions should be speculatively executed. Some implementations can also store target instructions, and even whole target basic blocks [4]. The prediction of branch outcomes can be coupled or decoupled with the BTB: if the outcome predictor and the BTB are coupled, only branches that hit in the BTB are predicted, while a static prediction algorithm is used on a BTB miss. If the BTB is decoupled from the outcome predictor, all branch outcomes are predicted using the outcome predictor.

Figure 1 General Branch Predictor Scheme.

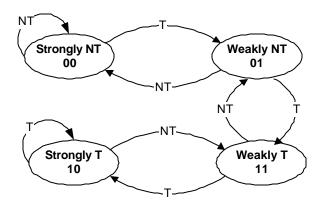

Dynamic prediction of a branch outcome is based on the state of a finite-state machine, which is usually a two-bit saturating counter [9], depicted in Figure 2. In states *Strongly Taken* and *Weakly Taken* a branch is predicted as taken, and it is predicted as not taken in the other two states, *Weakly Not Taken* and *Strongly Not Taken*.

Figure 2 Two-bit saturating counter: T=taken branch; NT=not taken.

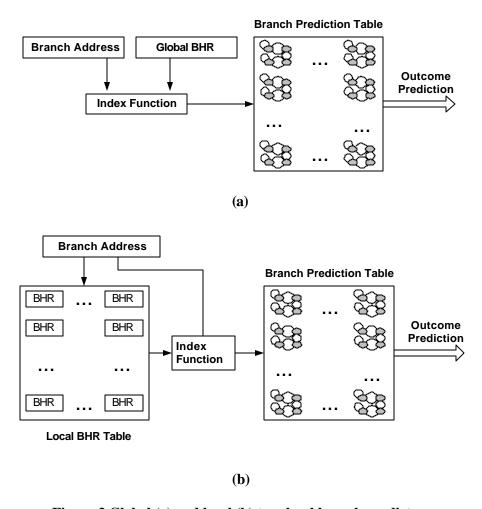

This counter is a cell of a branch prediction table (BPT), which could be accessed in different ways. The simplest BPT index is a portion of the branch address. More complex two-level predictors combine the branch address or a part of it with a branch history register BHR. The BHR is a shift register that keeps the history of *N* most recent branch outcomes, where *N* represents the number of bits of the shift register [10], [11]. The BPT index function is usually a concatenation or exclusive *OR* of the branch address and the corresponding BHR. Based on the type of recorded branch history, the predictors can be global and local. Global two-level predictors benefit from correlations between subsequent branches in the program execution flow (Figure 3a), while local predictors are based on correlation between subsequent executions of the same branch (Figure 3b).

In order to further reduce the number of branch mispredictions in wide-issue superscalar processors, more advanced mechanisms have been proposed, such as hybrid branch predictors. Hybrid branch predictors can include both global and local prediction mechanisms, as well as some other prediction schemes, e.g., specialized loop predictors [12]. Instead of exploiting the correlation between outcomes of the last *N* branches (pattern-based), the dynamic branch predictor can use the information of the path to the current branch (path-based) [13]. The path history register stores address bits from each of the most recently executed *P* branches, thus making the prediction path-dependant. One predictor can combine both pattern-based and path-based approaches. Specialized predictors can handle some special branch types, such as returns and loops.

Figure 3 Global (a) and local (b) two-level branch predictor.

In order to reduce the number of mispredictions, branch predictors are getting larger and more complex. However, code optimizations are still vital for processor performance, since large number of pipeline stages and superscalar fetch/decode make modern processors more sensitive to branch mispredictions.

# **Examples of Branch Optimization by Architecture-Aware Compiler**

The following three examples illustrate how knowledge about underlying branch predictor structure can improve code optimization. The first example deals with processor architectures with global branch predictors, and it is inspired by code generation guidelines explained in Sun's *UltraSparc User's Manual* [14]. The second example shows a possible optimization for local branch predictors, and it is based on hints given in one of the Intel Pentium III optimization guidelines [15]. Finally, the last example shows how knowledge about the size and organization of the branch predictor structure can reduce branch interference. Actual implementation of an architecture-aware compiler, which is outside the scope of this paper, must also take into account other performance factors, such as possible cache miss increases due to changes in executed code length.

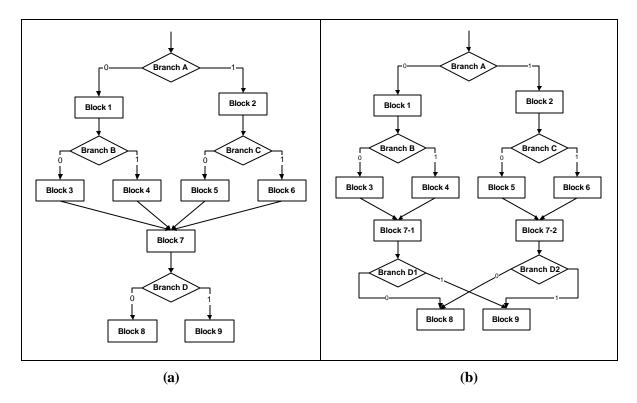

Let us first consider a processor with a global branch predictor that uses N global history bits. This predictor is able to correctly predict the outcome of a branch correlated with up to N previously executed branches, while correlations longer than N cannot be detected. If the outcome of a particular branch depends on more than N previous branches, the compiler can split the code and duplicate branches as necessary, replacing a long branch correlation with several shorter ones.

Figure 4a shows the control flow for one such scenario, where the branch D outcome is the *AND* function of the outcomes of two previously executed branches: A and B, or A and C (Table 1). In this example the branch predictor uses only one bit of global history (N=1). Since the predictor is able to "remember" only one previous branch, it cannot distinguish between branch histories 01, when D is not taken, and 11, when D is taken. The BPT index function takes as

arguments the branch D address and one history bit, so the same BPT cell is accessed in both cases. Assuming a two-bit saturating counter, one or both corresponding branch D outcomes are mispredicted, depending on the counter start state (Table 1a). In the other two cases -- i.e., branch histories 00 and 10 -- one history bit is enough for a correct prediction, since D outcome is equal to the outcome of the previous branch. Figure 4b shows the code modified by an architecture-aware compiler. Block 7 code and branch D are duplicated, to blocks 7-1 and 7-2, and branches D1 and D2: branch D1 is on the not taken path of branch A, and branch D2 is on the taken path. Now the D1 outcome is always 0, and the D2 outcome is equal to the branch C outcome (Table 1b). Since branches D1 and D2 are located at different addresses, they have separate predictor entries for the same branch histories, so both are correctly predicted by separate two-bit counters. In all cases we assume that this control flow is a part of a loop, and the predictor can be dynamically "trained."

Figure 4 Original (a) and optimized (b) code structure:

Branch D depends on two previously executed branches, and the branch predictor is global with one history bit.

Table 1 Branch outcome scenarios for original (a) and optimized code structure (b).

In the branch predictor with one global history bit, a two-bit saturation counter with starting state WT (Weakly Taken) mispredicts both shaded outcomes and with other starting states, mispredicts one of them.

(a) (b)

| Branch A | Branch B/C | Branch D |

|----------|------------|----------|

| 0        | 0          | 0        |

| 0        | 1          | 0        |

| 1        | 0          | 0        |

| 1        | 1          | 1        |

| Branch A | Branch B | Branch D1 |

|----------|----------|-----------|

| 0        | 0        | 0         |

| 0        | 1        | 0         |

| Branch A | Branch C | Branch D2 |

| 1        | 0        | 0         |

| 1        | 1        | 1         |

A similar optimization can be done for processors with a local branch predictor. Let us consider a processor with a local branch predictor using N bits of local branch history. The outcome of a loop condition branch can be correctly predicted if the loop does not have more than N iterations. Loops with more than N iterations can be unrolled, so the existing predictor can predict each unrolled loop. The compiler should perform loop unrolling if one such loop belongs to a critical portion of the code that executes frequently, and if it should be unrolled relatively few times. Figure 5a shows an example of code where the inner loop executes eight times and then exits, while the outer loop executes 1 million times. If this code executes on a processor with a local branch predictor using four bits of local history and two-bit saturation counters, the inner loop condition branch is mispredicted once in nine times, thus having 1 million branch mispredictions. After eight loop iterations, the two-bit counter for the history 1111 will be in the Strong Taken state. At the loop exit, four bits of local history are the same as in the previous four iterations (1111); hence the exit case uses the same BPT cell as others, and cannot be predicted correctly. An architecture-aware compiler can unroll the inner loop, and in this example twice is enough (Figure 5b). Both new loop branches can be correctly predicted with four bits of local history: now the 4bit branch history at the exit is unique with pattern 1111, so the exit case is mapped to the separate BPT entry. The number of lost execution cycles due to mispredicted branches is significantly reduced.

```

for (i=0;i<1000000;++i){

...

//original inner loop

for (j=0;j<8;++j){

...

}

...

}

(a)</pre>

for (i=0;i<1000000;++i){

...

//inner loop unrolled twice

for (j=0;j<4;++j){

...

}

...

}

...

}

(b)

```

Figure 5 Original (a) and optimized (b) C code:

### Original inner loop depends on its eight previous executions

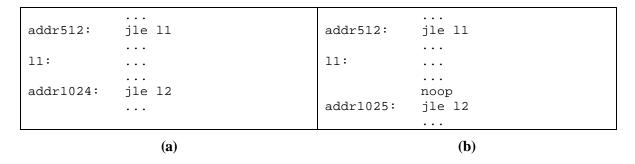

If the compiler is aware of predictor size and organization (i.e., the number of ways and sets and function used for the index), it can prevent branch interference in the critical portions of the code. For example, inserting a required number of noop instructions in the code can separate branches that map to the same predictor entry. Figure 6a shows an example of two branches mapping to the same branch target buffer entry, where it is assumed that branches at a distance of 512 bytes access the same BTB cell. If the BTB is always updated, both branch targets will be mispredicted, one always replacing the other. If both branches belong to a frequently executed portion of the code, an architecture-aware compiler can insert a *noop* instruction before one of the branches, thus preventing interference in the BTB (Figure 6b).

Figure 6 Original (a) and optimized (b) assembly code:

Branches mapping to the same predictor entry.

An architecture-aware compiler can encompass these mechanisms and other similar techniques. If applied to critical portions of the code, these optimizations can significantly increase performance. However, to be able to do so, the compiler needs to know the details about the branch predictor organization: the use of global, local, or both types of branch history; the number of history bits; and the BTB size and organization.

# **Experimental Environment**

This paper focuses on the widely used Intel P6 (Pentium III) and NetBurst (Pentium 4) architectures, although the proposed microbenchmarks can be applied, with some modifications, to other microprocessor architectures. For both P6 and NetBurst architectures, Intel sources [1], [5], [15] do not provide the exact description of the implemented branch predictors. Rather, they provide the exact number of BTB entries and several hints about program optimization that indicate some outcome predictor parameters. If a branch is not in the BTB, a static branch prediction is used, which means that the BTB and outcome predictor are coupled. The static prediction mechanism predicts backward conditional branches as taken, and forward branches as not taken. A return address stack of a known size predicts return addresses.

The P6 optimization reference manual states that the prediction algorithm includes pattern matching and can track up to the last 4 branch directions per branch address [15], most probably meaning that the P6 branch predictor has a local history component with 4 history bits. The P6 BTB has 512 entries.

In the NetBurst architecture implemented in the Pentium 4, Intel claims to use a new prediction algorithm, 33% better than in the P6. One of the assembly/compiler coding rules for Pentium 4 states that frequently executed loops with predictable number of iterations should be unrolled to reduce the number of iterations to 16 or fewer, and if the loop has N conditional branches, it should be unrolled so that the number of iterations is 16/N [1]. This rule indic ates that Pentium 4

uses a global outcome history, with probably 16 history bits, but the Intel sources never specifically say so.

Another interesting characteristic of the NetBurst architecture, tightly coupled with the branch prediction mechanism, is an execution trace cache [5], which stores and delivers sequences of traces, built from decoded instructions according to the execution flow. Intel sources explain that the trace cache and front-end translation engine have cooperating branch prediction hardware, so branch targets can be fetched from the trace cache, or in the case of a trace cache miss, from the second level cache or memory. The trace cache BTB is smaller (512 entries) compared to the front-end BTB (4K entries). It seems that both the trace cache and front-end share the same outcome predictor mechanism [15], but apart from trace cache size (12K micro-ops), and the trace cache line size (6 micro-ops), Intel does not disclose many details about its implementation. This work considers only the front-end BTB, and more experiments for trace cache component can be found in reference [16].

Both P6 and NetBurst architectures have several performance counters, able to measure various branch-related events, such as the number of retired branches, including unconditional branches, and the number of mispredicted branches, using event-based sampling. Since the number of branches depends on a particular microbenchmark and the number of times it executes, throughout the paper the MPR (Misprediction Ratio) is often used instead of the number of mispredicted branches. The MPR is the number of mispredicted branches divided by the total number of conditional branch instructions.

Although event-based sampling is not precise, it gives a good estimation of the number of events. A performance counter is configured to count one or more types of events and to generate an interrupt when it overflows. The counter is preset to a modulus value that will cause the overflow after a specific number of events have been counted. In this research the Intel VTune Performance Analyzer version 5.0 was used for configuration and access of performance counters. Performance counters on most non-Intel architectures, as well as Intel processors, can be accessed

by using the freeware PAPI tool (Performance Application Programming Interface), developed at the University of Tennessee [8].

All test benchmarks are compiled using a Microsoft Visual Studio 6.0 C compiler, with disabled optimization, preventing the compiler optimizations from changing the order and number of conditional branches. For experiments with a relatively large number of branches, we have also developed programs to generate benchmarks to our specifications in assembly. In order to get reliable values of performance counters, the execution time of the monitored code must be significantly larger than the execution of the interrupt service routine. Therefore, the test code is placed within a loop executing a relatively large number of times.

# **Experiment Flow**

The experiment flow consists of two groups of experiments targeting the branch target buffer and the outcome predictor. Branch target buffer experiments uncover the BTB organization and address bits used as an index, and outcome predictor experiments determine the existence of local and global prediction components, and the length of the corresponding history registers.

### **BTB** Experiments

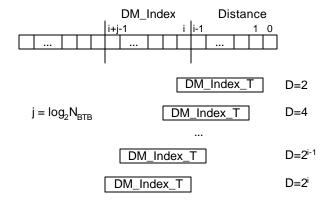

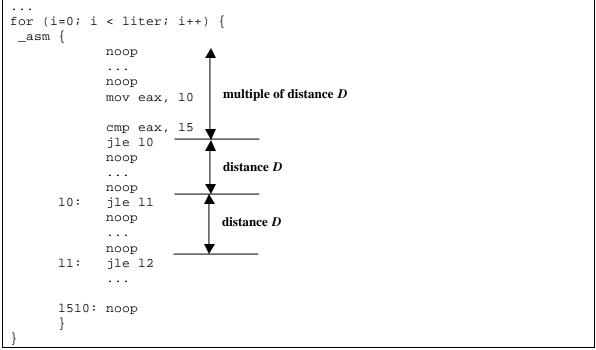

The Intel documentation for P6 does not describe BTB organization: whether it is direct-mapped or set-associative, and the degree of associativity. One way to determine the number of ways and the address bits used as the BTB index is to run a set of microbenchmarks varying the address distance D between branch instructions (Figure 7). Each microbenchmark has  $N_{BTB} - 1$  conditional branches in a loop, which makes a total of  $N_{BTB}$  conditional branches, where  $N_{BTB}$  is the number of BTB entries. These conditional branches are always taken, so they are mispredicted by the static algorithm if not present in the BTB. Figure 8 shows the fragment of the microbenchmark code.

For a "fitting" distance  $D_F$ , when all considered branches can fit in the BTB, the number of mispredictions is close to zero, i.e., the performance counter counts only a negligible number of mispredictions. If there is only one distance  $D_F$ , then the BTB is direct-mapped, and address bits used as the BTB index are Addr[i+j+1:i] (Figure 7). If there are exactly two distances  $D_F$ , the BTB is 2-way set-associative, and bits used as index are Addr[i+j+2:i]. Similarly, if there are exactly three distances  $D_F$ , the BTB is 4-way set-associative. In general, if there are m "fitting" distances, the BTB is  $2^{m-1}$ -way set associative, and the index bits are Addr[i+j+m:i].

Figure 7 BTB size and organization: varying the distance.

Figure 8 Benchmark for testing BTB organization.

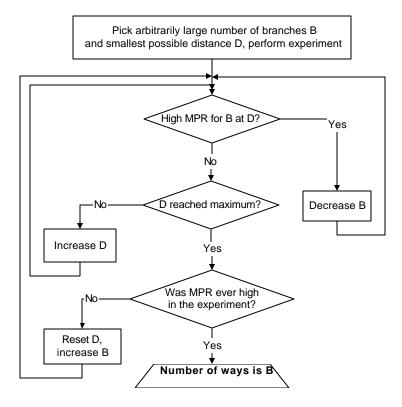

There is one exception to this experiment, and that is the unlikely border case in which loworder address bits are used as the index, i.e., Addr[ i-1 :0]. For any degree of associativity, this BTB will have only one "fitting" distance  $D_F=1$ . In this case, an additional experiment is necessary to establish the number of BTB ways. Instead of finding the number of branches that would fill the whole BTB, this additional experiment finds the number of branches that fill a BTB set, and a distance  $D_s$  such that those branches map into the same set. If there are more branches than ways mapping into the same set, the misprediction rate will be high. The same number of branches at some other distance might also produce a high MPR, if there are sets where the number of competing branches is larger than the number of the BTB ways. For example, 16 branches mapping into a 4-way set will have a high MPR, as well as 16 branches mapping into two 4-way sets. If the number of branches is equal or less than the number of ways, they do not collide at any distance. The corresponding microbenchmark is similar to the one described for the previous experiment (Figure 8), but in general, it requires a larger number of runs to establish correct BTB organization, since both the number of branches fitting in the set and the branch distance must be varied. Figure 9 shows the search process for the correct number of BTB ways. The algorithm first picks an arbitrarily large number of branches and sets them at the smallest possible distance D. If the MPR is low, the distance is increased and the experiment is repeated. When a high MPR is reached, it means that B branches collide in the same set, and the number of branches is decreased. The process stops when the maximum distance is reached, unless the number of branches picked at the beginning is smaller than the number of ways. In this case, the MPR is low throughout the series of experiments, and the number of branches B should be increased.

Figure 9 Searching the number of branches that fill a cache set

A variation of the microbenchmark shown in Figure 8 can be used to verify the assumption about the number of BTB entries, by increasing the number of branches for the "fitting" distances. For example, if the actual number of BTB entries is twice as large as the assumed one, and the previous experiments have found m distances  $D_F$ , the set of experiments with the actual number of entries should find m-1 such distances; i.e., the BTB would be  $2^{m-2}$ -way set associative. In general, if the actual number of BTB entries is  $2^n$  times greater than the assumed one, the experiments should find m-n "fitting" distances. If the experiments with a larger number of conditional branches do not find any such distance, the assumption about the size is correct.

## **Outcome Predictor Experiments**

The set of experiments for uncovering the characteristics of outcome predictor component (Figure 10) is devised in such a way that all the branches but a few are easily predictable; i.e., those few "spy" branches generate the misprediction rate for the whole microbenchmark. The microbenchmarks should be carefully tuned to avoid interference between different branches in the

branch predictor. Since the BTB organization is known from the previous set of experiments, it is possible to check the assembly code for branch interference and insert dummy instructions if necessary.

**Step 1.** This step determines the maximum length of a local history pattern that the predictor can correctly predict, for just one branch in the loop, i.e., the "spy" branch. The loop condition branch has just one outcome not taken, when it exits; otherwise it is taken. After enough iterations, misprediction due to this branch is negligible. For the "spy" branch, different repeating local history patterns of length *LSpy* can be used; however, the simplest pattern has all outcomes the same but the last one. If "1" means that the branch is taken, and "0" not taken, such local history patterns are 1111...110 and 0000...001.

Figure 11a shows the code for the Step 1 experiment, and Figure 11b shows the fragment of the corresponding assembly code for Intel x86 architecture, when pattern length LSpy=4. Note that the "spy" branch if((i%4)==0) is compiled as  $jne(jump\ short\ if\ not\ equal)$ , so the local history pattern for this branch is 1110. The fragment does not show the loop, which is compiled as the combination of instructions  $jae(jump\ short\ if\ above\ or\ equal)$  at the beginning of the loop and unconditional jmp at the end, so the jae outcome is 0 until the loop exit.

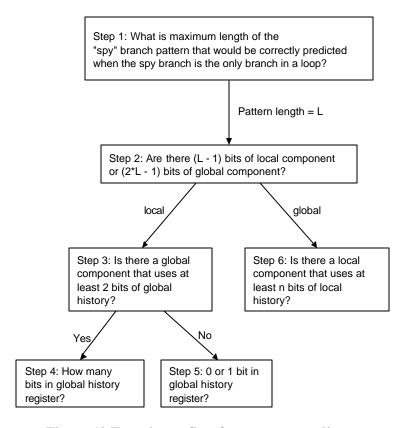

Figure 10 Experiment flow for outcome predictor.

```

void main(void) {

; Line 6

int long unsigned i;

0002e

eax,DWORD PTR _i$[ebp]

mov

00031

int a=1;

xor

edx, edx

int long unsigned liter = 10000000;

00033

mov

ecx, 4

00038

div

ecx

test edx, edx

for (i=0; i<liter; ++i){

0003a

if ((i%LSpy) == 0) a= 0; //spy branch

0003c

jne

SHORT $L38

0003e

DWORD PTR _a$[ebp], 0

mov

$L38:

```

Figure 11 Step 1 microbenchmark and the assembly fragment, when LSpy = 4.

**(b)**

(a)

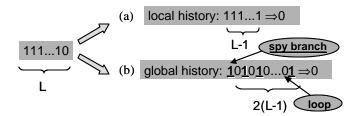

The MPR is low for all LSpy pattern lengths up to a certain number L, and then the outcome predictor is not able to predict the last outcome of the "spy" branch. That is, for each pattern of length LSpy>L, the "spy" branch is mispredicted once in LSpy times. However, this experiment does not tell whether the predictor has a local prediction component with history registers of length L-1, or a global predictor component with a history register of length 2\*(L-1). Two cases must be considered, as depicted in Figure 12:

- (a) The outcome predictor has a local history component, so any local pattern of the length L can be correctly predicted, including the "spy" pattern.

- (b) The outcome predictor has a global history component, so the local history pattern 11...10 of the "spy" branch with L-l 1's is correctly predicted, but by using the global history of previous 2\*(L-l) branches. Since the microbenchmark has just the loop condition and the "spy" branch, all predictions are correct if all relevant local history fits into the global history register. For example, just before execution of the "spy" branch with 0 outcome, the content of the global history register is  $\underline{101010...10}$ , where underlined and bolded 1's are outcomes of the "spy" branch, and 0's are the outcomes of the loop condition branch.

Figure 12 Two possible cases for maximum predictable pattern length L in Step 1

Step 2. Step 2 verifies which one of these two hypotheses matches the predictor under test. If the conditional branch in the loop is preceded by 2\*(L-1) "dummy" conditional branches, having always the same outcome, then no local "spy" history is present in the global history register when the "spy" branch prediction is generated. One example for the "dummy" branch is if(i<0) a=1 (Figure 13). If the MPR still stays low, the correct hypothesis is (a); i.e., the predictor has a local history component. The experiment flow proceeds to Step 3, which determines whether the outcome predictor also has a global history component. If the MPR increases, the correct hypothesis is (b); i.e., the predictor has a global history component. In this case, the experiment flow proceeds to Step 6 to determine whether the outcome predictor also has a local history component.

Figure 13 Step 2 microbenchmark.

```

void main(void) {

int a,b,c;

int long unsigned i;

for (i=1;i<=10000000;++i) {

if ((i%L1) == 0) a=1;

else a=0;

if ((i%L2) == 0) b=1;

else b=0;

if ((a*b) == 1) c=1; // spy branch

}

}</pre>

```

Figure 14 Step 3 microbenchmark.

**Step 3.** The Step 3 microbenchmark has three conditional branches in a loop, where the first two have predictable patterns 11...10 of different pattern lengths LI and L2, such that LI, L2 = L, and the smallest common denominator for (LI, L2) is greater then L. For example, if L=4, the values for LI, L2 may be LI=3 and L2=2. The third branch, the "spy," is correlated with the first two, and is not taken when both previous branches are not taken (Figure 14). The pattern of the third branch is 11...10, and its length is greater than L, so it cannot be predicted by local component, while both the first and second branch will be correctly predicted. That is, the local predictor can correctly predict all 1 outcomes of the "spy" branch, but a global predictor with at least two history bits is needed for a correct prediction of the "spy" 0 outcome. Hence, if the MPR is low, the number of global history bits is equal to or greater than two, and the next step is Step 4. Otherwise, there is no global component or there is just one bit of global history, and the next step is Step 5.

**Step 4.** This step determines the length of the global history register. The simplest way is to insert "dummy" conditional branches (e.g., pattern 111...11) before the "spy" conditional branch. The "spy" branch is not predicted correctly if the number of "dummy" branches is greater than the number of *global history bits* -2, so the number of global history bits is determined by varying the number of "dummy" branches.

```

void main(void) {

int a,b,c;

int long unsigned i;

for (i=1;i<=10000000;++i) {

if ((i%L1) == 0) a=1;

else a=0;

if ((i%L2) == 0) b=1;

else b=0;

if (i<0) a=1; //dummy branch

...

if (i<0) a=1; //dummy branch

if ((a*b) == 1) c=1;

}

</pre>

```

Figure 15 Step 4 microbenchmark.

**Step 5.** The Step 5 microbenchmark has just two conditional branches in the loop, where the first one has the local history pattern 111...110 of a length L3>L, and the second one has the same outcome as the first, as shown in Figure 16. Since it is known from Step 3 that the predictor does not use more than one global history bit, the first conditional branch is mispredicted once in every L3 times. If there is no global component at all, the second branch is also mispredicted once in L3 times, while it is always predicted correctly if there is a one-bit global history component. The number of mispredictions in this experiment determines the existence of a one-bit global history predictor.

```

void main(void) {

int a;

int long unsigned i;

int long unsigned liter = 10000000;

for (i=1;i<=liter;++i) {

if ((i%L3) == 0) a=1; //L3 > L

if ((i%L3) == 0) a=1; //spy branch

}

}

```

Figure 16 Step 5 microbenchmark.

**Step 6.** The presence of a global component with 2\*(L-1) history bits is proved in the previous steps, and this step probes for the presence of a local component. The Step 6 microbenchmark has 2\*(L-1) "dummy" branches (Figure 17) and varies the pattern length LSpy of the "spy" branch. If the MPR is low for some LSpy, there is an equivalent local component with at least LSpy-1 history bits. Depending on the decision mechanism, there could be more local history bits, so further experiments might be needed. This is outside the scope of this paper.

```

void main(void) {

int long unsigned i;

int a=1;

int long unsigned liter = 10000000;

for (i=0; i<liter; ++i) {

if (i<0) a=1;//dummy branch #1

...

if (i<0) a=1;//dummy branch #2*(L-1)

if ((i%LSpy) == 0) a=0; //spy branch

}

}</pre>

```

Figure 17 Step 6 microbenchmark.

## **Results**

### BTB Results

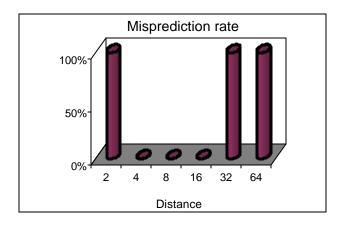

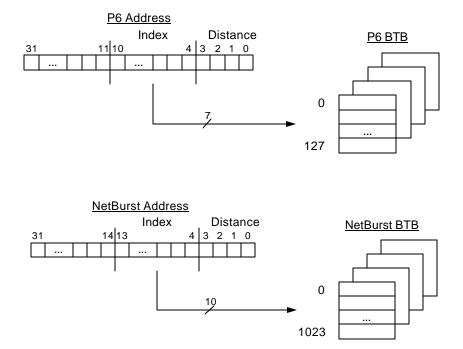

For the P6 architecture ( $N_{BTB}$ =512) the MPR is close to 0% when the distance between addresses of subsequent branches is 4, 8, or 16; and it is close to 100% for other distances (Figure 18). Since three different distances produce the low MPR, the P6 architecture has the branch target buffer organized in 4 ways, 128 sets. The address bits 4-10 are used as the set index.

Figure 18 Misprediction rate for  $N_{\text{BTB}}$  conditional branches, varying distance.

This result can be also obtained by trying to map B branches in the same set, varying the distance between them and the number of branches (Table 2). It can be seen that 16 branches collide in the same set when at a distance of 16, and 8 branches collide at a distance of 2048, while 4 branches do not collide at any distance. Hence, the conclusion is the same: the P6 architecture has 4 cache ways (Figure 19).

Table 2 P6 branch mispredictions when trying to map B branches in the same set.

| Iterations: 1M, B = 16 |                       |  |  |

|------------------------|-----------------------|--|--|

| Distance               | Mispredicted branches |  |  |

| 512                    | 1,953                 |  |  |

| 1024                   | 14,938,664            |  |  |

| Iterations: 1M, B = 8  |                       |  |  |

| Distance               | Mispredicted branches |  |  |

| 1024                   | 2,520                 |  |  |

| 2048                   | 6,927,480             |  |  |

|                        | Iterations: 1M, B = 4 |  |  |

| Distance               | Mispredicted branches |  |  |

| 2048                   | 2,400                 |  |  |

| 4096                   | 4,097                 |  |  |

Finally, to verify whether the correctness of the assumption about BTB size, the different distance experiment is performed with twice as many branches. Table 3 shows results for the P6 architecture for 1024 branches. The distances that produced the low MPR when the number of branches was 512 now produce an MPR close to 100%. Hence, the actual number of BTB entries is 512.

Table 3 P6 branch mispredictions when the total number of branches is  $2*N_{BTB}$ .

| Iter. $1M, B = 1024$            |               |  |  |

|---------------------------------|---------------|--|--|

| Distance Mis predicted branches |               |  |  |

| 4                               | 1,017,750,000 |  |  |

| 8                               | 1,016,900,000 |  |  |

| 16                              | 1,020,700,000 |  |  |

Figure 19 P6 and NetBurst BTB size and organization.

The results are similar for NetBurst architecture ( $N_{BTB-FE}$ =4096); i.e., the MPR is close to 0% when the distance between addresses of subsequent branches is 4, 8, or 16; and it is close to 100%

for other distances. Therefore, the front-end BTB has 4 ways and 1024 sets, while bits 4-13 are used as the set index (Figure 19).

### Outcome Predictor Results - P6 Architecture

**Step 1.** Table 4 shows the results of the Step 1 experiment (Figure 11). The maximum length of a correctly predicted pattern is 5, since the spy branch with a pattern of length 6 is mispredicted once in each 6 times (10,000,000/6 = 1,666,666), which is close to the number of mispredicted branches shown in Table 4. This result can be caused by a local predictor component that uses 4 bits of local history, or a global component that uses 8 global history bits.

Table 4 Results of the Step 1 experiment.

|       | P6                |                       | NetBurst          |                       |

|-------|-------------------|-----------------------|-------------------|-----------------------|

| Iter. | Pattern<br>length | Mispredicted branches | Pattern<br>length | Mispredicted branches |

| 10 M  | 4                 | 420                   | 5                 | 987                   |

|       | 5                 | 432                   | 6                 | 973                   |

|       | 6                 | 1,545,480             | 7                 | 957                   |

|       |                   |                       | 8                 | 1,256                 |

|       |                   |                       | 9                 | 918                   |

|       |                   |                       | 10                | 964,830               |

- **Step 2.** The microbenchmark has eight "dummy" conditional branches before the "spy" branch. Since the MPR is still close to 0 for longer global history pattern, the P6 architecture uses a local branch history of length 4.

- **Step 3.** The microbenchmark has three conditional branches in a loop, where the first two have patterns 11...10 of length 5 and 2, and hence are predictable by the local predictor component. The outcome of the third branch is correlated with the previous two. Since it has a pattern 11...10 of length 10, it is not predictable by the local component with 4 history bits. The MPR is about 10%, which means that the third branch is mispredicted once in each 10 times, when its outcome is 0.

Hence, the P6 architecture does not use a global history pattern of length greater than or equal to two.

**Step 4.** The Step 4 experiment is a 10 million iteration loop, with two conditional branches. The first branch has a pattern 111110 of length 6, so it is not predictable by the local component, and the second branch is correlated with it by having the same outcome. The result is about 3 million mispredicted branches, so both conditional branches are mispredicted once in six times. Therefore, the P6 architecture does not include global prediction component.

#### Outcome Predictor Results - NetBurst Architecture

**Step 1.** Table 4 shows the results of the Step 1 experiment: the maximum length of a correctly predicted pattern is 9, since the "spy" branch with a pattern of length 10 is mispredicted once in each 10 times -- about 1 million of mispredictions. These results can be explained by either an 8-bit local history register or a 16-bit global history register.

**Step 2.** The microbenchmark has 16 "dummy" branches before the "spy" branch with a local pattern of length 9. The measured MPR is about 10%; i.e., the "spy" branch is mispredicted once in 9 times. Therefore, the Step 1 result is caused by a global component that uses 16 global history bits.

**Step 6.** After several runs of different Step 6 experiments, the first conclusion might be that the NetBurst architecture uses one local history bit for prediction, since a pattern length 2 is predicted correctly (Table 5). Because this architecture includes the trace cache, an additional experiment is needed, with the structure from the Step 6 experiment repeated 10 times in sequence: 16 "dummy" branches, and one "spy" branch with a local history pattern of length 2. The "spy" branches have an MPR of about 50%, which is expected for the outcome predictor without any local component. Hence, the low MPR in Step 6 with pattern length 2 is due to the trace cache, since it is able to store the sequence "loop, 16 dummy branches, spy taken, loop, 16 dummy branches, spy not taken" as one continuous trace.

Table 5 Results of the Step 6 experiment.

| Iter. | Pattern length | Mispredicted spy branches |

|-------|----------------|---------------------------|

| 10 M  | 2              | 0%                        |

|       | 3              | 33%                       |

|       | 4              | 25%                       |

|       | 5              | 20%                       |

## Conclusion

The continual growth in complexity of processor features, such as wide-issue, deep pipelining, branch predictor, multiple levels of cache hierarchy, etc., puts more demand on code optimizations to achieve optimal performance. While current compilers depend on a programmer to specify for which architecture to optimize the code, and to manually adjust the code to a specific architecture, future compilers should be more architecture-aware and be able to discover the relevant characteristics of underlying architecture without a programmer's input. Consequently, the burden of optimization for different architectures will shift from a program developer to the compiler, and optimization will become more automated. Unfortunately, not all architecture details are publicly available, so the optimization process cannot rely solely on information given in manufacturers' manuals. To determine architecture intricacies, an architecture-aware compiler should run a set of carefully tuned microbenchmarks.

This paper presents a systematic approach to uncovering the basic characteristics of branch predictors. The proposed experiment flow encompasses microbenchmarks aimed at determining relevant branch predictor parameters -- namely, branch target buffer associativity and address bits used as index, the existence of local and global branch history component, and the number of corresponding history bits. These parameters can be used for automatic or manual code optimization. The proposed experiments can also be applied during the verification phase of processor design, and used as a starting point for comparison in future predictor research. Last, the

experiments have educational value, providing better understanding of branch predictor mechanisms. Although the proposed approach is demonstrated for Intel P6 and NetBurst architectures, with minor modifications, it can also be used for other architectures.

### Acknowledgments

The authors are grateful to the anonymous referees for their insights and suggestions for strengthening this paper. This work has been partially supported by the SED of the AMCOM.

## References

- 1. *IA-32 Intel*® *Architecture Optimization Reference Manual*, Intel, http://www.intel.com/design/pentium4/manuals/248966.htm [July 2003].

- 2. Coleman CL, Davidson JW. Automatic memory hierarchy characterization. In *Proceedings of the ISPASS 2001*; 103 –110.

- 3. Saavedra-Barrera R. CPU Performance Evaluation and Execution Time Prediction Using Narrow Spectrum Benchmarking. *PhD Thesis*, U.C. Berkeley, Computer Science Div., 1992.

- 4. Hennessy J, Patterson D. *Computer Architecture: A Quantitative Approach*. Morgan Kaufmann Publishers, San Mateo, CA, 2003.

- 5. Hinton G et al. The Microarchitecture of the Pentium® 4 Processor. *Intel Technology Journal*, (1<sup>st</sup> quarter 2001), <a href="http://www.intel.com/technology/itj/q12001.htm">http://www.intel.com/technology/itj/q12001.htm</a> [July 2003].

- 6. Sprangle E, Carmean D. Increasing Processor Performance by Implementing Deeper Pipelines. In *Proceedings of the 29th ISCA*, 2002; 25-34.

- 7. Intel VTune<sup>TM</sup> Performance Analyzer, <u>www.intel.com/software/products/vtune/</u> [August 2002].

- 8. London K et al. End-user Tools for Application Performance Analysis Using Hardware Counters. In *Proceedings of the International Conference on Parallel and Distributed Computing Systems*, 2001.

- 9. Smith JE. A study of Branch Prediction Strategies. In *Proceedings of the 8th ISCA*, 1981; 135–148.

- 10. Yeh TY, Patt YN. Two Level Adaptive Training Branch Prediction. In *Proceedings of the Micro-24*, 1991, pp. 51-61.

- 11. Pan ST, So K, Rahmeh JT. Improving the Accuracy of Dynamic Branch Prediction Using Branch Correlation. In *Proceedings of the ASPLOS V*, 1992; 76-84.

- 12. Evers M, Chang PY, Patt YN. Using Hybrid Branch Prediction to Improve Branch Prediction Accuracy in the Presence of Context Switches. In *Proceedings of the 23rd ISCA*, 1996; 3–10.

- 13. Nair R. Dynamic Path-Based Branch Corelation. In *Proceedings of the Micro-28*, 1995; 15-23.

- 14. *UltraSPARC User's Manual*, Sun Microelectronics, <a href="http://www.sun.com/processors/manuals/802-7220-02.pdf">http://www.sun.com/processors/manuals/802-7220-02.pdf</a> [July 2003].

- 15. Intel® Architecture Software Optimization Reference Manual, Intel, http://www.intel.com/design/PentiumIII/manuals/ [December 2001].

- 16. Milenkovic M, Milenkovic A, Kulick J. Demystifying Intel Branch Predictors. In *Proceedings of the Workshop on Duplicating, Deconstructing, and Debunking*, 2002; 52-61.