# TECHNIQUES FOR CAPTURING AND FILTERING DATA VALUE TRACES IN MULTICORES

by

#### MOUNIKA PONUGOTI

#### A THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Engineering in

The Department of Electrical & Computer Engineering to

The School of Graduate Studies of

The University of Alabama in Huntsville

HUNTSVILLE, ALABAMA

2016

| In presenting this thesis in partial fulfillr | nent of the requirements for a master's de-  |

|-----------------------------------------------|----------------------------------------------|

| gree from The University of Alabama in F      | Huntsville, I agree that the Library of this |

| University shall make it freely available t   | for inspection. I further agree that permis- |

| sion for extensive copying for scholarly pu   | arposes may be granted by my advisor or, in  |

| his/her absence, by the Chair of the Depa     | rtment or the Dean of the School of Gradu-   |

| ate Studies. It is also understood that due   | e recognition shall be given to me and to    |

| The University of Alabama in Huntsville       | in any scholarly use which may be made of    |

| any material in this thesis.                  |                                              |

|                                               |                                              |

|                                               |                                              |

|                                               |                                              |

| (student signature)                           | (date)                                       |

|                                               |                                              |

## THESIS APPROVAL FORM

Submitted by Mounika Ponugoti in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering and accepted on behalf of the Faculty of the School of Graduate Studies by the thesis committee.

We, the undersigned members of the Graduate Faculty of The University of Alabama in Huntsville, certify that we have advised and/or supervised the candidate on the work described in this thesis. We further certify that we have reviewed the thesis manuscript and approve it in partial fulfillment of the requirements for the degree of Master of Science in Engineering in Computer Engineering.

|                             |        | Committee Chair  |

|-----------------------------|--------|------------------|

| (Dr. Aleksandar Milenkovic) | (date) |                  |

| (Dr. Rhonda Gaede)          |        |                  |

| (Dr. Earl Wells)            |        |                  |

|                             |        |                  |

| (Dr. Ravi Gorur)            | (date) | Department Chair |

| (Dr. Shankar Mahalingam)    | (date) | College Dean     |

|                             |        | Graduate Dean    |

| (Dr. David Berkowitz)       | (date) |                  |

#### ABSTRACT

The School of Graduate Studies

The University of Alabama in Huntsville

Degree Master of Science in Engineering

College/Dept. Engineering/Electrical & Computer Engineering Name of Candidate Mounika Ponugoti Techniques for Capturing and Filtering Data Value Traces in Multicores Software testing and debugging represent critical aspects of the design of modern multicore-based embedded computer systems due to growing hardware and software complexity, increased integration, and tightening time-to-market. The existing tracing and debugging techniques offer limited visibility of the system under test or rely on large on-chip buffers and wide trace ports that increase the system cost. This thesis introduces three hardware/software techniques for capturing and filtering load data value traces in multicores. They track memory read accesses in data caches on the target platform and simulate their behavior in the software debugger to significantly reduce the number of trace events that need to be streamed out of the target platform. Our experimental evaluation explores the effectiveness of the proposed techniques by measuring the trace port bandwidth as a function of system parameters. The results show that the proposed techniques significantly reduce the total trace port bandwidth. The improvements relative to the existing Nexus-like load data value tracing range from 10 to 60 times for a single core and from 19 to 74 times for an octa core. Abstract Approval: Committee Chair Department Chair

Graduate Dean

#### ACKNOWLEDGMENTS

The work presented in this thesis would have been incomplete without thanking people who helped me directly and indirectly. First, I would like to express my sincere gratitude to my advisor Dr. Aleksandar Milenkovic for his unlimited support at every stage of this work, and for supporting me as a graduate research assistant. He inspired me personally and professionally with his patience and his interest towards student learning. This work was supported in part by US National Science Foundation (NSF) grant CNS-1217470.

I would like to thank Mr. Amrish K. Tewar who developed TmTrace module that I used in my research. I would like to thank Mr. Tewar and Mr. Armen Dzhagaryan for helping me to get started in the laboratory.

I would like to thank Dr. Rhonda Gaede and Dr. Earl Wells for serving on my committee. I would also like to thank all the professors and staff members who helped me during my time at the University of Alabama in Huntsville.

Also, I would like to thank Srinivas R. Mynampally and his family for giving me great support since the first day of my arrival to the United States.

Finally, I would like to express my deepest gratitude to my parents, Bhagavanth Rao and Vimala, for their unconditional love and support. I would like to thank my life partner, Vamshi Krishna, for providing continuous support and encouragement for higher studies.

# TABLE OF CONTENTS

| Cont |        | Pag                          | _          |

|------|--------|------------------------------|------------|

|      |        | GURESi                       |            |

| LIST | OF TA  | ABLESx                       | ii         |

| CHA  | PTER   | 1                            | . 1        |

| 1.1  | Bao    | ekground and Motivation      | . 1        |

| 1.2  | Sco    | ppe of this Thesis           | . 2        |

| 1.3  | Con    | ntributions                  | . 4        |

| 1.4  | Ou     | tline                        | . 5        |

| CHA  | PTER : | 2                            | 6          |

| 2.1  | Tra    | acing in Embedded Multicores | 6          |

| 2.2  | Me     | mory Data Traces             | . 9        |

| 2.3  | Rel    | ated Work                    | 11         |

| CHA  | PTER   | 31                           | 15         |

| 3.1  | mlv    | vCFiat                       | 15         |

| 3.2  | mc     | $^2RT$                       | 22         |

| 3.3  | mc     | $^2RFiat$                    | 33         |

| CHA  | PTER - | 4                            | <b>4</b> 5 |

| 4.1  | Sof    | tware Timed Trace Generator  | 16         |

| 4.2  | mlv    | vCFiat Simulator             | 17         |

| 4    | 1.2.1  | Implementation Details       | 51         |

| 4    | 1.2.2  | Verification Details         | 54         |

| 4.3  | mc     | $^2\!RT$ Simulator 6         | 31         |

| 4    | 4.3.1  | Implementation Details       | 33         |

| 4    | 1.3.2  | Verification Details         | 35         |

| 1 1  | l mc   | <sup>2</sup> RFiat Simulator | 73         |

| 4.4.  | .1    | Implementation Details                                         | 73    |

|-------|-------|----------------------------------------------------------------|-------|

| 4.4.  | .2    | Verification Details                                           | 75    |

| 4.5   | Sof   | tware to Hardware Trace Translation                            | 84    |

| 4.6   | Exp   | perimental Environment                                         | 88    |

| 4.6.  | .1    | Experimental Setup                                             | 88    |

| 4.6.  | .2    | Benchmarks                                                     | 90    |

| 4.6.  | .3    | Experiments                                                    | 92    |

| 4.6.  | .4    | Granularity Study                                              | 93    |

| 4.6.  | .5    | Variable Encoding                                              | 95    |

| CHAPT | ER 8  | 5                                                              | 99    |

| 5.1   | Tra   | ce Port Bandwidth for Load Data Value Traces                   | 99    |

| 5.1.  | .1    | NX_b                                                           | 99    |

| 5.1.  | .2    | mlvCFiat                                                       | . 104 |

| 5.1.  | .3    | $mc^2RT$                                                       | . 111 |

| 5.1.  | .4    | $mc^2RFiat$                                                    | . 117 |

| 5.2   | Dyı   | namic Trace Port Bandwidth Analysis for Load Data Value Traces | . 124 |

| 5.3   | Put   | ting It All Together                                           | . 126 |

| СНАРТ | ER 6  | 3                                                              | . 130 |

| סמממס | TINIC | TEC                                                            | 199   |

# LIST OF FIGURES

| Figure                                                                                   |

|------------------------------------------------------------------------------------------|

| Figure 2.1 Debugging and tracing in multicores: a detailed view                          |

| Figure 2.2. Memory read trace: an example a) C program b) equivalent x86                 |

| assembly c) memory read flow traces                                                      |

| Figure 3.1 A system view of mlvCFiat                                                     |

| Figure 3.2. $mlvCFiat$ structures for core $i$                                           |

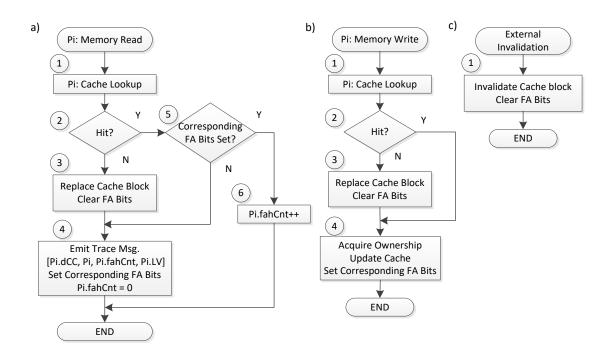

| Figure 3.3 $\mathit{mlvCFiat}$ operations on the target core $i$ for a) memory reads, b) |

| memory writes, and c) external invalidations                                             |

| Figure 3.4 $mlvCFiat$ operations in the software debugger on core $i$ for a)             |

| memory reads, b) memory writes, and c) external invalidations                            |

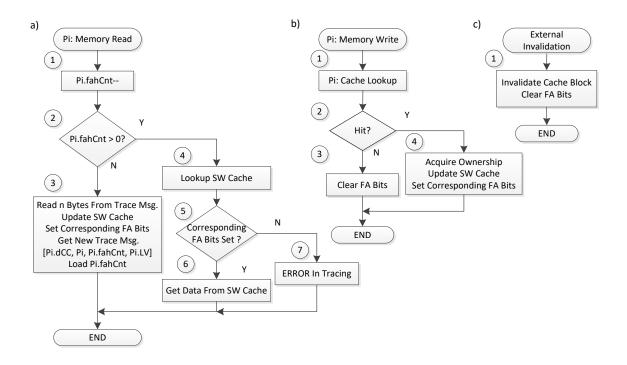

| Figure 3.5 A system view of $mc^2RT$                                                     |

| Figure 3.6 $mc^2RT$ structures for core $i$                                              |

| Figure 3.7 $mc^2RT$ operation on the target core $i$ for memory reads                    |

| Figure 3.8 Coherent Read Transaction in $mc^2RT$ on the target core $i$                  |

| Figure 3.9 $mc^2RT$ operation on the target core $i$ for memory writes 30                |

| Figure 3.10 Coherent Read and Invalidate in $mc^2RT$ on target core $i$ 31               |

| Figure 3.11 Coherent Invalidate in $mc^2RT$ on target core $i$                           |

| Figure 3.12 $mc^2RT$ operation in the software debugger on core $i$ for a)               |

| memory reads b) memory writes                                                            |

| Figure 3.13 A system view of $mc^2RFiat$                                                 |

| Figure 3.14 $mc^2RFiat$ structures for core $i$                                          |

| Figure 3.15 $mc^2RFiat$ operation on the target core i for memory reads 38               |

| Figure 3.16 Coherent Read Transaction in $\mathit{mc}^2RFiat$ on the target core $i$ | 39   |

|--------------------------------------------------------------------------------------|------|

| Figure 3.17 $mc^2RFiat$ operation on the target core $i$ for memory writes           | 41   |

| Figure 3.18 Coherent Read and Invalidate in $mc^2RFiat$ on the target core           | i 42 |

| Figure 3.19 Coherent Invalidate in $mc^2RFiat$ on the target core $i$                | 42   |

| Figure 3.20 $mc^2RFiat$ operation in the software debugger on core $i$ for a)        |      |

| memory reads, and b) memory writes                                                   | 44   |

| Figure 4.1 Experiment flow to create hardware traces                                 | 46   |

| Figure 4.2 Trace messages generated for memory reads and writes                      | 47   |

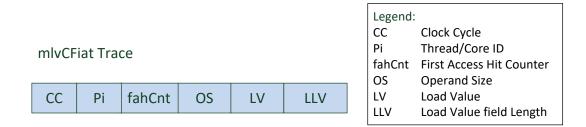

| Figure 4.3 mlvCFiat trace descriptor format                                          | 49   |

| Figure 4.4 mlvCFiat simulator statistics example                                     | 50   |

| Figure 4.5 mlvCFiat simulator functional flow                                        | 53   |

| Figure 4.6 Testing mlvCFiat: single cache block access                               | 57   |

| Figure 4.7 Testing <i>mlvCFiat</i> : multi cache block access                        | 61   |

| Figure 4.8 $mc^2RT$ trace descriptor format                                          | 62   |

| Figure 4.9 $mc^2RT$ simulator statistics example                                     | 63   |

| Figure 4.10 Testing $mc^2RT$ : single cache block access                             | 69   |

| Figure 4.11 Testing $mc^2RT$ : multi cache block access                              | 72   |

| Figure 4.12 Testing $mc^2RFiat$ : single cache block access                          | 80   |

| Figure 4.13 Testing $mc^2RFiat$ : multi-cache block access                           | 84   |

| Figure 4.14 Formats of trace messages for $NX_b$ , $CF_b$ , $CF_e$ , $RT_b$ , $RT_e$ | ,    |

| RF_b and RF_e                                                                        | 87   |

| Figure 4.15 Multicore model in Mult2Sim                                              | 89   |

| Figure 4.16 Normalized trace port bandwidth as a function of first-access            |      |

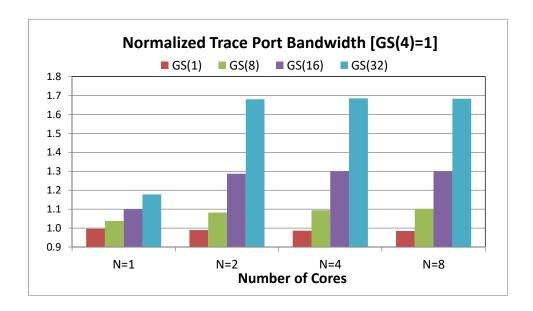

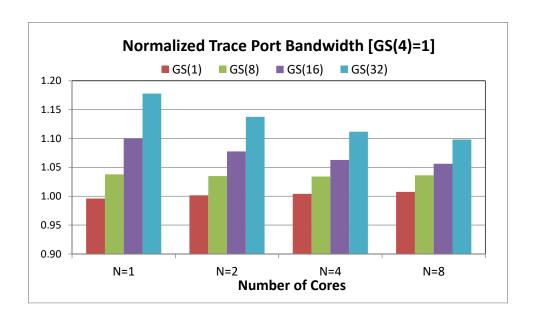

| granularity for mlvCFiat                                                             | 94   |

| Figure 4.17 Normalized trace port bandwidth as a function of first-access          |

|------------------------------------------------------------------------------------|

| granularity for $mc^2RFiat$                                                        |

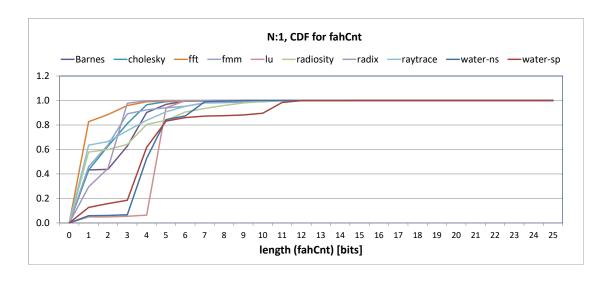

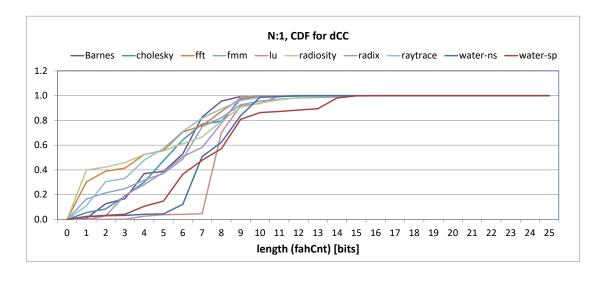

| Figure 4.18 CDF of the minimum length for fahCnt for mlvCFiat96                    |

| Figure 4.19 CDF of the minimum length for $dCC$ for $mlvCFiat$                     |

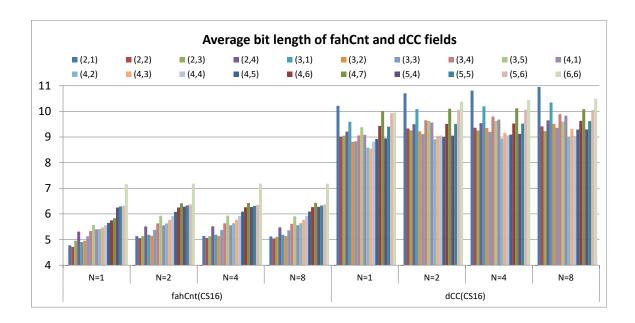

| Figure 4.20 Average $fahCnt$ and $dCC$ fields as a function of chunk sizes for     |

| mlvCFiat                                                                           |

| Figure 5.1 Breakdown of trace port bandwidth for $NX_b$ for Splash2                |

| benchmarks                                                                         |

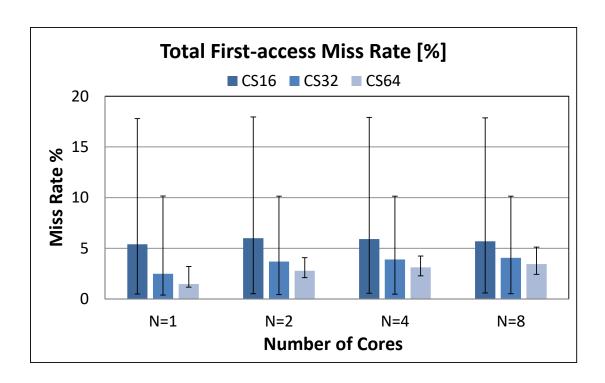

| Figure 5.2 First Access Miss Rate for $mlvCFiat$ for Splash2 benchmarks 106        |

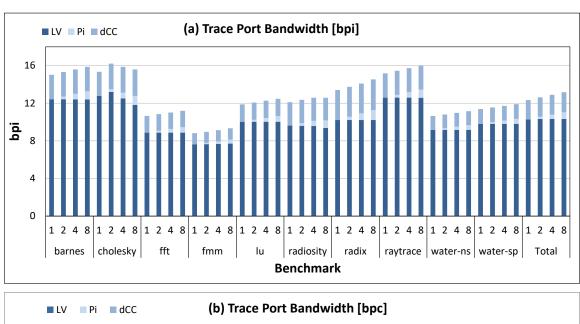

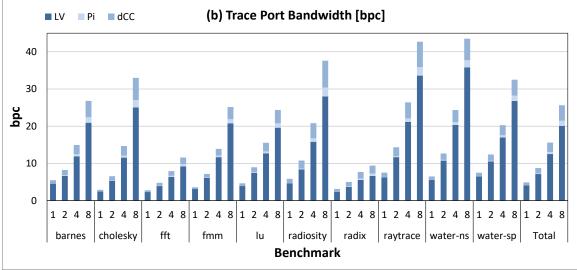

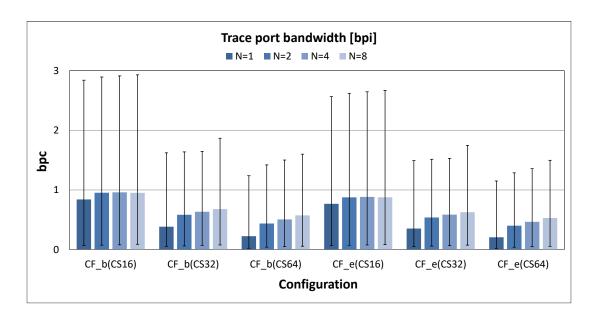

| Figure 5.3 Total average trace port bandwidth in bpi for $CF\_b$ and $CF\_e$ 107   |

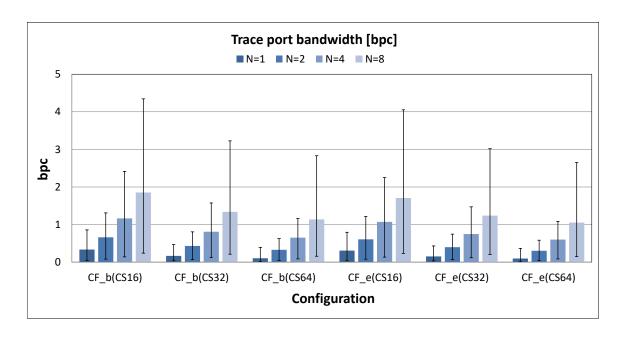

| Figure 5.4 Total average trace port bandwidth in bpc for $CF\_b$ and $CF\_e$ . 111 |

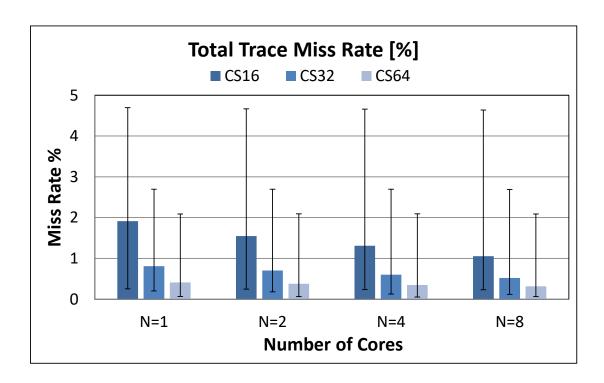

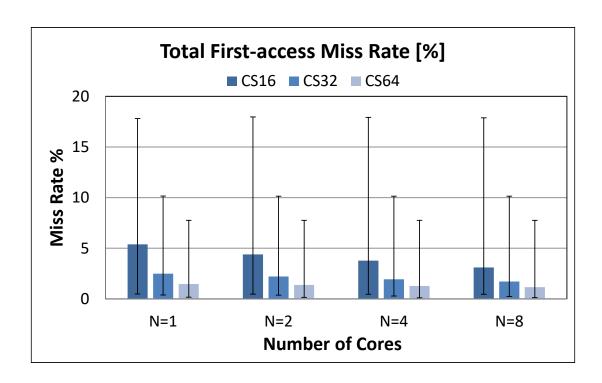

| Figure 5.5 Trace Miss Rate for $mc^2RT$ for Splash2 benchmarks                     |

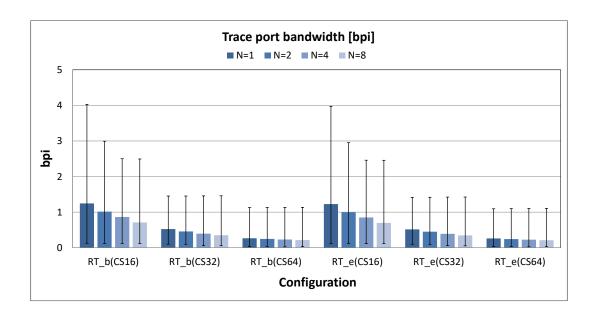

| Figure 5.6 Total average trace port bandwidth in bpi for $RT\_b$ and $RT\_e$ . 113 |

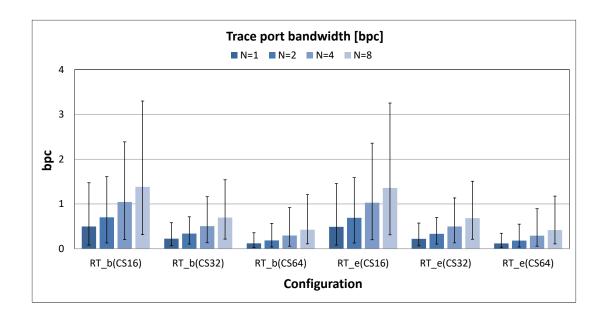

| Figure 5.7 Total average trace port bandwidth in bpc for $RT_b$ and $RT_e$ . 117   |

| Figure 5.8 First Access Miss Rate for $mc^2RT$ for Splash2 benchmarks 119          |

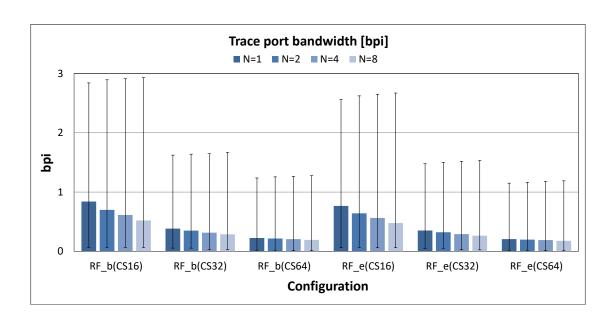

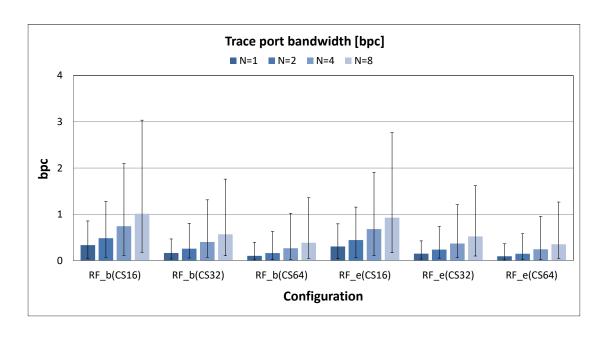

| Figure 5.9 Total average trace port bandwidth in bpi for $RF\_b$ and $RF\_e$ . 120 |

| Figure 5.10 Total average trace port bandwidth in bpc for $RF\_b$ and $RF\_e124$   |

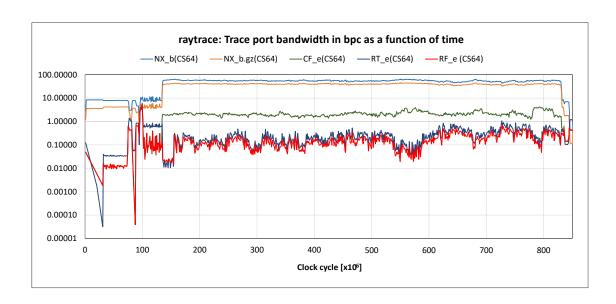

| Figure 5.11 Dynamic trace port bandwidth in bpc during execution of                |

| raytrace for $N=8$                                                                 |

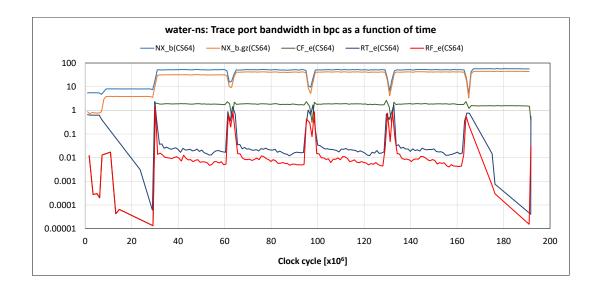

| Figure 5.12 Dynamic trace port bandwidth in bpc during execution of water-         |

| <i>ns</i> for <i>N</i> =8                                                          |

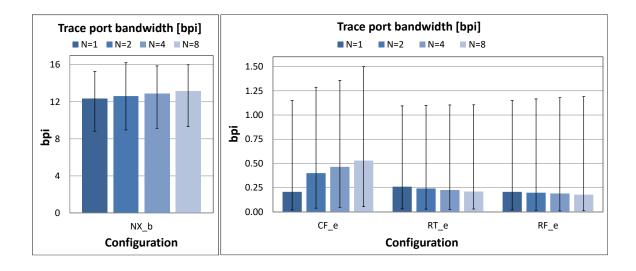

| Figure 5.13 Trace port bandwidth in bpi for CS64 configuration                     |

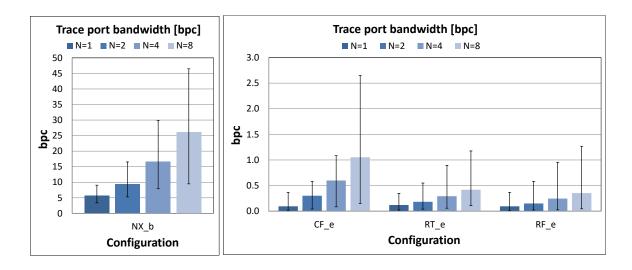

| Figure 5.14 Trace port bandwidth in bpc for CS64 configuration                     |

# LIST OF TABLES

| able                                                                   | age  |

|------------------------------------------------------------------------|------|

| Table 4.1 mlvCFiat flags                                               | . 49 |

| Table 4.2 Splash2 benchmark suite characterization                     | . 91 |

| Table 4.3 Characterization of memory reads in Splash2                  | . 92 |

| Table 4.4 Experiments conducted                                        | . 93 |

| Table 4.5 Summary of variable encoding parameters for different fields | . 98 |

| Table 5.1 Trace port bandwidth for $NX\_b$ for Splash2 benchmarks      | 101  |

| Table 5.2 Compression ratios achieved by gzip                          | 104  |

| Table 5.3 Trace port bandwidth bpi for $CF\_b$                         | 108  |

| Table 5.4 Trace port bandwidth bpi for $CF\_e$                         | 109  |

| Table 5.5 Compression ratio of $CF\_e$ relative to $NX\_b$             | 110  |

| Table 5.6 Trace port bandwidth bpi for $RT\_b$                         | 114  |

| Table 5.7 Trace port bandwidth bpi for $RT_{\_}e$                      | 115  |

| Table 5.8 Compression ratio of $RT_e$ relative to $NX_b$               | 116  |

| Table 5.9 Trace port bandwidth bpi for $RF\_b$                         | 121  |

| Table 5.10 Trace port bandwidth bpi for $RF\_e$                        | 122  |

| Table 5.11 Compression ratio of $RF\_e$ relative to $NX\_b$            | 123  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Background and Motivation

Growing complexity and sophistication of modern embedded systems and the shift toward multicores make software testing and debugging one of the most critical aspects of system development. Faster and cheaper processors with an increased level of integration have enabled new applications that were impossible just a decade ago. Users' expectations and their reliance on embedded systems have also gone up. As a result, the complexity of the software stack in embedded systems keeps growing and the time-to-market is decreasing. A recent report from the International Technology Roadmap for Semiconductors found that the software engineering and tool costs account for 80% or more of the total development cost of modern high-end embedded systems [1].

It is important to give software developers tools to quickly locate and correct all software bugs with minimum effort. When debugging, software developers often need perfect visibility of the system under test. However, achieving this visibility is not feasible due to high system complexity, limited available bandwidth for debugging data, and high operating frequencies. Traditional debugging techniques rely on single stepping, setting breakpoints, and examining the content of registers and memory locations while the processor is halted. This approach is effort- and time-consuming for software developers. In addition, it perturbs the sequence of events on

target platforms and thus is not practical in real-time cyber-physical systems. Finally, it does not scale well to multicores.

To address these challenges, modern embedded processors include on-chip resources dedicated for tracing and debugging. The trace module on the target platform collects the traces for the program of interest. With certain conditions, collected traces can be used to replay the program offline. State-of-the-art trace modules require 1 to 4 bits per executed instruction per core for control-flow traces and 8 to 16 bits per executed instruction per core for data flow traces. Thus, a 1 KB on-chip trace buffer per processor core may capture control flow traces for program segments on the order of 2000 – 8000 instructions and load data value traces for program segments on the order of 500 – 1000 instructions. It should be noted that limited program traces are not sufficient in locating software bugs in modern processors because there could be millions of instructions between the origin of the bug and its manifestation. To capture traces, especially Nexus-like load data value traces for the entire program, we require deep trace buffers and wide trace ports. However, hardware vendors have little incentive to spend a lot of on-chip resources, thus increasing the system cost, just to help software developers find more bugs faster.

#### 1.2 Scope of this Thesis

Capturing load data value traces on-the-fly is important in debugging multicore embedded systems. Load data value traces are created by recording values read from memory and I/O devices. These traces captured on the target platform and streamed out to a software debugger are necessary under certain conditions to deterministically replay programs offline. In this thesis, trace port bandwidth requirements for Nexus-like load data value traces are analyzed to illustrate challenges in capturing data traces in multicores when running a set of parallel programs and using commercial state-of-the-art tracing techniques. The trace port bandwidth is measured in bits per instruction executed (bpi) and bits per processor clock cycle (bpc). The total average trace port bandwidth (bpi) for the entire Splash2 benchmark suite ranges from 12.34 when N=1 to 13.17 when N=8 where N is the number of cores. For a given multicore model the trace port bandwidth (bpc) ranges from 4.92 when N=1 to 25.64 when N=8. Several benchmarks require an average trace port bandwidth of over 40 bits per clock cycle. These results illustrate the challenges of capturing and streaming out load data value trace. Having trace ports with over 40 pins that work at processor clock speed or megabytes of on-chip trace buffers is not practical.

To address data tracing challenges, we introduce three new techniques for unobtrusive capturing and filtering of load data value traces in real-time in multicore platforms. These techniques are named (i) mlvCFiat – multicore load value cache first access tracking, (ii)  $mc^2RT$  – multicore cache-coherent read tracking, and (iii)  $mc^2RFiat$  – multicore cache-coherent read with first access tracking. They rely on on-chip tracking of memory reads in data caches on the target platform and equivalent changes in the software debugger. The software debugger simulates the behavior of data caches and trace modules on the target platform during program replay, thus reducing the number of trace messages that need to be emitted by the target platform. This way we reduce the trace port bandwidth requirements and requirements for on-chip trace buffers. The three techniques differ in the number of tracking bits per data cache block and the level of support for cache coherence proto-

col. Using an execution-driven cycle-accurate simulator and the Splash2 parallel programs, we evaluate the effectiveness of the proposed techniques as a function of system parameters, such as data cache size, the number of cores (N), and encoding mechanism.

The total average trace port bandwidth using the mlvCFiat technique with CS64 configuration ranges from 0.21 bpi when N=1 to 0.53 bpi when N=8. mlvCFiat reduces the total average trace port bandwidth relative to Nexus-like load data value traces by 16.1 to 59.6 times when N=1 and 15.0 to 24.8 times when N=8. The total average trace port bandwidth using the  $mc^2RT$  technique with CS64 configuration ranges from 0.26 bpi when N=1 to 0.21 bpi when N=8.  $mc^2RT$  reduces the total average trace port bandwidth relative to Nexus-like load data value traces from 10.1 to 47.3 times when N=1 and from 18.9 to 62.5 times when N=8. The total average trace port bandwidth using the  $mc^2RFiat$  technique with CS64 configuration ranges from 0.21 bpi when N=1 to 0.18 bpi when N=8.  $mc^2RFiat$  reduces the total average trace port bandwidth relative to Nexus-like load data value traces by 16.1 to 59.6 times when N=1 and 27.6 to 73.8 times when N=8.

#### 1.3 Contributions

The main contributions of this work are as follows.

Characterization of trace port bandwidth requirements in multicores

for Nexus-like time stamped load data value traces as a function of the

number of cores. Both bits per instruction and bits per clock cycle as

measures of the required trace port bandwidth are considered.

- Introduction of hardware/software techniques mlvCFiat, mc²RT, and mc²RFiat that capture and compress load data value traces in multicores.

- A detailed experimental evaluation of the trace port bandwidth required by the proposed techniques, while varying the number of cores, cache sizes, and encoding approaches.

- An analysis of dynamic trace port bandwidth during benchmarks' execution.

#### 1.4 Outline

The rest of the thesis is organized as follows. CHAPTER 2 discusses the background, focusing on tracing and debugging in state-of-the-art embedded systems and especially on load data value traces. CHAPTER 3 describes the proposed techniques for capturing and compression of load data value traces in multicores. We introduce three techniques namely, mlvCFiat,  $mc^2RT$ , and  $mc^2RFiat$  that differ in their effectiveness and the level of hardware support. CHAPTER 4 describes the experimental evaluation of the proposed techniques and experimental environment used to create Nexus-like load data value traces and filtered traces. CHAPTER 5 discusses the results of the experimental evaluation. Finally, CHAPTER 6 gives concluding remarks.

## CHAPTER 2

#### BACKGROUND AND MOTIVATION

This chapter gives a more detailed view of debugging with tracing in embedded systems (Section 2.1). It also describes four classes of operations as defined in the Nexus 5001 standard. Section 2.2 describes load data value traces in multicores. Section 2.3 gives an overview of related work for this research.

#### 2.1 Tracing in Embedded Multicores

Embedded processor and systems-on-a-chip often include on-chip trace modules that include resources to support tracing and debugging operations. The IEEE Nexus 5001 standard [2] defines functions and a general-purpose interface for software development and debugging of embedded processors. Nexus 5001 specifies 4 classes of debugging operations (Class 1 – Class 4). Higher classes support more complex debug operations but require more on-chip resources and wider trace ports, thus increasing the system cost.

Class 1 supports basic run control debugging, including setting breakpoints, single stepping, and changing the content of the memory or registers while the processor is halted. It is typically supported through the JTAG interface [3]. Class 2 adds support for capturing control-flow traces and streaming them out in near real time. Class 3 adds support for capturing and streaming out data flow traces (memory reads, memory writes, I/O reads, and I/O writes) in near real time. Finally, Class 4 adds support for emulating memory and I/O through the trace port.

Class 1 operations are routinely used to debug programs and widely supported in modern embedded platforms but are unsatisfying in many respects. First, it is more time-consuming and puts the burden on the software developer. Second, setting a breakpoint in real-time embedded systems and cyber-physical systems is not practical. Third, when the processor is halted for debugging, the actual order of events executed by the processor may change relative to the normal operation, which in turn may result in disappearing bugs. Finally, Class 1 operations do not scale well with multicores where setting breakpoints in one core may have an adverse impact on other processor cores.

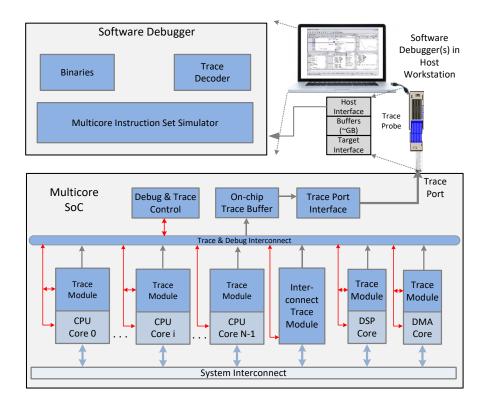

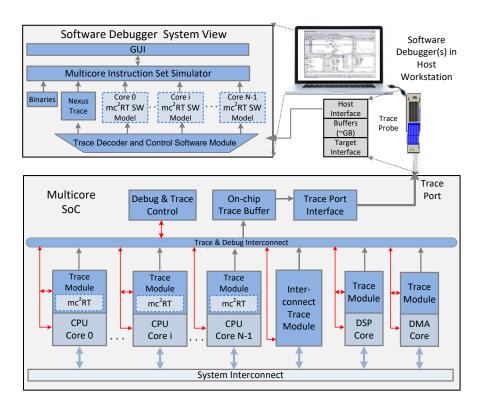

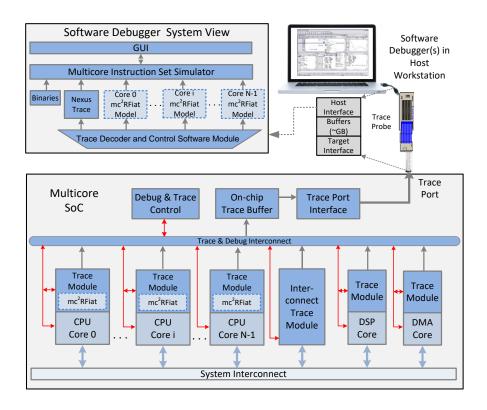

To address these challenges, modern embedded processors rely on on-chip resources dedicated for tracing and debugging. Figure 2.1 shows a multicore system-on-a-chip (SoC) with trace and debug infrastructure. The multicore has N processor cores, a DSP core and a DMA core, all connected through a system interconnect. Each core has its own trace module which is responsible for capturing traces of interest. All the trace modules are connected to a debug and trace control unit through a trace and debug interconnect. Traces collected by the trace modules are temporarily stored in on-chip trace buffers before they are streamed out through a dedicated trace port to an external trace probe. The external trace probe connected to the host workstation may include Gigabytes of memory to store collected traces. These traces are then read by the software debugger running on a development workstation during a program replay, thus enabling a complete reconstruction of events that occurred on the target platform.

Control-flow traces enable the reconstruction of the program's flow only; for certain classes of hardware and software bugs control flow traces are sufficient, but for some classes of bugs such as data race conditions, control-flow traces are not sufficient. Data-flow traces enable a complete replay of the executed program under certain conditions. To replay the program offline, the software debugger on the host workstation (Figure 2.1) relies on an instruction set simulator of the target platform, the program binary, initial conditions of the target platform and exception traces in addition to the data-flow traces. Replaying a program offline gives valuable information about shared memory access patterns, possible data race conditions, and better insights into the behavior of the target system.

Many chip vendors are including trace modules, examples include ARM's CoreSight [4], MIPS's PDTrace [5], Infineon's MCDS [6], and Freescale's MPC5500 [7]. State-of-the-art trace modules require trace port bandwidth in the range of 1 to 4 bits per executed instruction per core for control flow traces [4] and 8 to 12 bits per executed instruction per core for data flow traces [4]. Thus, a 1 KB on-chip trace buffer per processor core may capture control flow traces for program segments on the order of 2000 – 8000 instructions and data flow traces for program segments on the order of 500 – 1000 instructions. These limited traces are not enough to find the bugs because the origin of the bug and its manifestation are often millions of instructions apart. To capture traces, especially data-flow traces, for the entire program, deep trace buffers and wide trace ports are needed, significantly increasing the system complexity and cost. Hence, hardware vendors rarely support the higher classes of the Nexus 5001 standard. This problem is even worse in multicores where the number of I/O pins dedicated to the trace port cannot keep pace with the exponential growth in the number of cores on a single chip.

Figure 2.1 Debugging and tracing in multicores: a detailed view

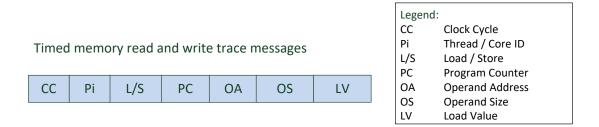

#### 2.2 Memory Data Traces

Data traces contain information about executed memory read and memory write instructions in the order in which they occurred during program execution. A typical data trace message may have relevant information, such as instruction address, type of memory operation (read or write), operand address, operand size, and operand value. In multicores, in addition to these fields, a trace message holds information about core/thread id and a global time stamp if the trace messages are not emitted in the order they occurred. The format of the trace messages may change depending on the context in which they are used and sometimes traces are needed only memory read or memory write.

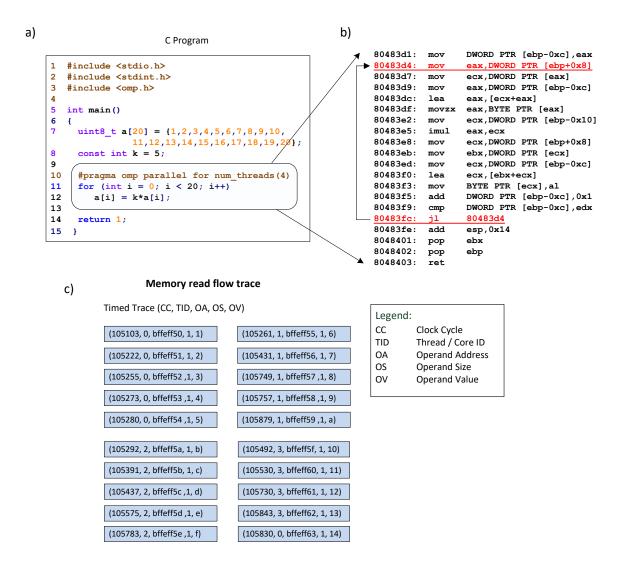

Figure 2.2 shows an example of trace messages for memory reads of an OpenMP C program. The program scales each element of the input array and writes the result to the same location. The input array holds 20 single byte elements. All the operations executed by each thread are independent, thus each thread processes 5 elements. Figure 2.2b shows the assembly code of the parallel loop executed by each thread. Figure 2.2c shows trace messages capturing memory reads during program execution. Each message includes a global time stamp, thread id, operand address, operand size, and operand value.

Figure 2.2. Memory read trace: an example a) C program b) equivalent x86 assembly c) memory read flow traces

#### 2.3 Related Work

Modern embedded processors increasingly include on on-chip trace and debug infrastructure [4]–[9]. However, commercially available trace modules typically implement only rudimentary forms of hardware filtering with a relatively small com-

pression ratio. Irrgang and Spallek analyzed the Nexus and trace port configurations and their impact on achievable compression for instruction traces and found that 8-bit trace ports are sufficient [10].

Several recent research efforts in academia propose trace-specific compression techniques that achieve higher compression ratios. A class of these techniques is applicable only to software traces as they combine trace-specific and general-purpose compression algorithms and, in general, are not applicable to hardware tracing [11]–[19].

Another group of proposed techniques is applicable to hardware tracing. Several techniques rely on hardware implementations of general-purpose compressors [20], [21]. For example, Kao et al. [22] introduce an LZ-based compressor specifically tailored to control-flow traces. The compressor encompasses three stages: filtering of branch and target addresses, difference-based encoding, and hardware-based LZ compression. A novel approach, the stream based compression algorithm [15], exploits inherent characteristics of program execution traces for compression. A double-move-to-front compressor introduced by Uzelac and Milenkovic [20] encompasses two stages, each featuring a history table performing the move-to-front transformation. Although these techniques significantly reduce the size of the control-flow trace that needs to be streamed out, they have a relatively high complexity (50,000 gates and 24,600 gates, respectively).

A set of recently developed techniques relies on architectural on-chip structures such as stream caches [23]–[25] and branch predictors [14], [26], [27] with their software counterparts in software debuggers, as well as effective trace encoding to significantly reduce the size of traces that needs to be streamed out. Uzelac et

al. [26] introduced *TRaptor* for control-flow traces that requires only 0.029 bits per instruction on the trace port (~34-fold improvement over the commercial state-of-the-art) per processor core at the hardware cost of approximately 5,000 gates. Tewar et. al. introduced *mcfTRaptor* that extends *TRaptor* to multicore platforms [28].

Whereas a number of studies in academia focus on capturing and compressing control-flow traces, relatively few studies look at on-the-fly data tracing. One interesting solution for debugging multicore SoCs called hidICE was proposed by Hochberger and Weiss [29]. It relies on a hardware emulator that replicates all master cores and memories from the target platform. The target platform reports only exceptions and data reads from peripherals that cannot be inferred by the emulator. However, hidICE is cost-prohibitive because it requires not only changes on the target platform to include a synchronization core and a new trace port, but also requires a sophisticated hardware emulator that replicates all the master modules and the RAM memory from the target platform. In addition, there has been no quantitative evaluation of hidICE.

This research relies on the prior work of Uzelac and Milenkovic. For load value traces, Uzelac and Milenkovic [30], [31] introduced cache first-access tracking mechanism (c-fiat) that reduces the trace size between 5.8 to 56 times, depending on the cache size. However, this technique has been demonstrated on uniprocessors only. In addition, prior studies were based on functional simulation and did not address the challenges of producing ordered or time-stamped trace messages coming from multiple cores. To the best of our knowledge, there have been no academic studies focusing on the quantitative evaluation of data tracing requirements and development of cost-effective trace filtering techniques scalable to multicores.

The problem of tracing requirements in multicores running parallel programs requires additional study and answering the following questions. What is the required trace port bandwidth? How does trace port bandwidth scale up with multiple processor cores? How the existing techniques may be applied to multicores? These are some of the questions that are fully addressed in this thesis [32]–[34]. In this thesis, we want to explore requirements for real-time load data value tracing in multicores and introduce cost-effective solutions that scale well with a number of processor cores.

## CHAPTER 3

#### NEW TECHNIQUES FOR DATA TRACING IN MULTICORES

This chapter discusses novel techniques for capturing and compressing load data value traces in multicores; mlvCFiat, which stands for multicore load value cache first-access tracking (Section 3.1),  $mc^2RT$ , which stands for multicore cache coherent read tracking (Section 3.2) and  $mc^2RFiat$ , which stands for multicore cache coherent read with first-access tracking (Section 3.3). All three techniques are designed to reduce the pressure on the trace port and require relatively modest hardware support on the target platform and the software debugger capable of mirroring hardware events during program replay.

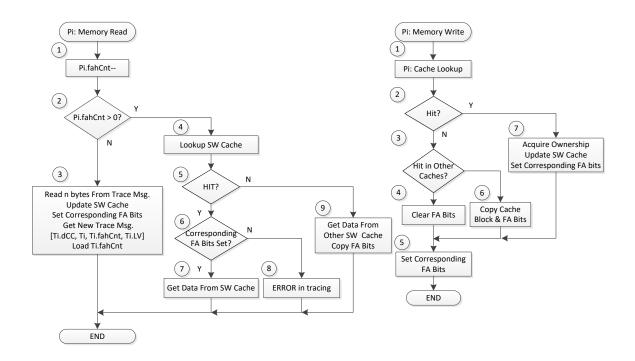

#### 3.1 mlvCFiat

mlvCFiat is a hardware-based mechanism for a multicore processor that reduces the number of load data value traces by collecting a minimal set of trace messages with the help of a cache first access tracking mechanism [33]. mlvCFiat is an extension of the existing CFiat mechanism for capturing and filtering load data value traces in single-core processors [35].

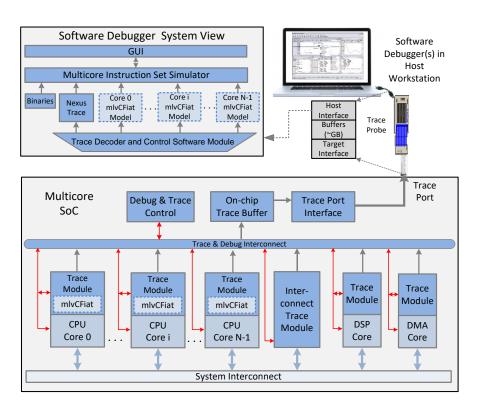

Figure 3.1 shows the block diagram of a multicore system-on-chip (SoC) with the trace and debug infrastructure; light blue boxes represent additional *mlvCFiat* hardware and software modules. *mlvCFiat* requires hardware changes to the L1 data caches to capture and compress load data value traces. It also requires the software debugger to maintain exact models of the data caches with the same organiza-

tion and updating policies as in the target platform. The data cache models in the software debugger are updated while replaying the program offline in the same way the data cache are updated on the target platform. mlvCFiat ensures that the hardware platform only emits trace messages with load data values that cannot be inferred by the software debugger from the software of the data cache. This approach significantly reduces the number of trace messages that need to be emitted by the target platform, thus reducing the pressure on the trace port, which in turn reduces the on-chip resources and system cost.

Figure 3.1 A system view of *mlvCFiat*

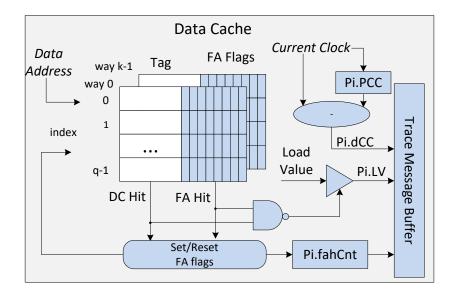

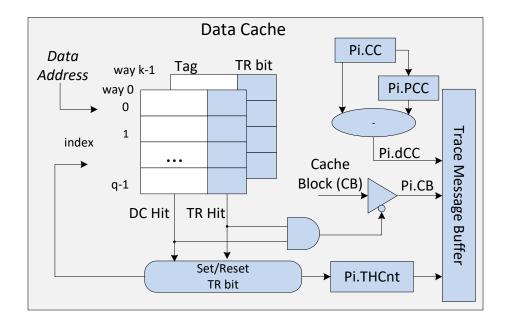

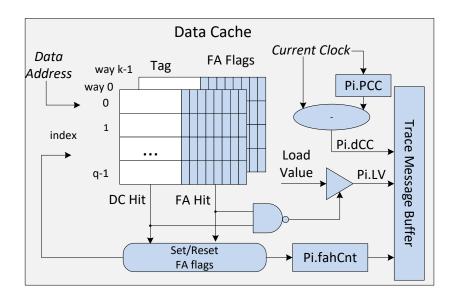

Figure 3.2 gives a detailed description of the hardware changes for a single core on the target platform (core i) required to support mlvCFiat. Each cache block is augmented with first-access (FA) tracking bits. These bits keep track of sub-blocks that need to be reported to the software debugger. For example, if a single firstaccess tracking bit can protect a sub-block of 4 bytes, then a 32-byte cache block would requires 8 first-access tracking bits. However, the size of sub-block protected by a first-access bit is a design parameter. When a sub-block is read for the first time, the sub-block is traced out and the corresponding FA flag is set. The previously reported sub-blocks do not have to be reported again as they can be inferred by the software debugger. This way we exploit temporal and spatial locality of data accesses to significantly reduce the number of trace messages that need to be reported. Each trace module includes a local first access hit counter (Pi.fahCnt) that counts the number of successive first-access hits on processor core i. The value of this counter is reported in a trace message on a first-access miss. The Pi.PCC register records the time stamp of a previously reported first-access miss. This register is used to a determine differentially encoded time stamp for the current trace miss event that occurs at clock cycle Pi.CC (Pi.dCC=Pi.CC - Pi.PCC).

Figure 3.2. mlvCFiat structures for core i

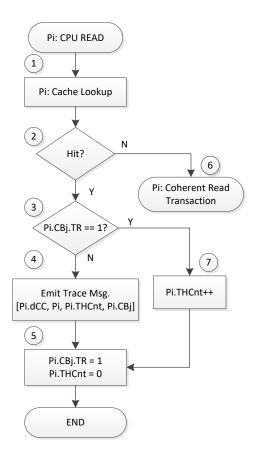

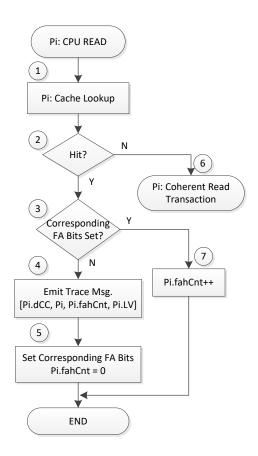

Figure 3.3 describes mlvCFiat operation on the target platform carried out for memory reads, memory writes, and external invalidate requests. Each memory read results in an L1 data cache lookup; if the requested data item is found in the L1 data cache ( $cache\ hit\ event$ ) and the corresponding FA bit(s) is set, we call this an FA  $hit\ event$ . In this case, we do not need to emit a trace message because the software debugger can retrieve the data from its software copy of the data cache. To synchronize mlvCFiat on the target platform with the software debugger, the first-access hit counter (Pi.fahCnt) is incremented (step 6 in Figure 3.3a). If the corresponding FA bit(s) is not set ( $FA\ miss\ event$ ) then a trace message is emitted. The trace message includes a differentially encoded time stamp for that core (Pi.dCC), core id (Pi), the current value of the first-access hit counter (Pi.fahCnt), and the corresponding data cache sub-block that includes the load value (Pi.LV). Once the trace message is emitted, the corresponding FA bit(s) is set, and the Pi.fahCnt is cleared (step 4 in Figure

3.3a). For a cache read miss event, a new cache block is fetched from the memory and loaded into the data cache, the corresponding FA are cleared, and then the same steps as in FA miss event are carried out (steps 3 and 4 in Figure 3.3a). The FA bits are also updated for memory writes and external invalidations. For each memory write operation, if we have a cache hit and if the data is shared then the current processor acquires the ownership by invalidating the cache block in the other processor caches. If the current write operation writes an entire sub-block protected by an FA bit, then the corresponding FA bit is set (step 4 in Figure 3.3b). In case of a write miss, the corresponding FA bits are cleared for a newly fetched cache bock, and the same steps are carried out as in the case of a cache hit (steps 3 and 4 in Figure 3.3b). For external invalidations, the FA bits for the invalidated cache block are cleared. By capturing trace events at the L1 data cache level, cache coherence protocols are transparent to mlvCFiat. Thus, a write request to a shared block is treated as a miss in mlvCFiat.

Figure 3.3 mlvCFiat operations on the target core i for a) memory reads, b) memory writes, and c) external invalidations

Figure 3.4 describes steps carried out by the software debugger in response to memory reads, memory writes, and external invalidations in a steady state. To replay the program offline, the software debugger relies on an instruction set simulator (ISS) of the target platform that uses the software models of data caches, first-access hit counters (*Pi.fahCnt*), the program binary, the exception traces, and the *mlvCFiat* trace messages received from the target platform. The software debugger reads and decodes trace messages while replaying the program. The formats of trace messages and lengths of the fields are known to the software debugger. The software copies of data caches and *Pi.fahCnt* are updated during the program replay using the same updating policies employed on the target platform. The debugger replays the instructions for each core using the corresponding ISS. For each memory read

operation, Pi.fahCnt is decremented by 1. If Pi.fahCnt>0 and the corresponding FA bits are set, the debugger retrieves the data values from the software copy of the data cache and moves to replay the next instruction. If the corresponding FA bits are not set it implies that there is an error in tracing (step 7 in Figure 3.4a). If Pi.fahCnt=0, we have a first read miss event: the load data value is retrieved from the current trace message, the software copy of the data cache is updated, and the corresponding FA bits are set. Then, a new trace message from the trace buffer is read for that core and Pi.fahCnt is updated with the new value extracted from the trace message (step 3 in Figure 3.4a). For each memory write operation, if the data is found in the software data cache and the cache block is shared, the current processor acquires ownership by invalidating copies of the cache block in other caches. Once the software copy of the cache block is updated, if the current write operation writes the entire sub-block protected by an FA, bit then the corresponding FA bit is set (step 4 in Figure 3.4b). In the case of external invalidations, the FA bits for the invalidated cache block are cleared.

Figure 3.4 mlvCFiat operations in the software debugger on core i for a) memory reads, b) memory writes, and c) external invalidations

## $3.2 \quad mc^2RT$

$mc^2RT$  is a hardware-based mechanism that reduces load data value traces by collecting a minimal set of trace messages by exploiting the MOESI [36] cache coherence protocol with a single tracking bit per data cache block [34].

Figure 3.5 shows the block diagram of a multicore system-on-chip (SoC) with the trace and debug infrastructure; light blue boxes represent additional  $mc^2RT$  hardware and software modules.  $mc^2RT$  requires hardware changes on the L1 data caches to capture and compress load data value traces. It also requires a software debugger to maintain an exact model of the data caches with the same organization and updating policies as the target platform. The data cache models in the software

debugger are updated while replaying the program offline in the same way the data caches are updated on the target platform.  $mc^2RT$  ensures that the hardware platform only emits trace messages with load data values that cannot be inferred by the software debugger from the software copy of the data caches. This approach significantly reduces the number of trace messages that need to be emitted by the target platform, thus reducing the pressure on the trace port, which in turn reduces the onchip resources and the system cost.

Figure 3.5 A system view of  $mc^2RT$

Figure 3.6 gives a detailed description of hardware changes for a single core on the target platform (core i) required to support  $mc^2RT$ . Each cache block is aug-

mented with a trace tracking bit (TR). The trace bit keeps track of whether the associated cache block is reported or not to the software debugger. The cache block fetched from the memory for the first time by a processor having a read miss will be emitted through the trace port. Once the cache block is emitted, the trace bit is set. Previously reported cache blocks do not have to be reported again as they can be inferred by the software debugger. This way we exploit the temporal and spatial locality of data accesses to significantly reduce the number of trace messages that need to be reported. Each trace module includes a local trace hit counter (Pi.THCnt) that counts the number of successive trace hits on processor core i. The current value of this counter is reported together in a trace message on a trace miss. The Pi.PCC register records the time stamp of a previously reported trace message. The register is used to determine a differentially encoded time stamp for the current trace miss event that occurs at a clock cycle Pi.CC (Pi.dCC = Pi.CC - Pi.PCC).

Figure 3.6  $mc^2RT$  structures for core i

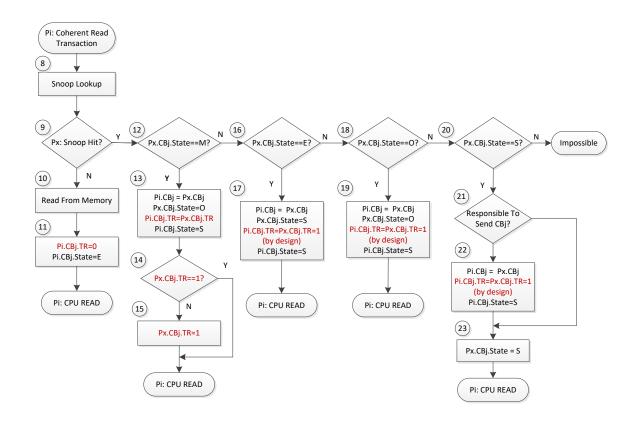

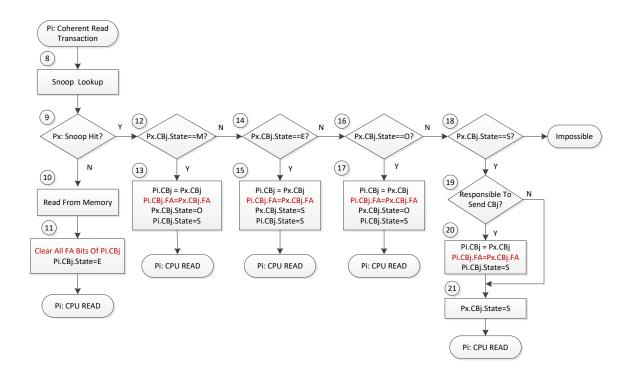

Figure 3.7 and Figure 3.8 describe  $mc^2RT$  operation on the target platform for memory reads by core i. Each memory read results in an L1 data cache lookup. If the requested data item is found in the L1 data cache (cache hit event) and the trace bit is set, we have a trace hit event. In this case, we do not need to emit a trace message because the software debugger can retrieve the data from its software copy of the data cache. To synchronize trace hit events in  $mc^2RT$  on the target platform with the software debugger, the trace hit counter (Pi.THCnt) is incremented (step 7). If the corresponding trace bit is not set (trace miss event), a trace message is emitted. The trace message includes a differentially encoded time stamp for that core (Pi.dCC), core id (Pi), the current value of the trace hit counter (Pi.THCnt) and the corresponding cache-block that includes the load data value (Pi.CBj) (step 4). Once the trace message is emitted the corresponding trace bit is set, and Pi.THCnt is

cleared (step 5). For a cache read miss event, a Coherent Read Transaction is issued (step 6). The requested cache block is supplied to the processor core i (Pi) by another processor cache (Px) or by main memory. In a Coherent Read Transaction, a snoop lookup is performed by all the caches, as follows and shown in Figure 3.8.

- If the snoop lookup finds the requested cache block in the *Modified*(M) state, it is transferred to Pi along with its trace bit. The state of the cache block in Px transitions to Owned (O) and the new state of the Pi cache block is Shared (S) (step 13). If this cache block is not previously reported (Px.CBj.TR=0) by processor Px, then it is reported by processor Pi. Since the cache block is going to be reported by the processor Pi, the trace bit for Px is set to 1 (step 15).

- If the snoop lookup finds the requested cache block in the *Exclusive*(E) state, it is transferred to Pi along with its trace bit. Since this cache block is already reported first time when it is read from memory, trace bit for Pi and Px is 1. The states of the cache block in Pi and Px are updated to Shared state (step 17).

- If the snoop lookup finds the requested cache block in the Owned state, the requested cache block is transferred to Pi along with its trace bit and the new state of Pi is updated to Shared. The trace bit for Pi and Px is 1 because the only way to transition to Owned state is from the Modified state by having coherent read request from another processor to that cache block (step 19).

- If the snoop lookup finds the requested cache block in the Shared state, it is transferred to Pi along with its trace bit only if the current

processor is responsible to transfer. By design a cache block can be in the *Shared* state only after *Coherent Read Transaction* therefore, the cache block is already reported by another processor and the trace bit for Pi and Px is 1. The state of the cache block in Pi is updated to *Shared* state (step 21).

• If the requested cache block is not found in any processor cache, then it is retrieved from main memory and corresponding trace bit is cleared. The new state of the cache block is set to *Exclusive*.

After Coherent Read Transaction, the same steps as in the CPU READ operation are carried out.

Figure 3.7  $mc^2RT$  operation on the target core i for memory reads

Figure 3.8 Coherent Read Transaction in  $mc^2RT$  on the target core i

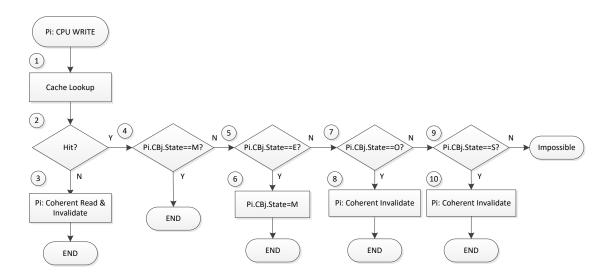

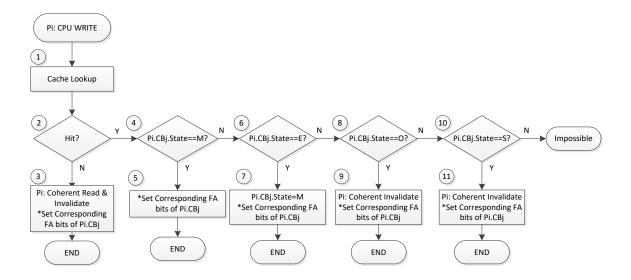

Figure 3.9, Figure 3.10, and Figure 3.11 describes the operation of  $mc^2RT$  on the target platform for memory writes by core i. The data cache is looked up for the requested cache block. In the case of a cache hit in the Exclusive state, the state of the cache block is upgraded to the Modified state (step 6). If the requested cache block is in the Owned or Shared state, a Coherent Invalidate transaction is initiated. A snoop lookup is performed by all other caches. If the snoop lookup finds the cache block in the Shared state or Owned state, then the cache block is invalidated and the trace bit is cleared. The state of the cache block in Pi is updated to Modified (step 28 and step 30). If the requested cache block is not found in the processor Pi, then a

Coherent Read and Invalidate transaction is initiated. The sequence of events performed by other caches in response to a Coherent Read and Invalidate transaction is described as follows:

- If the snoop lookup finds the requested cache block in the *Modified* state, it is transferred to *Pi* along with its trace bit. The new state of the *Pi* cache block is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The trace bit for the invalidated cache block is cleared (step 16).

- If the snoop lookup finds the requested cache block in the *Exclusive* state, it is transferred to *Pi* along with its trace bit. By design, the trace bit for a cache block in *Pi* and *Px* is 1, because this cache block is already reported first time when it is read from memory. The new state of the *Pi* cache block is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The trace bit for the invalidated cache block is cleared (step 18).

- If the snoop lookup finds the requested cache block in the *Owned* state, it is transferred to *Pi* along with its trace bit. The new state for cache block in *Pi* cache is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The trace bit for *Pi* and *Px* is 1 because the only way to transition to *Owned* state is from the *Modified* state by having a coherent read request from another processor to that cache block. The trace bit for the invalidated cache block is cleared (step 20).

- If the snoop lookup finds the requested cache block in the Shared state, it is transferred to Pi along with its trace bit if the current pro-

cessor is responsible to transfer. By design, a cache block can be in the *Shared* state only after a Coherent Read Transaction, therefore the cache block is already reported by another processor, the trace bit for a cache block in Pi and Px is 1. The cache block of the processor Px is invalidated and the corresponding trace bit is cleared (step 23 and step 24).

• If the requested cache block is not found in any processor cache, then it is retrieved from main memory and corresponding trace bit is cleared. The new state of the cache block is set to *Modified* (step 13 and step 14).

Figure 3.9  $mc^2RT$  operation on the target core i for memory writes

Figure 3.10 Coherent Read and Invalidate in  $mc^2RT$  on target core i

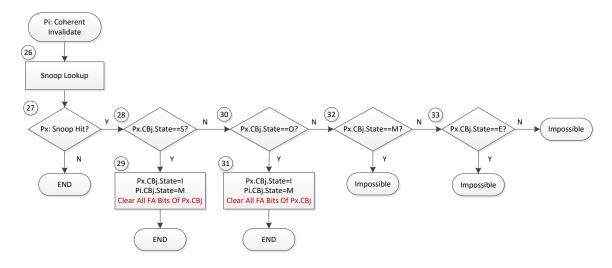

Figure 3.11 Coherent Invalidate in  $mc^2RT$  on target core i

Figure 3.12 describes the steps carried out by the software debugger in response to memory reads and memory writes in a steady state. To replay the program offline, the software debugger relies on an instruction set simulator (ISS) of the target platform that uses the software models of data caches, trace hit counters (Pi.THCnt), the program binary, exception traces, and the  $mc^2RT$  trace messages received from the target platform. The software debugger reads and decodes trace messages while replaying the program. The formats of the trace messages and lengths of the fields are known to the software debugger. The software copies of data caches and Pi.THCnt are updated during the program replay using the same updating policies employed on the target platform. The debugger replays the instructions for each core using the corresponding ISS. For each memory read operation, *Pi.THCnt* is decremented by 1. If *Pi.THCnt>*0 and if the data is found in the software copy of the data cache of processor Pi with the corresponding trace bit set, the debugger retrieves the data values from the software copy of the data cache and moves to replay the next instruction. If the corresponding trace bit is not set, it implies that there is an error in tracing (step 7 in Figure 3.12a). If Pi.THCnt>0 and data is not found in the software copy of the data cache of processor Pi, then the software debugger gets data from another processors data cache. If Pi.THCnt=0, we have a trace miss event: the load data value is retrieved from the current trace message, the software copy of the data cache is updated and the corresponding trace bit is set. Then, a new trace message from the trace buffer is read for that core and Pi.THCnt is updated with a new value extracted from the trace message (step 3 in Figure 3.12a). For each memory write operation, if the data is found in the software cache and the cache block is shared, the current processor acquires the ownership by

invalidating copies of the cache block in other caches. If the data is a hit in other caches then, the trace bit is inherited.

Figure 3.12  $mc^2RT$  operation in the software debugger on core i for a) memory reads b) memory writes

#### $3.3 \quad mc^2RFiat$

$mc^2RFiat$  is a hardware-based mechanism that reduces load data value traces by collecting a minimal set of trace messages by exploiting the MOESI cache coherence protocol. This technique is a combination of mlvCFiat and  $mc^2RT$ ; it requires additional support to copy first-access tracking bits from another cache. This can be implemented by either having additional data lines on the bus to carry FA bits or an extra bus transaction.

Figure 3.13 shows the block diagram of a multicore system-on-chip (SoC) with trace and debug infrastructure; light blue boxes represents additional  $mc^2RT^2$  hardware and software modules.  $mc^2RFiat$  requires hardware changes on the L1 data caches to capture and compress load data value traces. It also requires the software debugger to maintain exact models of the data caches with the same organization and updating policies as in the target platform. The data cache models in the software debugger are updated while replaying the program offline in the same way the data caches are updated on the target platform.  $mc^2RFiat$  ensures that the hardware platform emits only trace messages with load data values that cannot be inferred by the software debugger from the software copy of the data caches. This approach significantly reduces the number of trace messages that need to be emitted from the target platform, thus reducing the pressure on the trace port, which in turn reduces on-chip resources and the system cost.

Figure 3.13 A system view of  $mc^2RFiat$

Figure 3.14 gives a detailed description of hardware changes for a single core on the target platform (core i) required to support  $mc^2RFiat$ . Each cache block is augmented with first-access (FA) tracking bits. These bits keep track of sub-blocks that need to be reported to the software debugger. For example, if a single first-access tracking bit can protect a sub-block of 4 bytes, then a 32-byte cache block requires 8 first-access tracking bits. However, the size of the sub-block protected by a first-access bit is a design parameter. When a sub-block is read for the first time, the sub-block is traced out and the corresponding FA bit(s) is set. The previously reported sub-blocks do not have to be reported again as they can be inferred by the software debugger. This way we exploit temporal and spatial locality of data accesses to significantly reduce the number of trace messages that need to be reported.

Each module includes a local first access hit counter (Pi.fahCnt) that counts the number of successive first-access hits on processor core i. The value of this counter is reported together in a trace message on a first-access miss. The Pi.PCC register records the time stamp of a previously reported first-access miss. This register is used to determine differentially encoded time stamp for the current trace miss event that occurs at clock cycle Pi.CC (Pi.dCC = Pi.CC - Pi.PCC).

Figure 3.14  $mc^2RFiat$  structures for core i

Figure 3.15 and Figure 3.16 describes the operation of  $mc^2RFiat$  on the target platform for memory reads by core i. Each memory read results in an L1 data cache lookup. If the requested data item is found in an L1 data cache ( $cache\ hit\ event$ ) and the corresponding first-access bit(s) is set, we have an  $FA\ hit\ event$ . In this case, we do not need to emit a trace message because the software debugger can retrieve data from its software copy of the data cache. To synchronize  $mc^2RFiat$  on the target plat-

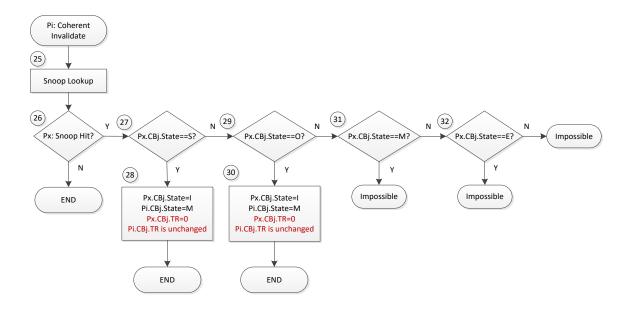

form with the software debugger, the first-access hit counter (Pi.fahCnt) is incremented (step 7). If the corresponding FA bit(s) is not set  $(FA\ miss\ event)$ , a trace message is emitted. The trace message includes a differentially encoded time stamp for that core (Pi.dCC), core id (Pi), the current value of first-access hit counter (Pi.fahCnt) and the corresponding data cache sub-block that include the load value (Pi.LV) (step 4). Once the trace message is emitted, the corresponding FA bit(s) is set, and the Pi.fahCnt counter is cleared (step 5). For a cache read miss event, a Coherent Read Transaction is issued (step 6). The requested cache block is supplied to the core i (Pi) by another processor cache (Px) or by main memory. In Coherent Read Transaction, a snoop lookup is performed by all the caches, as follows:

- If the snoop lookup finds the requested cache block in the *Modified*(*M*) state, it is transferred to *Pi* along with its *FA* bits. The state of the cache block in *Px* transitions to *Owned* (*O*) and the new state of the *Pi* cache block is *Shared* (*S*) (step 13).

- If the snoop lookup finds the requested cache block in the *Exclusive*(E) state, it is transferred to *Pi* along with its *FA* bits. The states of the cache block in *Pi* and *Px* are updated to *Shared* state (step 15).

- If the snoop lookup finds the requested cache block in the Owned state, it is transferred to Pi along with its FA bits. The new state of Pi cache block is updated to Shared (step 19) and the Px state is unchanged (step 17).

- If the snoop lookup finds the requested cache block in the Shared state, it is transferred along with its FA bits to Pi only if the current processor is responsible to transfer. The new state of the Pi cache

block is updated to *Shared* and the *Px* state is unchanged (steps 20 and 21).

• If the requested cache block is not found in any processor cache, then it is retrieved from main memory and the corresponding *FA* bits are cleared. The new state of the cache block is *Exclusive* (step 11).

Figure 3.15  $mc^2RFiat$  operation on the target core i for memory reads

Figure 3.16 Coherent Read Transaction in  $mc^2RFiat$  on the target core i

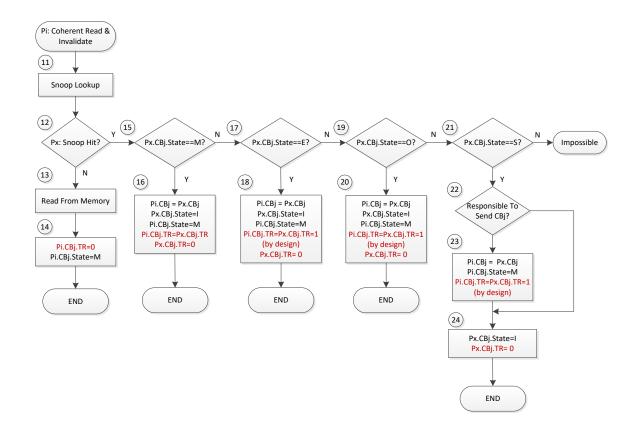

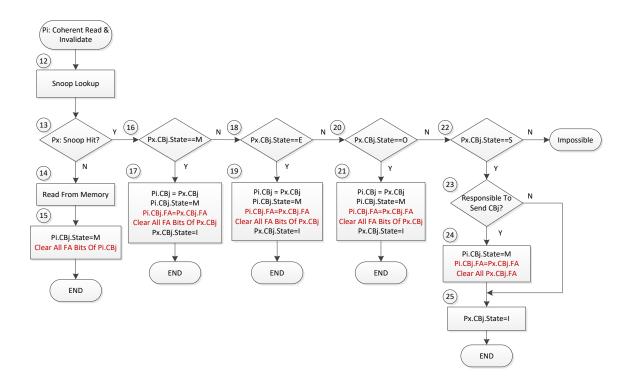

Figure 3.17, Figure 3.18, and Figure 3.19 describes the operation of  $mc^2RFiat$  for memory writes on the target platform by core i. A data cache lookup performed for the requested cache block. In case of a cache hit in the Exclusive state, the state of the cache block is upgraded to the Modified state (step 7). If the requested cache block is in the Owned or Shared state, a Coherent Invalidate transaction (Figure 3.19) is initiated. A snoop lookup is performed by all other caches. If the cache block is hit in the Shared or Owned state, then the cache block is invalidated and the FA bits are cleared. The state of the cache block in Pi is updated to Modified (state 29 and step 31). If the requested cache block is not found in processor Pi, then a Coherent Expression Pi is initiated. The sequence of

events performed by other caches in response to a *Coherent Read and Invalidate* transaction is described as follows:

- If the snoop request finds the requested block in the *Modified* state, it is transferred to *Pi* along with its *FA* bits. The new state for the *Pi* cache block is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The *FA* bits for the invalidated cache block are cleared (step 17).

- If the snoop request finds the requested block in the *Exclusive* state, it is transferred to *Pi* along with its *FA* bits. The new state for the *Pi* cache block is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The *FA* bits for the invalidated cache block are cleared (step 19).

- If the snoop request finds the requested block in the *Owned* state, it is transferred to *Pi* along with its *FA* bits. The new state for a cache block in *Pi* cache is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The *FA* bits for the invalidated cache block are cleared (step 21).

- If the snoop request finds the requested block in the *Shared* state, it is transferred to *Pi* along with its *FA* bits. The new state for the cache block in *Pi* cache is *Modified* and the state of the cache block in *Px* is updated to *Invalid*. The *FA* bits for the invalidated cache block are cleared (steps 24 and 25).

• If the requested cache block is not found in any processor cache, then it is retrieved from main memory and the corresponding *FA* bits are cleared. The new state of the cache block is set to *Modified* (step 16).

If the current memory write operation writes the entire sub-block protected by FA corresponding FA bits are set.

Figure 3.17  $mc^2RFiat$  operation on the target core i for memory writes

Figure 3.18 Coherent Read and Invalidate in  $mc^2RFiat$  on the target core i

Figure 3.19 Coherent Invalidate in  $mc^2RFiat$  on the target core i

Figure 3.20 describes steps carried out by the software debugger in response to memory reads and memory writes in a steady state. To replay the program offline, the software debugger relies on an instruction set simulator (ISS) of the target platform that uses software models of data caches, first access hit counters (*Pi.fahCnt*), the program binary, the exception traces, and the  $mc^2RFiat$  trace messages received from the target platform. The software debugger reads and decodes trace messages while replaying the program. The formats of the trace messages and the lengths of the fields are known to the software debugger. The software copies of data caches and *Pi.fahCnt* are updated during the program replay using the same updating policies employed on the target platform. The debugger replays the instructions for each core using the corresponding ISS. For each memory read operation, Pi.fahCnt value is decremented by 1. If *Pi.fahCnt>*0 and if the data is found in the software copy of the data cache of the processor Pi with the corresponding FA bit(s) set, the debugger retrieves the data values from the software copy of the data cache for that processor and moves to replay the next instruction. If the corresponding FA bits are not set, it implies that there is an error in tracing (step 8 in Figure 3.20a). If *Pi.fahCnt>*0 but data is not found in the software copy of the data cache of processor Pi, then the software debugger gets data from another processors data cache. If Pi.fahCnt=0, we have a first read miss event: the load data value is retrieved from the current trace message, the software copy of the data cache is updated and the corresponding FA bits are set. Then, a new trace message from the trace buffer is read for that core and Pi.fahCnt is updated with a new value extracted from the trace message (step 3 in Figure 3.20a). For each memory write operation, if the data is found in the software copy of the data cache and the cache block is shared, the current cache acquires the ownership by invalidating copies of the cache block in other caches and then software copy of cache block is updated. If the data is a hit in another cache, the *FA* bits are also copied along with the cache block. In the case of a cache miss event, *FA* bits for the corresponding block are cleared. If the current memory write operation writes the entire sub-block protected by a single FA bit, corresponding FA bits are set (step 5 in Figure 3.20b).

Figure 3.20  $mc^2RFiat$  operation in the software debugger on core i for a) memory reads, and b) memory writes

# CHAPTER 4

#### EXPERIMENTAL EVALUATION

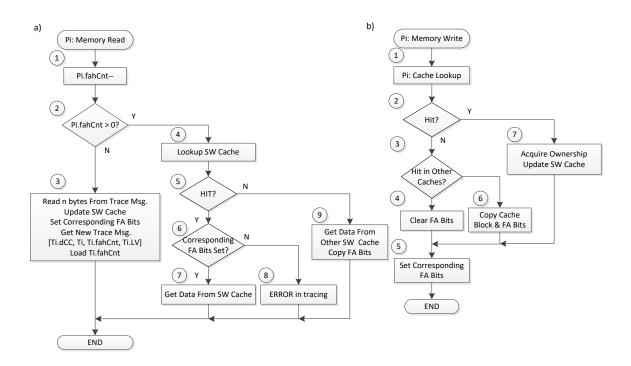

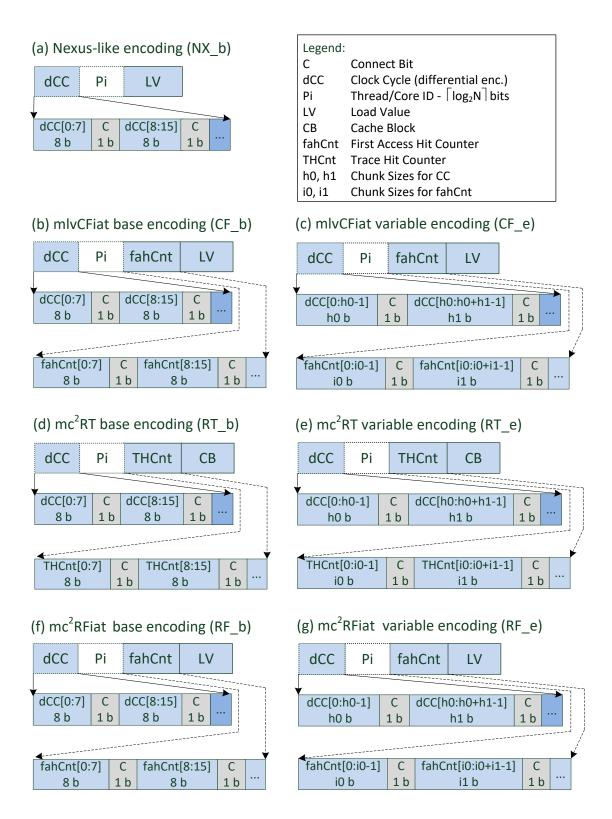

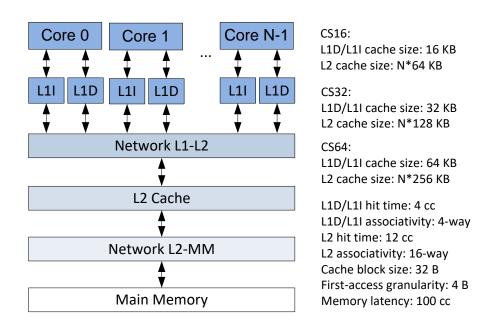

This chapter discusses the experimental setup used for the evaluation of the proposed techniques. Figure 4.1 describes the experimental flow used to create hardware traces and to analyze the trace port bandwidth requirements. The experimental flow include three major components (i) software timed trace generator, (ii) mlvCFiat,  $mc^2RT$ , and  $mc^2RFiat$  simulators to filter the load data value traces, and (iii) software to hardware trace converters and encoders. Section 4.1 discusses the TmTrace tool used to create timed software traces and their output format. Section 4.2 discusses the implementation and verification details of the mlvCFiat simulator. Section 4.3 discusses the implementation and verification details of the  $mc^2RT$  simulator. Section 4.4 discusses the implementation and verification details of the  $mc^2RFiat$  simulator. Section 4.5 discusses the conversion of software traces to hardware traces. Finally, Section 4.6 discusses the workload used for the trace port bandwidth evaluation and experimental analysis to select a good granularity size and variable encoding parameters.

Figure 4.1 Experiment flow to create hardware traces

# 4.1 Software Timed Trace Generator

TmTrace [28] (Timed Multithreaded Trace) is a software module developed as an extension of the Multi2Sim simulator [37] that was used to create timed software traces. This tool provides different options for collecting traces of interest. For example, we can collect control flow traces for all committed instructions, data traces for memory reads and/or memory writes. In this case, we use this tool to collect traces for all memory read and memory write operations. We refer to these traces as tmlsTraces. The format of these traces is shown in Figure 4.2. Each trace message includes the following fields:

- CC: Clock cycle in which the memory instruction is committed;

- Pi: Thread id or processor core id;

- L/S: Memory read (L=0) or write (S=1) instruction;

- PC: Value of the program counter or address of the instruction;

- OA: Address of the operand;

- OS: Size of the operand;

- LV: Value of the operand read from memory. This field is empty for a memory write operation.

Figure 4.2 Trace messages generated for memory reads and writes

## 4.2 *mlvCFiat* Simulator

mlvCFiat simulator takes tmlsTraces as an input, implements the mlvCFiat trace filtering as described in Section 3.1, and outputs the compressed load data value traces. The mlvCFiat simulator maintains the mlvCFiat structures (Figure 3.6) private to each processor core. Section 4.2.1 discusses the main implementation details of the mlvCFiat simulator, and Section 4.2.2 describes the test cases used to confirm its correctness.

Table 4.1 describes the parameters that can be used to control the behavior of the *mlvCFiat* simulator. With the help of these parameters, we can control output file size, size of the data caches, the size of the sub-block protected by a single first-

access bit, and output file name. Figure 4.3 shows the output format of the mlvCFiat trace message. It includes a time stamp (CC), the thread id (Pi), the first access hit counter (fahCnt), the operand size (OS), the corresponding data cache sub-block(s) that includes the load value (LV), and the length of the LV field (LLV). Note: the length of the LV filed depends on the granularity size and it can be greater than or equal to the length of the actual operand. For example, if the granularity size is 4-bytes and the operand size is 1-byte, the minimum length of the LV field is 4-bytes. The mlvCFiat simulator also outputs the program statistics. An example of a statistics file is given in Figure 4.4. It includes information about the number of memory read and memory write operations, cache hits, cache misses, and first-access hits etc.

Table 4.1 *mlvCFiat* flags

| Parameter          | Description                                                       |

|--------------------|-------------------------------------------------------------------|

| help               | Generates help messages                                           |

| f [size]           | Output file size in MB. If file exceeds the specified size the    |

|                    | tracing stops. Default 50,000 MB.                                 |

| cs [kilobytes]     | Cache size in kilobytes. Default is 32 KB.                        |

| cls [line size]    | Cache line size in bytes. Default is 32 B.                        |

| ca [associativity] | Sets the associativity of the cache. Default is 4.                |

| cfg [granularity]  | First access flag granularity, with each flag protecting a sub-   |

|                    | block of size granularity in a cache line. Default is 4 words (8  |

|                    | bytes).                                                           |

| o [filename]       | Specifies output trace file name. Default is                      |

|                    | tmlvCFiat_out_yr_mon_day_hr_min_sec                               |

|                    | Note: *.txt = descriptors, *.Statistics = Statistics of tmlvCFiat |

Figure 4.3 mlvCFiat trace descriptor format

```

; mlvCFiat: Instrumentation Time 180.608 ms

; timed memory read stats

Recorded 2197 memory read instructions.

211 ( %9.60 ) Byte Operands

11 ( %0.50 ) Word Operands

1971 ( %89.71 ) Doubleword Operands

2 ( %0.09 ) Quadword Operands

2 ( %0.09 ) Extended Precision Operands

0 ( \%0.00 ) Octaword Operands

0 ( %0.00 ) Others Operands

; timed memory write stats

Recorded 2213 memory write instructions.

108 ( %4.88 ) Byte Operands

166 ( %7.50 ) Word Operands

1937 ( %87.53 ) Doubleword Operands

1 ( %0.05 ) Quadword Operands

1 ( %0.05 ) Extended Precision Operands

0 ( \$0.00 ) Octaword Operands

0 ( %0.00 ) Others Operands

; timed memory read flow with CFiat stats

Cache Size (KB): 16

Cache Associativity: 4

Cache Line Size (B): 32

First Access Flag Granularity (B): 4

-- Cache Read References Hits: Misses (Hit Rate)

Total 2080:117(94%)

Byte Operands 177:34(83%)

Word Operands 9:2(81%)

Doubleword Operands 1891:80(95%)

Quadword Operands 1:1(50%)

Extended Precision Operands 2:0(100%)

Octaword Operands 0:0(0%)

Hexaword Operands 0:0(0%)

Other Sized Operands 0:0(0%)

-- Cache References Hits: Misses (Hit Rate)

Total 4172:238(94%)

Byte Operands 282:37(88%)

Word Operands 175:2(98%)

Doubleword Operands 3710:198(94%)

Quadword Operands 2:1(66%)

Extended Precision Operands 3:0(100%)

Octaword Operands 0:0(0%)

Hexaword Operands 0:0(0%)

Other Sized Operands 0:0(0%)

-- First Access Flag References Hits: Misses (Hit Rate)

Total 1829:368(83%)

Byte Operands 143:68(67%)

Word Operands 8:3(72%)

Doubleword Operands 1676:295(85%)

Quadword Operands 1:1(50%)

Extended Precision Operands 1:1(50%)

Octaword Operands 0:0(0%)

Hexaword Operands 0:0(0%)

Other Sized Operands 0:0(0%)

; File size in Binaries

; Type, TotalSizeofTime, TotalSizeofLine, TotalSize

Input Load, 17576, 35152, 52728

Input Store, 17704, 35408, 53112

Input, 35280, 70560, 105840

Output, 2944, 3312, 6256

```

Figure 4.4 mlvCFiat simulator statistics example

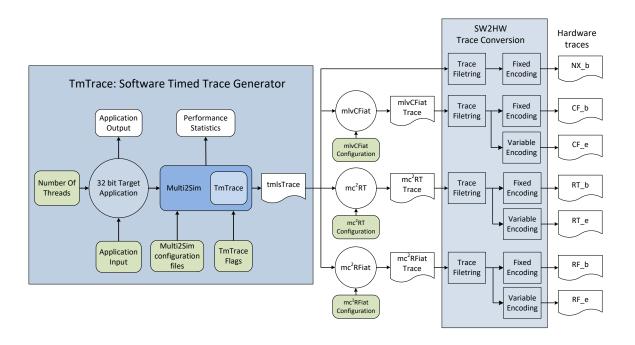

### 4.2.1 Implementation Details

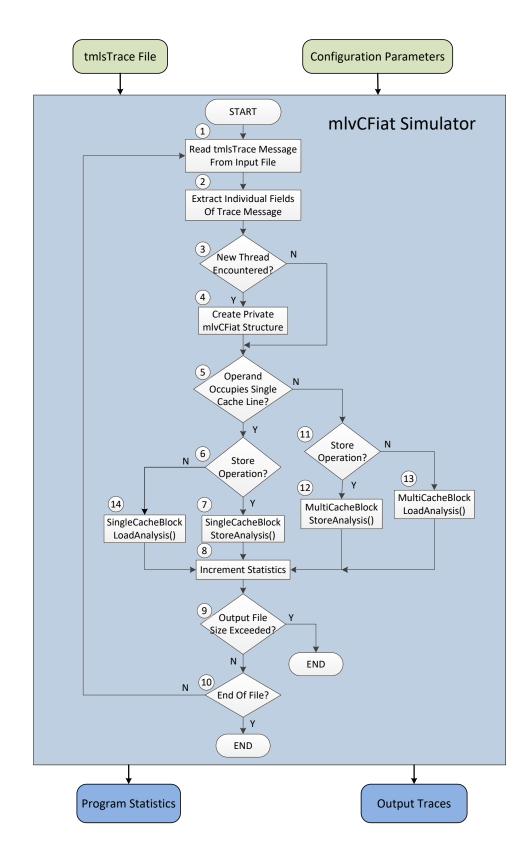

Figure 4.5 shows the functional flow of the *mlvCFiat* simulator. It starts by reading the trace messages from the input file and by extracting the individual fields of the trace message. If the trace message is from a new thread, it creates a new private *mlvCFiat* structure as in Figure 3.2 for the corresponding thread. By using the operand address and the operand size, it decides whether the operand spans single cache block or multiple cache blocks. Depending on the operation and the number of cache blocks occupied by the operand, the following functions are invoked: memory read operation with single cache block invokes the *SingleCacheBlockLoadAnalysis()* function, memory write operation with single cache block invokes the *SingleCache-BlockStoreAnalysis()* function, memory read operation with multiple cache blocks invokes the *MultiCacheBlockLoadAnalysis()* function, and memory write operation with multiple cache blocks invokes the *MultiCacheBlockStoreAnalysis()* function.

SingleCacheBlockLoadAnalysis() checks whether the requested data is found in the cache (cache hit event) or not (cache miss event). For a cache hit event, if all the corresponding FA bits are set, fahCnt is incremented. Even if a single FA bit is not set, it is treated as an FA miss event. For a cache miss event or FA miss event, a trace message for that thread is written to the output file, fahCnt is cleared and the corresponding FA bits are set (Figure 3.3a). To avoid duplication of sub-blocks protected by the FA bit reported by the target platform, mlvCFiat emits the trace message with the missing sub-blocks instead of all the sub-blocks corresponding to the requested data.

SingleCacheBlockStoreAnalysis()checks whether the requested data is found in the cache (cache hit event) or not (cache miss event). For a cache miss event, a new

cache block is fetched and the *FA* bits for newly fetched cache block are cleared. For a *cache hit event*, the current processor acquires ownership by invalidating data in other processor caches. If the current write operation writes the entire sub-block protected by an *FA* bit, the corresponding *FA* bit is set (Figure 3.3b).

If the operand spans multiple cache blocks, each cache block is treated as an independent single cache block and operations are carried out as in SingleCache-BlockStoreAnalysis() and SingleCacheBlockLoadAnalysis(). If the data is found partially in the cache (some cache blocks are hit and some cache blocks are miss), it is treated as a  $cache\ miss\ event$ . Statistics related to caches (cache hit or cache miss, first access bits are hit or miss etc.), instructions (number of memory reads and memory writes), and operands (byte, word, double word etc.) are incremented. These steps are repeated until the output file exceeds the allocated size or the input file reaches its end.

Figure 4.5 mlvCFiat simulator functional flow

#### 4.2.2 Verification Details