# CPE 626 CPU Resources: Multipliers

Aleksandar Milenkovic E-mail: milenka@ece.uah.edu Web: http://www.ece.uah.edu/-

-milenka

#### Outline

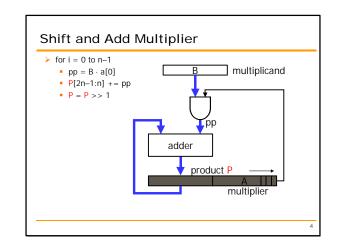

- Unsigned Multiplication

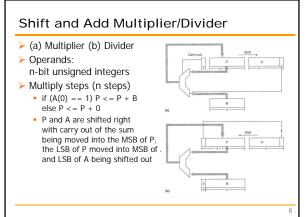

- Shift and And Multiplier/Divider

- Speeding Up Multiplication

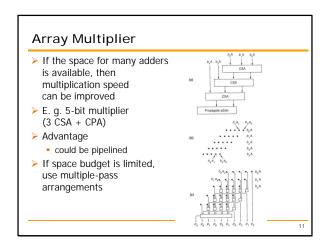

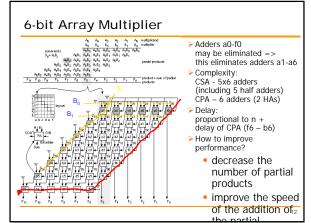

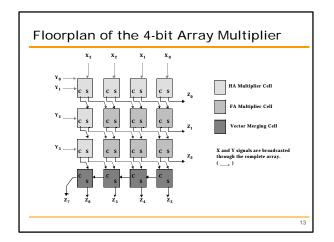

- Array Multiplier

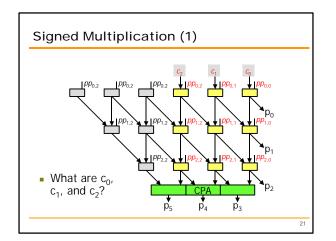

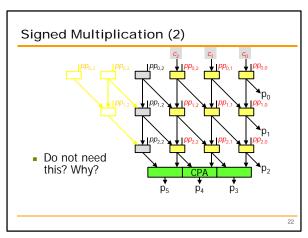

- Signed Multiplication

- Booth Encoding

- ➢ Wallace-tree

| 0 1  | 011101 multiplicand (29)<br>101011 multiplier (43)<br>011101 ← partial product<br>011101 ← • product = 0<br>00000 ← • for i = 0 to n-1<br>- compute partial product<br>(AND operation)<br>01 ← • left-shift partial product by i<br>- product += partial product |   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1001 | I <b>1 0 1 1 1 1 1 ←</b> product                                                                                                                                                                                                                                 | 3 |

| > Operands (a/b):                              | P<br>00000 | A<br>1110 | Divide 14 = 1110, by 3 = 11, B always contains 0011,                          |

|------------------------------------------------|------------|-----------|-------------------------------------------------------------------------------|

|                                                | 00001      | 110       | step 10); shift.                                                              |

| n-bit unsigned integers                        | -00011     |           | step 1(i): subtract.                                                          |

| put a in register A                            | -00010     | 1100      | step 1(iii): result is negative, set quotient bit to 0.                       |

|                                                | 00001      | 1100      | step 1(iv): restore.                                                          |

| put b in register B                            | 00011      | 100       | step 2(i): shift.                                                             |

| put 0 in register P                            | -00011     |           | step 2(i): subtract.                                                          |

| 1 5                                            | 00000      | 1001      | step 2(ii): result is nonnegative, set quotient bit to 1.<br>step 3(): shift. |

| Divide steps (n steps)                         | -00011     | 001       | step 30); subtract.                                                           |

|                                                | -00010     | 0010      | step 3000 result is negative, set quotient bit to 0.                          |

| <ul> <li>Shift (P, A) register pair</li> </ul> | 00001      | 0010      | step 3(iv): restore.                                                          |

| one bit left                                   | 00010      | 010       | step 4(i): shift.                                                             |

| P <= P - B                                     | -00011     |           | step 4(ii): subtract.                                                         |

|                                                | -00001     | 0100      | step 4(iii): result is negative, set quotient bit to 0.                       |

| <ul> <li>if result is negative,</li> </ul>     | 00010      | 0100      | step 4(iv): restore. The quotient is 01002 and the remainder is 0001          |

| set the low order bit of A to                  | 0,         |           |                                                                               |

| otherwise to 1                                 |            |           |                                                                               |

| If the result of step 2 is neg                 | ative      |           |                                                                               |

| restore the old value of P by                  |            |           |                                                                               |

|                                                |            |           |                                                                               |

| adding the contents of B ba                    | ck to P    |           |                                                                               |

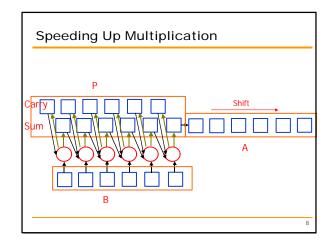

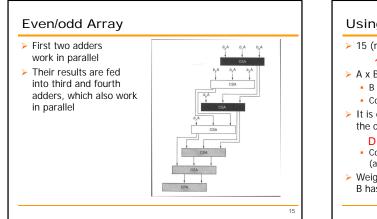

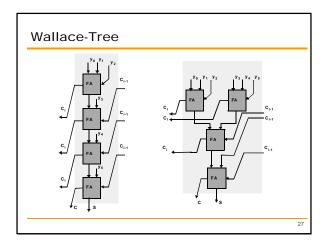

#### Speeding Up Multiplication (cont'd)

- Reduce the amount of computation  $\geq$

- in each step by using carry-save adders (CSA)

- ۶ CSA is simply collection of n independent full adders

- Each addition operation results in a pair of bits, stored in the sum and carry parts of P

- > At each step, only the LSB bit of the sum needs to be shifted Steps

- load the sum and carry bits of P with zero

perform first addition

shift the LSB sum bit of P into A, as well as A itself Note: (n-1) bit of P do not need to be shifted because on the next cycle the sum bits are fed into the next lower order adder

- Disadvantages

Additional hardware (keep both carry and sum)

- After the last step, the high order word of the result must be fed into an ordinary adder to combine the sum and carry parts

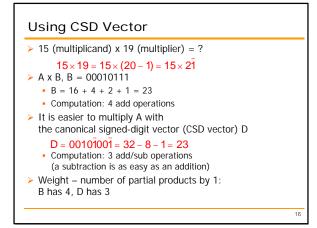

#### **CSD** Vector

> Recode (or encode) any binary number, B, as a CSD vector D  $D_i = B_i + C_i - 2C_{i+1}$  $C_{i+1} = Carry\{B_{i+1} + B_i + C_i\}, C_0 = 0$ B = 011 $B_2 = 0, B_1 = 1, B_0 = 1$  $C_1 = Carry\{1 + 1 + 0\} = 1, D_0 = 1 + 0 - 2 = \overline{1}$  $C_2 = Carry\{0 + 1 + 1\} = 1, D_1 = 1 + 1 - 2 = 0$  $C_3 = Carry\{0 + 0 + 1\} = 0, D_2 = 0 + 1 - 0 = 1$

## CSD Vector: An Example – Radix = 2

- > B = 101001, n = 5 B = 1+8-32 = -23 B =  $(0-B_0) \cdot 2^0 + (B_0 - B_1) \cdot 2^1 + (B_1 - B_2) \cdot 2^2 + (B_2 - B_3) \cdot 2^3$

- $+ (B_3 B_4) \cdot 2^4 + (B_4 B_5) \cdot 2^5$ = (-1) + 2 + 0 + (-8) + 16 + (-32) = -23

- = (-1) + 2 + 0 + (-0) + 10 + (-32) = -23

- $E = \bar{1}1\bar{1}01\bar{1} = (-1) \cdot 2^5 + 1 \cdot 2^4 + (-1) \cdot 2^3 + 1 \cdot 2^1 + (-1) \cdot 2^0$

- = -32 + 16 8 + 2 1 = -23 ➤ To multiply by B

- encode it as a radix-2 signed digit E

- Multiply by 2 (a shift) + 6 (n+1) add/subtract operations

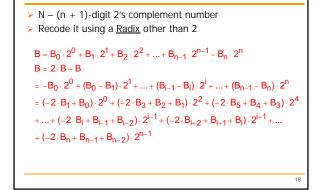

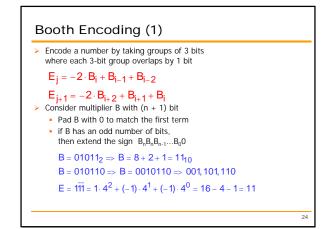

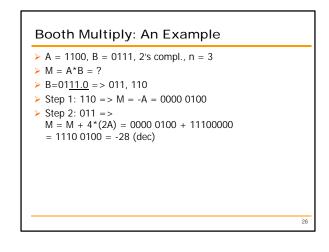

# CSD Vector: An Example - Radix=4

- ▶ B = 101001, n = 5

- B = 1 + 8 32 = -23

- $$\begin{split} &\mathsf{B} = (-2 \cdot \mathsf{B}_1 + \mathsf{B}_0) \cdot 2^0 + (-2 \cdot \mathsf{B}_3 + \mathsf{B}_2 + \mathsf{B}_1) \cdot 2^2 + (-2 \cdot \mathsf{B}_5 + \mathsf{B}_4 + \mathsf{B}_3) \cdot 2^4 \\ &= (2 \cdot 0 + 1) \cdot 2^0 + (-2 \cdot 1 + 0 + 0) \cdot 2^2 + (-2 \cdot 1 + 0 + 1) \cdot 2^4 \end{split}$$

- = 1-8-16 = -23

```

\mathsf{E} = 1\overline{21} = 1 \cdot 4^0 + (-2) \cdot 4^1 + (-1) \cdot 4^2

```

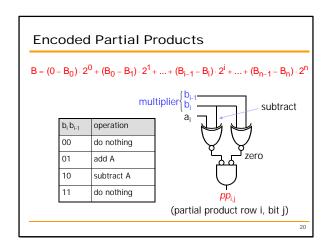

#### = 1- 8 - 16 = -23 ➤ To multiply by B

- encode it as a radix-4 signed digit E

- Multiply by 4 (a shift by 2) + 3 add/subtract operation

23

| B | B <sub>i-1</sub> | B <sub>i-2</sub> | Operation |  |

|---|------------------|------------------|-----------|--|

| 0 | 0                | 0                | 0         |  |

| 0 | 0                | 1                | 1         |  |

| 0 | 1                | 0                | 1         |  |

| 0 | 1                | 1                | 2         |  |

| 1 | 0                | 0                | -2        |  |

| 1 | 0                | 1                | -1        |  |

| 1 | 1                | 0                | -1        |  |

| 1 | 1                | 1                | 0         |  |

> Control settings for the Nth cycle of the multiplication

> Use existing shifter and ALU + additional hardware dedicated two-bits-per-cycle shift register for the multiplier and a few gates for the Booth's algorithm control logic (overhead is a few per cent on the area of ARM core)

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                |                       |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---|

| $\begin{array}{ccccc} x & 2 & LSL \#(2N+1) & A-B & 1 \\ x & 3 & LSL \#2N & A-B & 1 \\ 1 & x & 0 & LSL \#2N & A+B & 0 \\ x & 1 & LSL \#(2N+1) & A+B & 0 \end{array}$ |                       | 0 |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                               | x 1 LSL#2N A+B        | 0 |

| 1 x 0 LSL #2N A+B 0<br>x 1 LSL #(2N+1) A+B 0                                                                                                                        | x 2 LSL #(2N+1) A – B | 1 |

| x 1 LSL #(2N+1) A+B 0                                                                                                                                               | x 3 LSL#2N A-B        | 1 |

|                                                                                                                                                                     | 1 x 0 LSL#2N A+B      | 0 |

| x 2 LSL #2N A – B 1                                                                                                                                                 | x 1 LSL #(2N+1) A+B   | 0 |

|                                                                                                                                                                     | x 2 LSL#2N A-B        | 1 |

| x 3 LSL #2N A+0 1                                                                                                                                                   | x 3 LSL #2N A+0       | 1 |

|                                                                                                                                                                     |                       |   |

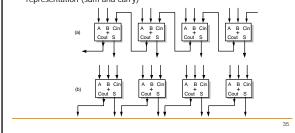

## Carry-propagate (a) and carry-save (b) adder structures

- Carry propagate adder takes two conventional (irredundant) binary numbers as inputs and produces a binary sum

- Carry save adder takes one binary and one redundant (partial sum and > partial carry) input and produces a sum in redundant binary representation (sum and carry)

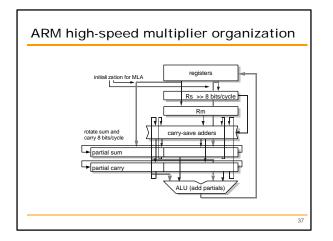

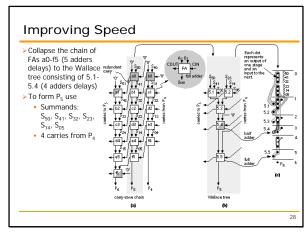

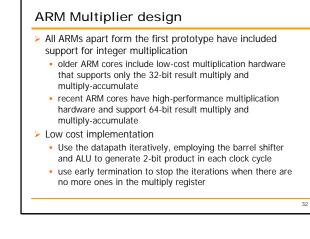

# ARM high-speed multiplier organization

> CSA has 4 layers of adders each handling 2 multiplier bits => multiply 8-bits per clock cycle

36

- > Partial sum and carry are cleared at the beginning or initialized to accumulate a value

- Multiplier is shifted right 8-bits

- per cycle in the 'Rs' register

- Carry sum and carry are rotated right 8 bits per cycle Performance: up to 4 clock cycles (early termination is possible)

- Complexity: 160 bits in shift registers, 128 bits of carry-save adder logic (up to 10% of simpler cores)